写在前面

本文主要翻译自Xilinx白皮书《WP312,Xilinx Next Generation 28 nm FPGA Technology Overview》,蓝色字体部分是我的理解。

这篇文章主要是从半导体工艺的角度来“吹”28nm FPGA(即7系列FPGA)的优点,涉及得到半导体工艺名词较多,由于我并不了解具体的半导体工艺,所以某些名字的翻译可能有误,如有误请指出,感谢!

概述

Xilinx 选择了28nm HKMG高性能、低功耗工艺技术,并将其与新的统一 ASMBL™ 架构相结合,打造出具有更低功耗和更高性能的新一代 FPGA 和 All Programmable SoC。这些器件实现了前所未有的集成度和带宽水平,并为系统架构师和设计人员提供了完全可编程的 ASSP 和 ASIC 替代方案。

Xilinx 的28nm 技术架构的创新:

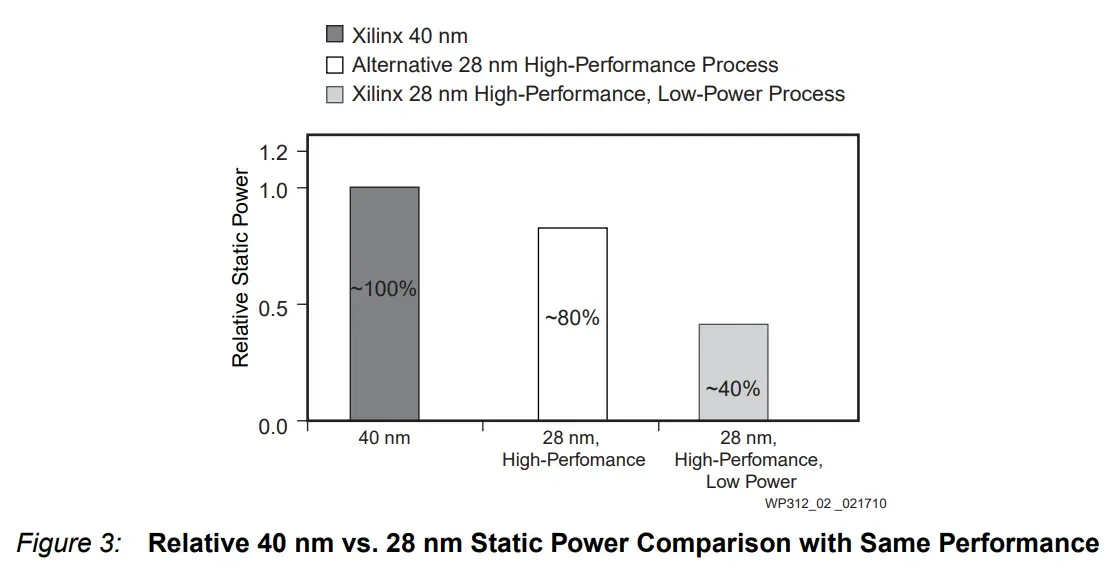

- 与其他 28 nm 高性能方案相比,静态功耗降低高达 50%

- 与上一代 FPGA 相比,系统级性能提升高达 50%

- 与上一代 FPGA 相比,容量增加 2 倍,总功耗降低高达 50%

本白皮书描述了半导体行业在满足市场需求方面面临的挑战, 并描述了如何使用正确的 28nm 工艺技术解决这些挑战。高性能、低功耗工艺与架构创新的突破性结合使新型28 nm FPGA 和 All Programmable SoC 非常适合功耗敏感型应用、 带宽密集型和超高端应用。

HKMG:半导体制程工艺技术, HK是HighK的缩写(高介电常数), MG是Metal Gate的缩写,也就是金属栅极。

ASMBL:是Xilinx面向应用的组合模块架构,核心是一个硅硬件子系统模块化框架,该架构支持一种新的FPGA开发方法,从而可快速、经济地推出针对不同应用领域的FPGA平台。

ASSP: Application Specific Standard Parts,专用标准产品,是为在特殊应用中使用而设计的集成电路。

ASIC:Application Specific Integrated Circuit,即专用集成电路,是指应特定用户要求和特定电子系统的需要而设计、制造的集成电路。

其实28nm工艺的FPGA就是我们平常所熟知的7系列FPGA,根据内部硬件资源的不同,可分为4个系列:S7、A7、K7、V7。

是在上一代45nm工艺基础上发展而来的产品,即S6系列:

以及高端的20nm、UltraSCALE架构产品:

和更高端的16nm、UltraSCALE+架构产品:

技术挑战和经济性挑战:降低静态功耗以提高可用性能并降低系统功耗

由于包含多个集成电路 (IC) 系统的盛行,其导致功耗不断上升的现象成为一个广为关注的问题。除了环境问题外,功耗还会增加构建和操作系统的成本。去除多余的热量需要使用复杂的散热器、风扇和更多的稳压器,所有这些都会增加投资成本 (capital expenditures,CAPEX)。运营成本 (Operating expense,OPEX) 随总功耗增加而增加,包括驱动设备的功率和冷却所需的额外功率。此外,过热系统会导致可靠性降低、系统停机时间增加和运营费用增加。

摩尔定律仍然有效。每一代新的半导体工艺技术都提供了更高的集成度和更低的成本。 然而,这些好处被静态功耗的增加所抵消,伴随着特征尺寸的每次减小,静态功耗的增加似乎不可避免。这种影响对于可编程逻辑行业尤为严重,可编程逻辑行业传统上引领半导体行业,采用最先进的工艺技术,为客户提供更高水平的性能和容量。因此, 系统设计人员发现他们利用更高密度和电路速度的能力受到功耗的限制。启用下一代系统的关键是为设计人员提供更高的“可用性能”,这被定义为在可用功率预算内可能的数据处理能力。降低静态功耗可以为动态功率留出更多的功率预算空间, 从而获得更多可用的性能。这为单个 FPGA 提供了更高带宽的接口和和更多的逻辑、存储器、DSP 和其他高级功能资源。

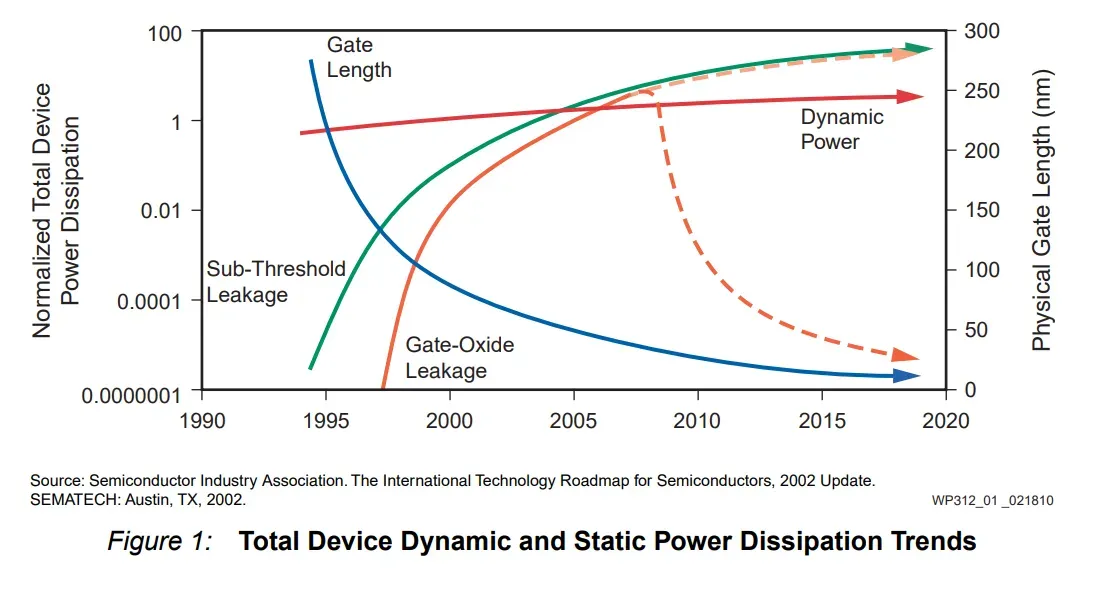

可编程逻辑设计的主要挑战是管理动态功耗和静态功耗(漏电流)的增加,这是对性能没有贡献的开销。不幸的是,更精细的工艺几何形状导致静态功耗增加。事实上,在某些情况下,静态功耗实际上超过动态功耗。参见图 1。

在 28nm 工艺节点之前,业界试图通过降低电源电压和多个晶体管阈值电压(multiple transistor threshold voltages)来解决功耗增加的问题,并取得了一些成功。但是 28nm 工艺需要一种新方法。

为应对 28nm 可用性能挑战,Xilinx与技术和制造合作伙伴台积电 (TSMC) 合作, 为 FPGA 和 All Programmable SoC 开发了 HKMG、高性能低功耗的 28nm 工艺技术。这种新的 28nm 工艺技术建立在 40nm FPGA工艺开发成果的基础上,并引入了新的HKMG 技术,通过降低功耗最大限度地提高可用系统性能。

Xilinx 做出的这项技术选择虽然在业内独一无二,但也已被其他领先的 IC 供应商所接受,因为与其他替代工艺技术相比,它显着降低了静态功耗。在 28nm 工艺节点,静态功耗通常是器件总功耗中的很大部分。因此,要实现最大功率效率,工艺技术的选择是关键。

28nm 工艺静态功耗的显着降低为有效功耗(active power)、动态功耗留出了更多的系统功耗预算,从而实现了更高水平的集成和性能。这使设计人员能够灵活地以较低的功率实现产品,或者创建在相同功率预算内增加容量和性能的产品。

最佳 28nm FPGA 工艺技术:HKMG——高性能、低功耗

传统的 FPGA 工艺技术在 28nm 几何尺寸下已达到其功率极限,因此也达到了其性能极限。问题的根源在于多晶硅栅(polysilicon gate)和氮氧化硅栅极电介质 (ilicon oxynitride gate dielectric,Poly/SiON) 堆栈,几十年来一直用于在 IC 中构建晶体管。

为了制造更快的晶体管,随着工艺几何形状逐渐变小,半导体工程师不断减小栅极介电层(gate dielectric layer)的厚度。但是,由于穿过介电层的隧穿效应(tunneling)和栅极本身下方的漏电流,这种减小了的介电厚度导致了更高的漏电流。随着工艺几何结构中每个节点的增强,这些效应会显着增加静态功耗。

Xilinx 从 90nm 开始一直到 40nm 技术节点,通过创新的三重门极氧化层(triple oxide)电路技术成功地管理了隧穿电流效应(tunneling effects)。然而,在 28nm 节点,栅极氧化层太薄了,隧穿效应必须通过新的栅极材料和架构来解决。为了控制栅极下的漏电流(亚阈值漏电流),Xilinx 工程师在整体晶体管设计中进行了谨慎的权衡。

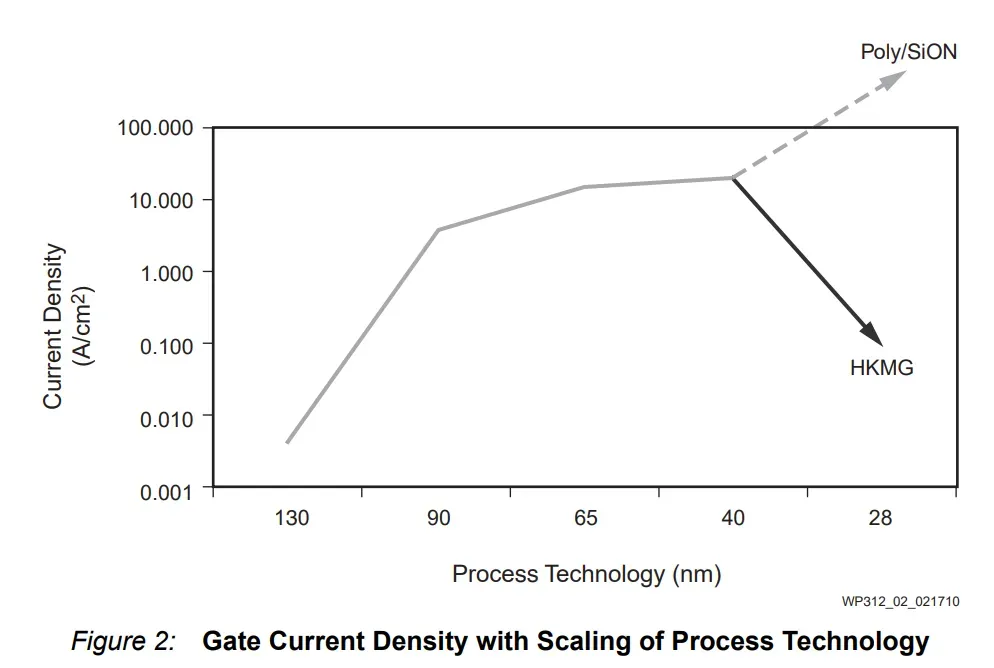

为了解决 28nm 的这些问题,Xilinx 采用了一种名为二氧化铪(hafnium dioxide)的新型栅极电介质材料。这种材料具有高介电常数 (κ),可以增加栅极厚度;因此晶体管更难受隧穿电流效应的影响。例如,40nm工艺中使用的二氧化硅κ值为3.9,而28nm金属栅技术中使用的二氧化铪值κ为25,因此成为高性能低功耗的28nm工艺的最佳选择。如图 2 所示。

在选择 28nm HKMG 高性能和低功耗工艺技术之前,赛灵思评估了多种 28nm 技术选项,包括标准低功耗 (LP) 和高性能 (HP) 变体。

28nm LP 变体通过使用 Poly/SiON 40nm 方法的简单演变来降低风险。不幸的是,由于它较低的晶体管开关速度和低性能,使得其并不适用于 FPGA。相比之下,28 nm HP 技术针对高性能进行了调整,但遗憾的是也会导致更高的功耗,从而限制了可用性能。参见图 3。

28 nm HP 变体工艺还需要将 HKMG 与硅锗 (SiGe) 应变技术(silicon germanium strain technique)相结合。与采用 HKMG 和应力衬垫应变技术(stress-liner strain technology.)的更简单的 28nm 高性能、低功耗方法相比,这种在制造过程中集成了两种先进技术的工艺会带来更多风险。

在经过广泛的合作工艺选择评估后,除了与 40 nm 行业领导者联华电子(UMC)的合作伙伴关系外,赛灵思还与 28 nm行业领先的硅晶圆代工厂(silicon foundry)台积电建立了合作伙伴关系。 台积电是 Xilinx 下一代 FPGA 和 All Programmable SoC 要求的最佳选择,其技术经过优化以实现性能和能效的平衡,以满足确切的产品要求。 Xilinx 28nm 方法与其成熟的代工战略一致,可实现快速上市和技术领先,同时通过地域多元化(geographical diversification)降低供应风险。

polysilicon gate:多晶硅栅,多晶硅栅的形成是集成电路工艺中最关键的步骤,因为它包括了最薄的栅氧化层的热生长(干氧和湿氧),形成多晶硅栅的先进且复杂的光刻技术和干法刻蚀技术,以及需要精确控制且复杂的侧墙工艺。

silicon oxynitride:氮氧化硅,常用作半导体工艺材料。

gate dielectric:栅极电介质是一种在栅电极和晶体管沟道区之间的绝缘层,在工作时,栅极处的电压会在沟道区中形成电场,从而切断电流。

gate-oxide:栅极氧化层,电子结构。

矛盾的解决:以低功耗实现高性能

FPGA 旨在满足广泛市场的各种应用需求:汽车、广播、消费、工业、医疗、测试和测量、视频、有线通信和无线通信等。 Xilinx 28 nm FPGA 和 SoC 产品是在这些市场中数百名客户的帮助下发展的。目标是将功耗降低 50%,并将系统性能提高 50% 或更多。

为成功应对不断增长的系统性能需求带来的挑战,Xilinx 与客户密切合作,确定并了解他们系统中的架构瓶颈。几乎普遍地,外部接口瓶颈被发现是达到所需性能水平的主要障碍。为了实现客户所需的高接口速度,低延迟和改进的噪声容限(noise margin)被确定为关键因素。

为了解决 28 nm 的接口性能问题,赛灵思在时钟技术方面取得了重大进展,并选择强化关键数据路径组件。其结果是外部存储器接口的显着改进,可以将整体系统性能提高 50% 以上。

在许多高性能微处理器中,最重要的设计特性是原始核心速度(raw core speed)。相比之下,FPGA 结构可以以相对适中的切换速率执行高性能数据处理;设计人员可以利用 FPGA 架构中固有的并行性来创建宽数据路径,时钟以输入和输出线速率的一小部分运行。通过将设备容量提高 2 倍,28nm 技术可实现更多流水线和并行处理,从而进一步提高核心性能。这类似于微处理器向多核设计发展的趋势,每个内核以较低的频率运行,但提供比单个“热”核更多的综合性能。

结合时钟方面的创新和有助于更高效地在片内和片外移动数据的硬化关键数据路径组件,FPGA 内核性能的这些提升提高了整体系统性能。

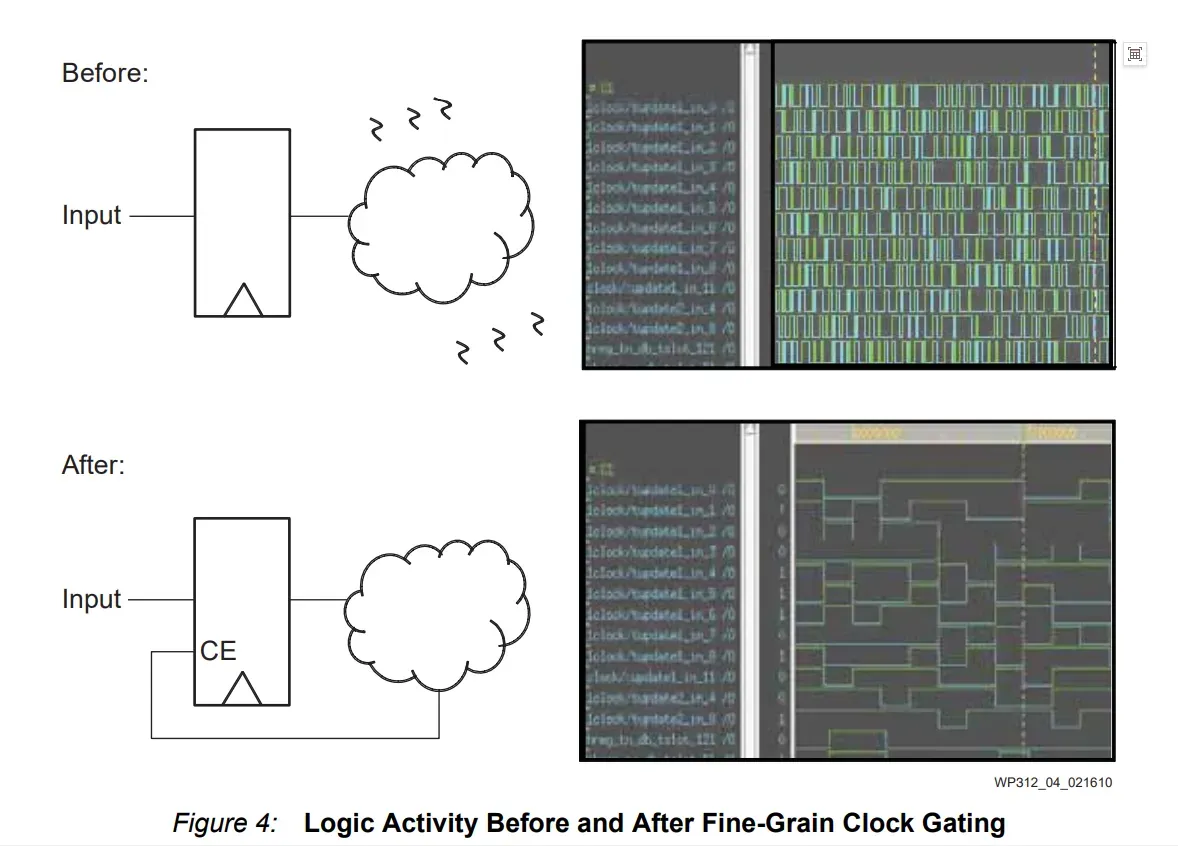

除了最佳的高性能、低功耗工艺技术选择外,28nm FPGA 和 All Programmable SoC 还受益于创新的时钟门控和新的布局布线算法,从而进一步降低功耗。细粒度(Fine-grain)时钟门控技术是一种专利算法,可分析逻辑方程并禁用对最终结果没有贡献的浪费了的逻辑转换。去除了不必要的逻辑活动,平均有效降低了 20% 的功耗。参见图 4。

这些设计方法和工具的进步,再加上第 5 代部分重新配置和新的统一 ASMBL 架构等技术,能够实现更低的功耗和更高的有效密度。

成熟的方法:实现快速上市

多年来,Xilinx 一直使用一种技术开发方法,能够在每个工艺节点快速可靠地引入 FPGA。这种方法论经过二十多年的完善,并在每个技术节点上都得到了成功的证明。

这种方法的关键特征之一是硅测试工具(test vehicle)的智能使用,可在产品流片(tape-out)前显着实现技术准备就绪。对所有领域进行了全面检查,包括设备性能、设计/工艺裕度、片上变化、 制造设计 (DFM)、关键块验证、工艺和生产稳定性、芯片与封装的交互,以及最终的产品可靠性。测试工具最有效是在高价值测试结构和设计/IP 模块与设备和流程就绪里程碑保持一致时, 而不是专注于开发过程中部署的测试工具的绝对数量。

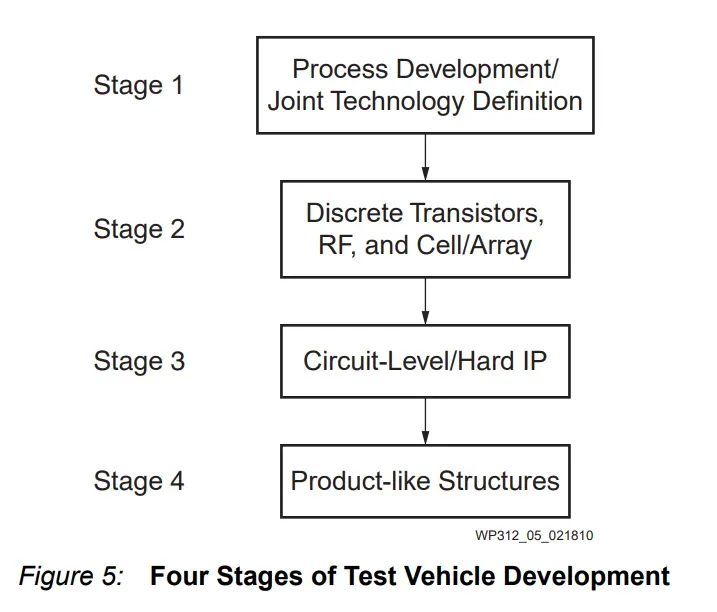

这种经过验证的技术开发方法包括四个阶段。参见图 5。

第 1 阶段从晶圆厂合作伙伴开始,提供特定技术的测试结构,以测试新工艺模块、启用新设备并评估新材料组合。例如,浸没式光刻(immersion lithography)和硅锗 (SiGe) 用于 40nm 和 HKMG 28nm。在第 1 阶段,Xilinx 与代工厂合作定义和调整技术目标。

在晶圆厂合作伙伴测试结构的同时,Xilinx 共同开发了额外的测试工具,使用专用于新一代 Xilinx All Programmable 器件的测试结构来验证器件模型。这使 Xilinx 能 够修改布局和设计规则,并调整仿真模型以实现器件/电路行为的可预测性和可制造性。

在第 2 阶段,Xilinx 创建了额外的测试工具来验证 RF 组件,例如电感器和电容器 (高速收发器所必需的),以及基于单元/阵列的 FPGA 元件结构。

在第 3 阶段,电路级 FPGA 模块(例如BRAM 和配置)和硬核 IP 结构被添加到测试工具中。这些测试可以评估特定 FPGA 模块的宏观功能和性能,包括寄生效应对电路性能的影响。其他结构可以在产品开发的早期表征 ESD 效应。随着时间的推移,不断收集和检查来自这些测试车辆的经验数据,以将设备模型与实际硅相关联。结果是产品在性能和低功耗方面都得到了更好的调整。

第 4 阶段包括之前所有阶段的测试车辆的关键要素,并增加了对代表性产品结构的测试。例如,调试与版图效果相关的随机缺陷的 RAM 还可以表征功能和性能,并允许更早地评估产品可靠性。

在大多数阶段中,Xilinx 都获得了基准测试结构和监控电路 IP 的专利,这些 IP 专为可编程设备量身定制,用于检测、调试和优化过程特性,并微调性能与功耗。

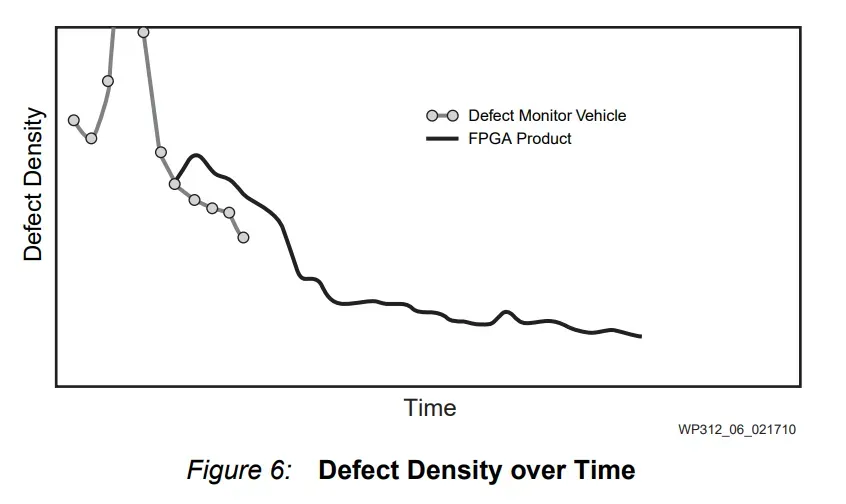

这些监控电路提供了宝贵的见解,帮助代工合作伙伴能够在产品流片前识别并解决潜在的制造问题。这导致更快、更可预测的产量上升。这些专有电路提供了检测精确故障位置的能力,以便快速诊断和解决问题。与统计分析相结合,获得专利的基准测试结构有助于识别突出关键流程边缘的弱点。其他结构经过整体设计,通过允许在整个工艺、电压和温度范围( PVT)内对前端(晶体管级)和 后端(互连/电介质)的性能和功率进行早期分析,来识别工艺和设计角之间的相互作用变化。这些器件中还添加了代表性结构,以进一步调试并将测试工具结构提供的结果与实际 FPGA 器件相关联。参见图 6。

Xilinx 技术开发过程也非常重视高速模拟组件。除了电容器和电感器等基本构建元件外,测试工具中还包含多个 PLL 振荡器和其他电路,以表征收发器的关键元件。 振荡器是收发器的核心,需要对频率稳定性和相位噪声进行早期和全面的表征。边沿速率(edge rate)和回波损耗(return loss)等其他特性也通过与收发器相关的结构完成。测试工具将多个结构彼此靠近放置,并使用完整的后端金属层来识别潜在的耦合效应(coupling effects)以及与相邻振荡器的相互作用。这种接近度至关重要,因为这些器件中具有完整后端金属层的多个结构与仅具有一个后端金属层的单个振荡器具有不同的特性。 这些数据解决了技术开发的早期问题,并使 28nm产品更快准备就绪。

自 2007 年以来,Xilinx 一直在开发其 28nm 工艺技术,使用多个测试平台以确保快速、可靠地推出下一代 All Programmable 设备。

immersion lithography:浸没式光刻,该光刻技术是在传统的光刻技术中,其镜头与光刻胶之间的介质是空气,而所谓浸入式技术是将空气介质换成液体。

coupling effects:耦合效应。

edge rate:电信号的边沿由低到高或由高到低变化的速率,通常以伏特每纳秒为单位。有时(信号幅度恒定且不易混淆时)也指信号的边沿时间。

return loss:回波损耗,又称为反射损耗。是电缆链路由于阻抗不匹配所产生的反射,是一对线自身的反射。

总结

功耗是当前半导体行业,特别是FPGA行业最关心的问题。在Xilinx的28nm系列产品中,Xilinx采用了全新的方法来减少功耗以及提升系统性能。

与上一代FPGA产品相比,28nm高性能低功耗工艺、革新性的架构和设计工具的组合提供了一个整体的提升:

- 打破了静态功率和动态功率增加的历史趋势,使总功率减少一半

- 系统性能增加了50%

- 容量增加了2倍

结果就是28nm 的All Programmable FPGA and SoC的产品线帮助系统架构师和设计人员取得了一个重大的技术突破。这一技术可以使设计人员实现更多应用,包括低功耗应用(例如HDTV(High Definition Television,高清晰度电视),工业控制和车用视听娱乐(automotive infotainment)),带宽敏感性应用和超高端应用(例如通讯设备,高性能计算,软件定义的无线电(software-defined radio)和视频处理)。

-

📣您有任何问题,都可以在评论区和我交流📃!

-

📣本文由 孤独的单刀 原创,首发于CSDN平台🐵,博客主页:wuzhikai.blog.csdn.net

-

📣您的支持是我持续创作的最大动力!如果本文对您有帮助,还请多多点赞👍、评论💬和收藏⭐!

文章出处登录后可见!