前言

- FPGA 内部有大量的逻辑资源,可以实现简单到复杂的工程,但依旧需要基本的输入输出引脚,如时钟引脚,普通的IO引脚

配置IO 引脚

-

这里配置一下LED的引脚与 FPGA的时钟输入引脚,也就是FPGA外部晶振的输入引脚

-

首先需要通过查看原理图,确认FPGA的引脚,以下是我的开发板上的引脚配置

| 引脚 | 引脚编号 | 说明 |

|---|---|---|

| 40MHz 时钟输入 | U27 | 40MHz 时钟输入 |

| LED1 | AF28 | 高电平 亮 |

| LED2 | AE28 | 高电平 亮 |

| LED3 | Y29 | 高电平 亮 |

- 一般FPGA 会有 复位引脚,也就是 RESET引脚,我这个开发板没有找到,可以先随意制定一个没有使用的IO引脚

配置步骤

-

在开发FPGA 的Module (模块)时,会定义输入与输出的网络,类型为:input 、output、 inout类型中的一种,然后定义一个 wire 线的 name,或者 port,引脚配置最终与这些 port 一一对应,如果port没有指定引脚,在生成Bitstream 文件时,Vivado 会报错,提示没有IO约束

-

我当前的引脚定义

module led_flash(

input sys_clk, //FPGA_40MHz

input sys_rst_n,

output reg [2:0] led

);

- 也就是 :sys_clk 对应 FPGA 的晶振时钟输入, sys_rst_n 指定复位引脚,板子没有这个引脚,就随意制定一个不使用的IO,led,3位的,对应板子上的三个LED控制引脚

约束文件指定

- 新建约束文件,Vivado 默认文件扩展名为:

.xdc,在这个文件直接设置引脚即可

set_property CONFIG_VOLTAGE 3.3 [current_design]

set_property CFGBVS VCCO [current_design]

# set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

set_property BITSTREAM.CONFIG.CONFIGRATE 50 [current_design]

set_property BITSTREAM.CONFIG.SPI_32BIT_ADDR YES [current_design]

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

#set_property BITSTREAM.CONFIG.SPI_FALL_EDGE YES [current_design]

set_property PACKAGE_PIN Y29 [get_ports {led[2]}]

set_property PACKAGE_PIN AE28 [get_ports {led[1]}]

set_property PACKAGE_PIN AF28 [get_ports {led[0]}]

set_property PACKAGE_PIN U27 [get_ports sys_clk]

set_property PACKAGE_PIN AH29 [get_ports sys_rst_n]

set_property IOSTANDARD LVCMOS33 [get_ports {led[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports sys_clk]

set_property IOSTANDARD LVCMOS33 [get_ports sys_rst_n]

set_property SLEW SLOW [get_ports {led[2]}]

set_property SLEW SLOW [get_ports {led[1]}]

set_property SLEW SLOW [get_ports {led[0]}]

set_property DRIVE 12 [get_ports {led[2]}]

set_property DRIVE 12 [get_ports {led[1]}]

set_property DRIVE 12 [get_ports {led[0]}]

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

使用 Vivado 图形配置

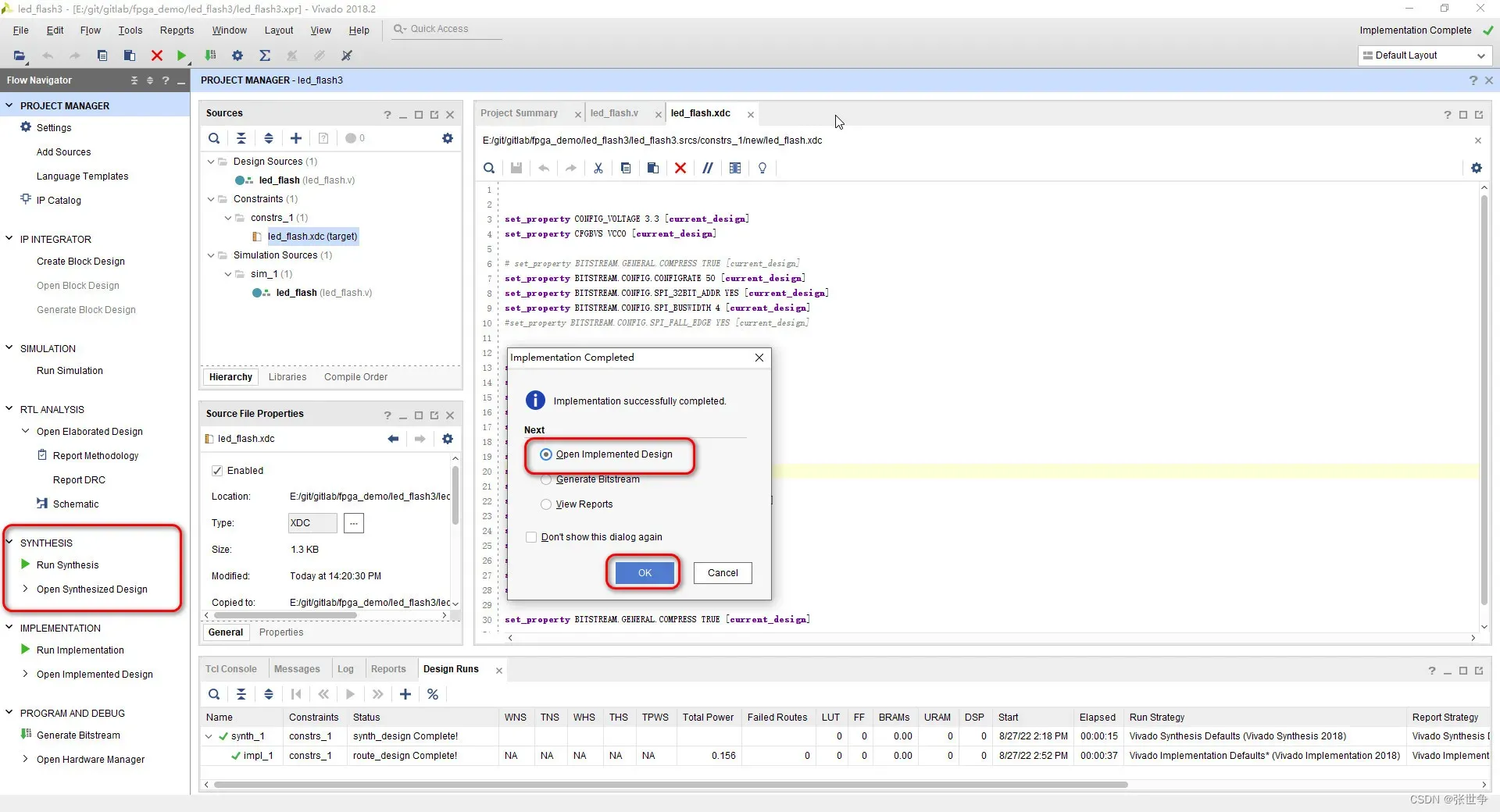

- 需要 完成【实现】,也就是:【Run Implemention】完成后,打开【Open Implemented Design】

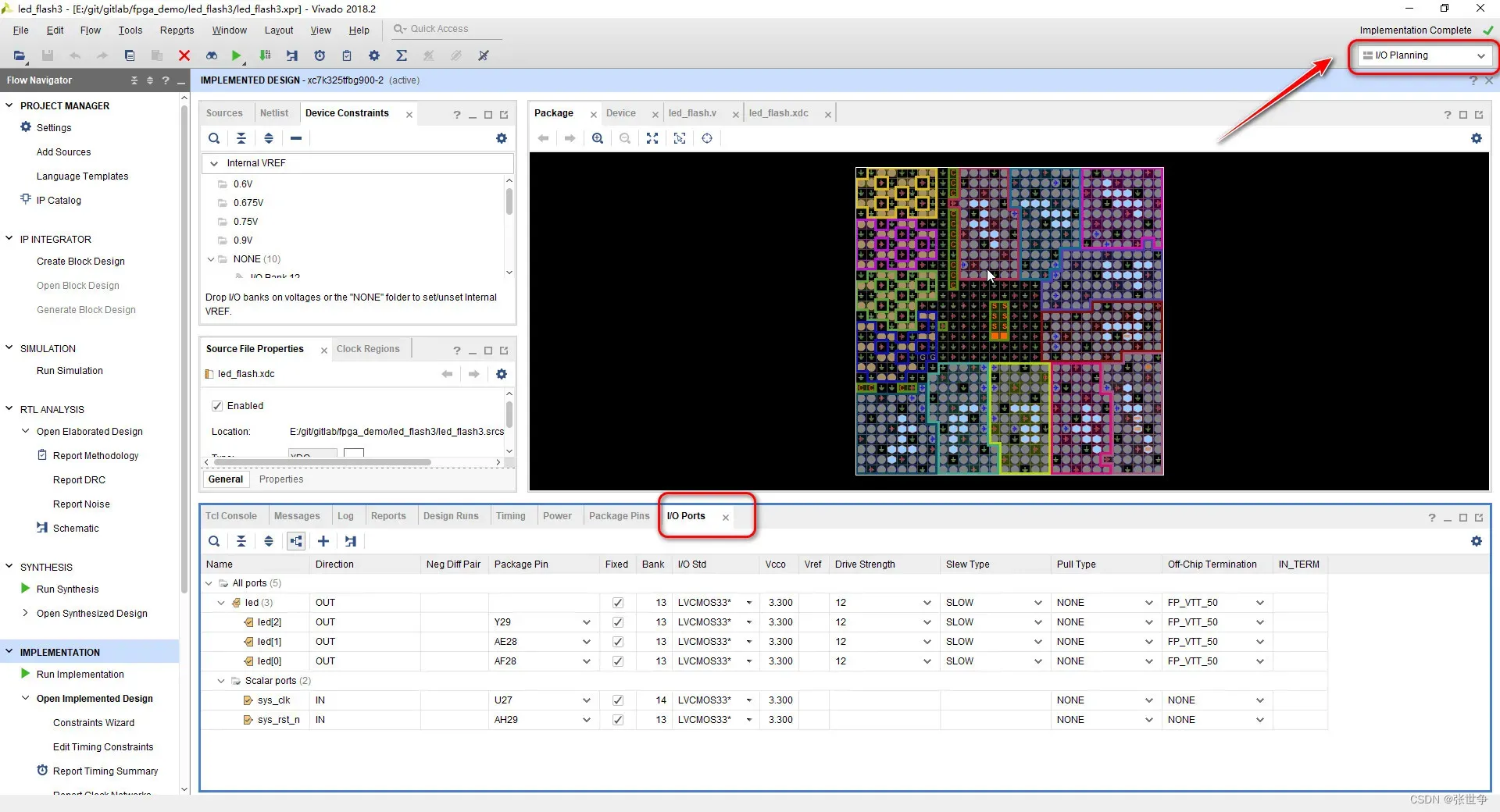

- 右上角有个【I/O Planning】,选择 【I/O Ports】

- 这里可以直接配置引脚,配置完成后,CTRL + S 保存,如果没有约束文件:【Constraints】文件,可以新建,如果已有,可以【覆盖】,也就是 overwrite。这样会更新到 .xdc 约束文件中

功能验证

- 配置引脚后,可以点击【Generate Bitstream】,重新生成 bit文件,下载到 FPGA 运行,确认引脚是否设置正确

小结

-

学习FPGA,方法很多,有的喜欢研究Verilog HDL、VHDL等硬件描述语言,有的喜欢仿真,不断的学习研究【数字逻辑】,有的喜欢工程式的开发,研究各个FPGA平台的使用,不过都需要持续深入的研究,才会有所得

-

需要熟练使用开发工具,如Xilinx 的 Vivado,功能很强大,可以满足初学者的学习要求

文章出处登录后可见!

已经登录?立即刷新