在我们的日常生活中,我们经常会遇到一些“快如闪电”的事物:比如那场突如其来的雨、那个突然出现在你眼前的前任、还有就是今天我们要聊的——固态硬盘(SSD)。

如果你是一个技术宅,或者对速度有着近乎偏执的追求,那么恭喜你,你找到了一个新朋友。这个朋友不仅快,而且非常稳定。他可以让你的游戏加载瞬间完成,让你的工作效率翻倍,甚至让你的电脑启动时间从“泡一杯咖啡”缩短到“打个哈欠”。

但你知道吗?这种神奇的速度背后,隐藏着一个复杂的结构和原理。这就是我们今天要探索的主题——SSD架构原理。我们将深入到它的内部,看看那些小小的闪存颗粒是如何变成我们手中的高速存储设备的。这就像是一次奇妙的探险,我们将一起揭开SSD神秘面纱,一探究竟!

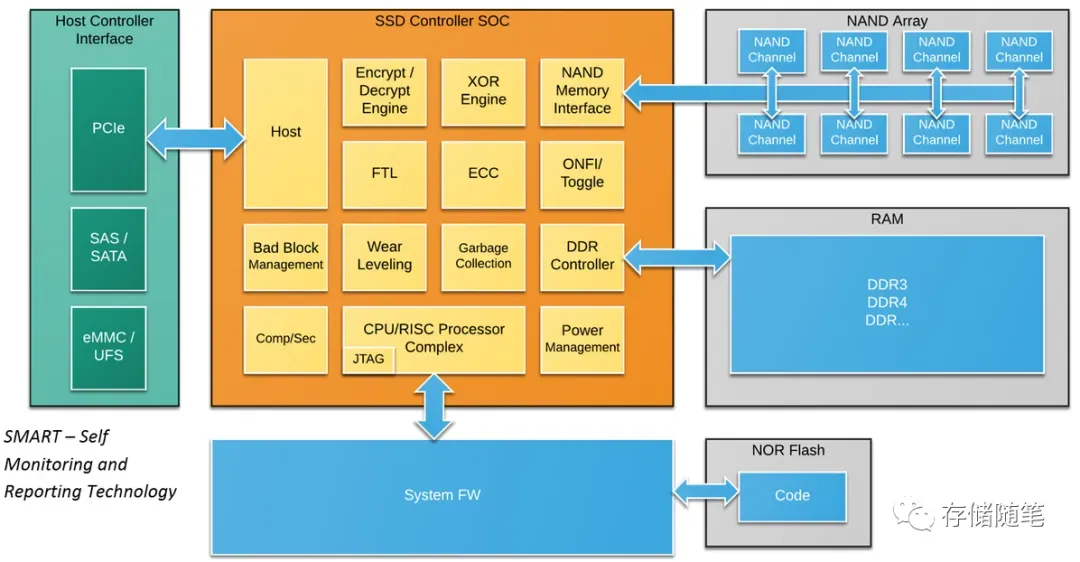

先来看一张完整架构:SSD主要包括了与Host接口协议、控制器芯片SOC,NAND闪存,DRAM缓存。

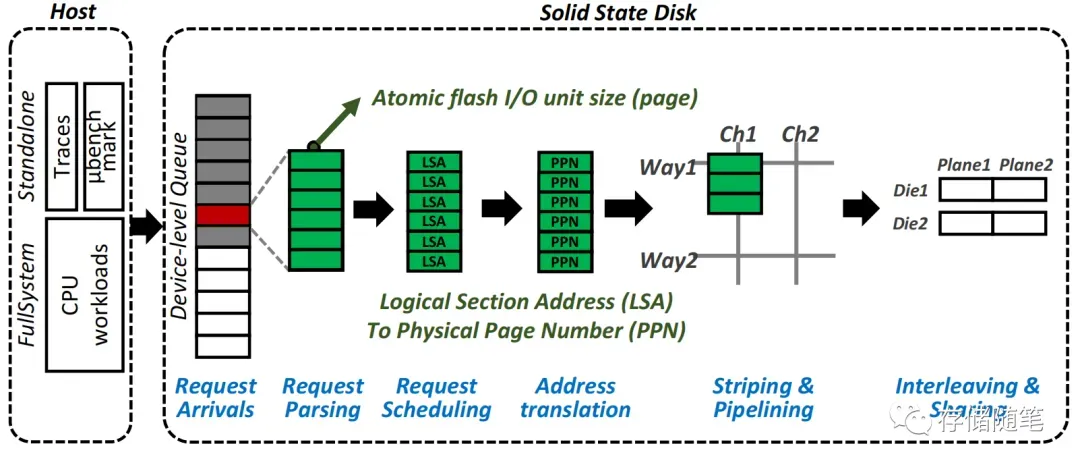

Host下发IO,到SSD内部的处理逻辑如下图。这里面核心点,IO逻辑地址LSA(或者叫LBA),到真正最后落入NAND,还有一层FTL转化为了NAND的物理地址PPN(或者叫做PBA)。

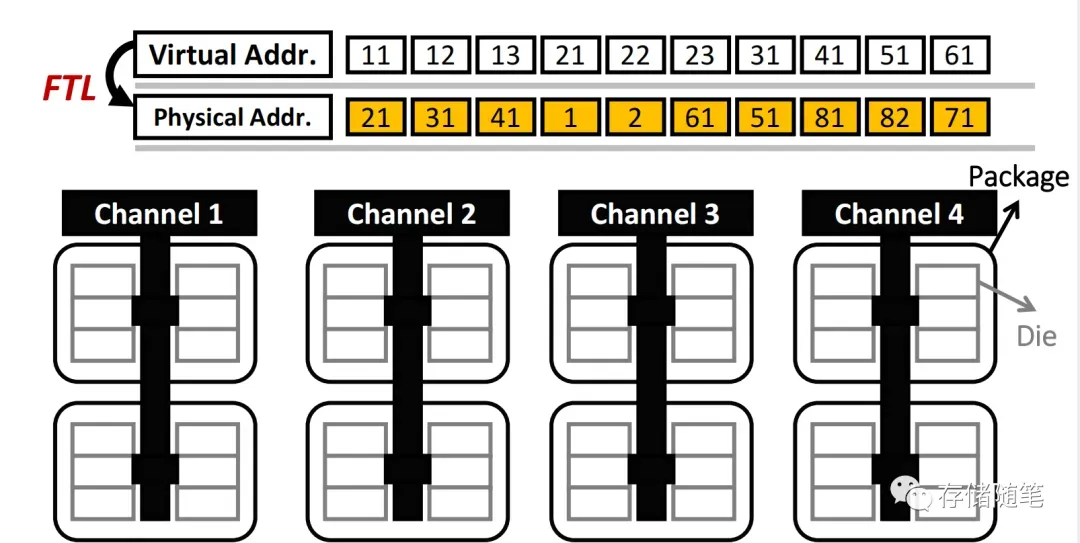

FTL管理着逻辑地址和物理地址的映射关系。有时候,逻辑地址不变,对应的物理地址在不断变化。

IO最后写入NAND的过程也有很多关卡:

-

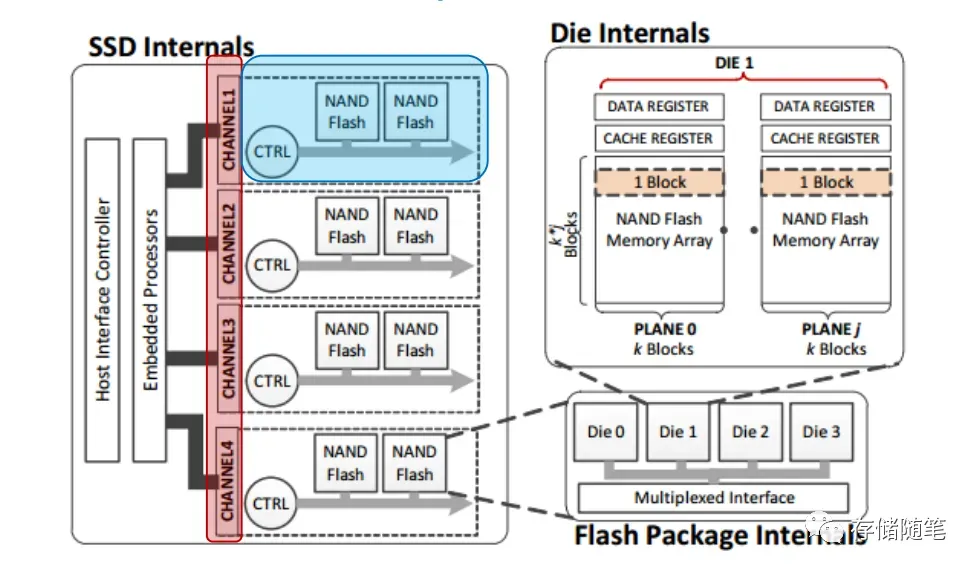

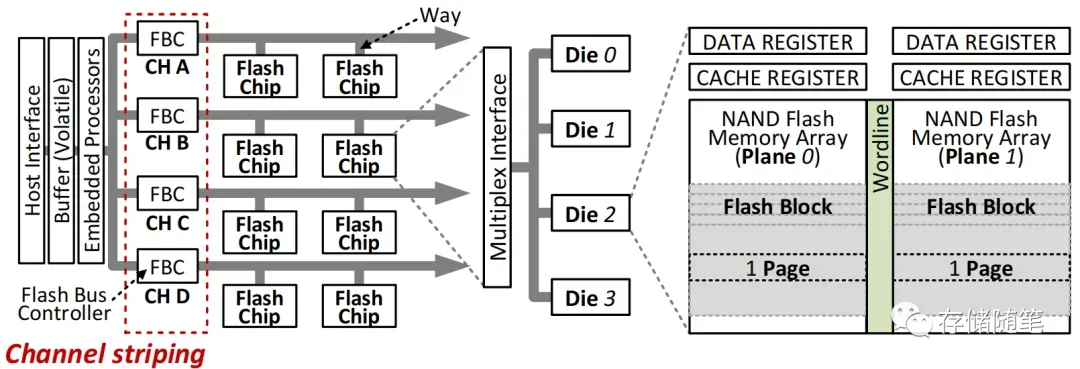

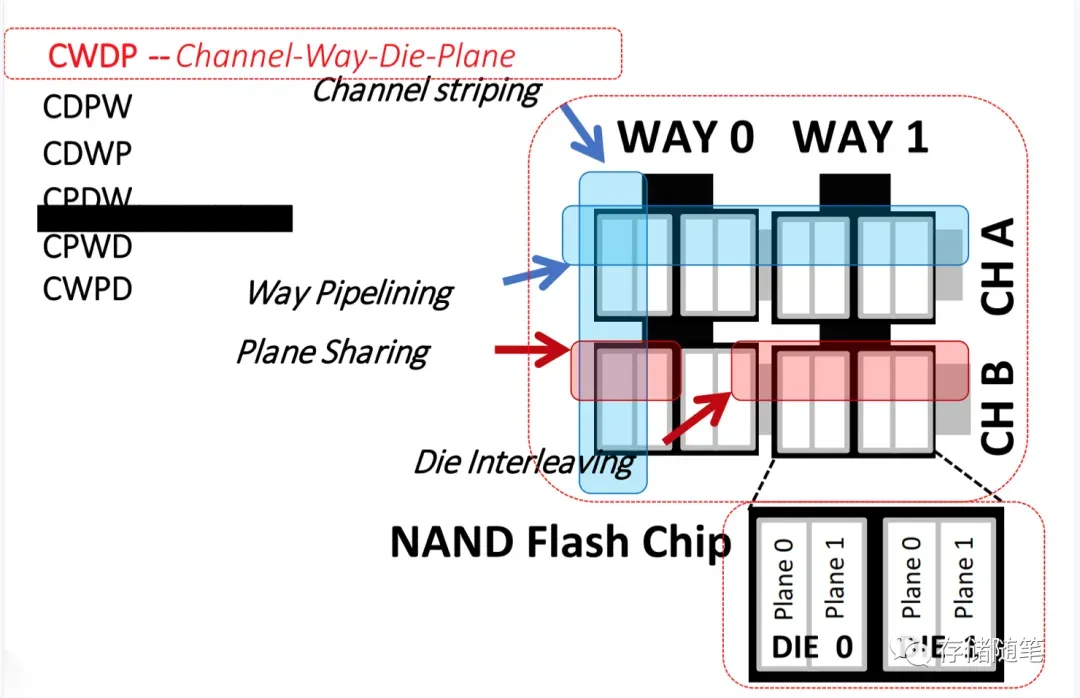

与SSD控制交互的NAND Channel,每个Channel通道有独立的NAND控制芯片。

-

每个Channel也有多个NAND芯片,不同芯片之间又有Way的概念。

-

每个NAND芯片,又包括了多个NAND die。

-

每个Die再细分还有不同Plane

-

每个Plane有很多个数据块Block

-

每个Block再细分就有了Page,每个block会有上千个page数据页。

为了提升固态硬盘(SSD)的性能,NAND相关的并发访问优化是关键因素之一,涉及NAND并发访问主要有以下几个方面:

-

多通道设计:现代SSD通常使用多通道架构,每个通道连接一组NAND闪存芯片。这样可以同时处理多个并行读写操作,从而提高I/O吞吐量和响应时间。

-

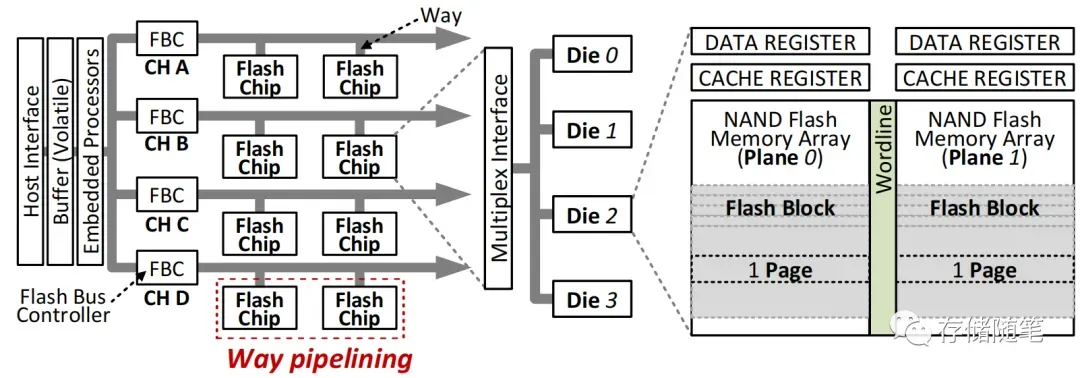

Way Pipeline设计:因为共享同一个channel通道,并不能完全并发执行。但NAND有erase/program/read多种操作,不同的操作响应时间也不一样,可以通过way pipeline的方式尽可能优化响应时间。这部分主要是在NAND package内部交叉执行(interleaving)

-

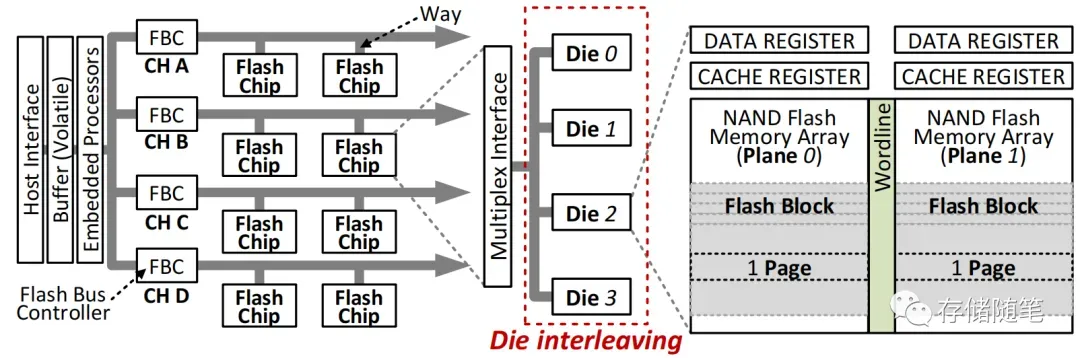

die间并发:当一个NAND芯片封装包含多个die时,可以在不同die之间并行地执行读写操作。这可以通过先进的控制器算法来实现,以充分利用所有可用资源。

-

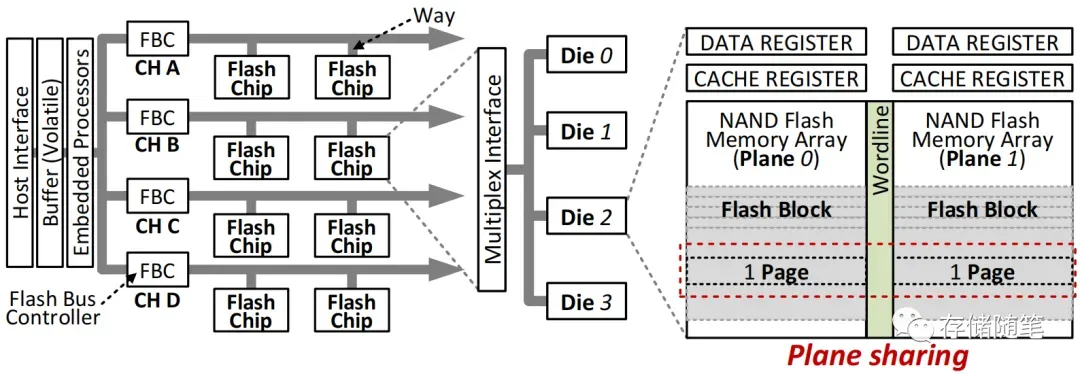

Plane间并发:在NAND闪存中,一个die(晶片)通常由多个plane组成。每个plane都包含独立的地址线、数据线和控制信号,能够并行地执行读写操作。不同plane之间的共享可以提高SSD的性能和效率。目前NAND都支持multi-plane的操作。

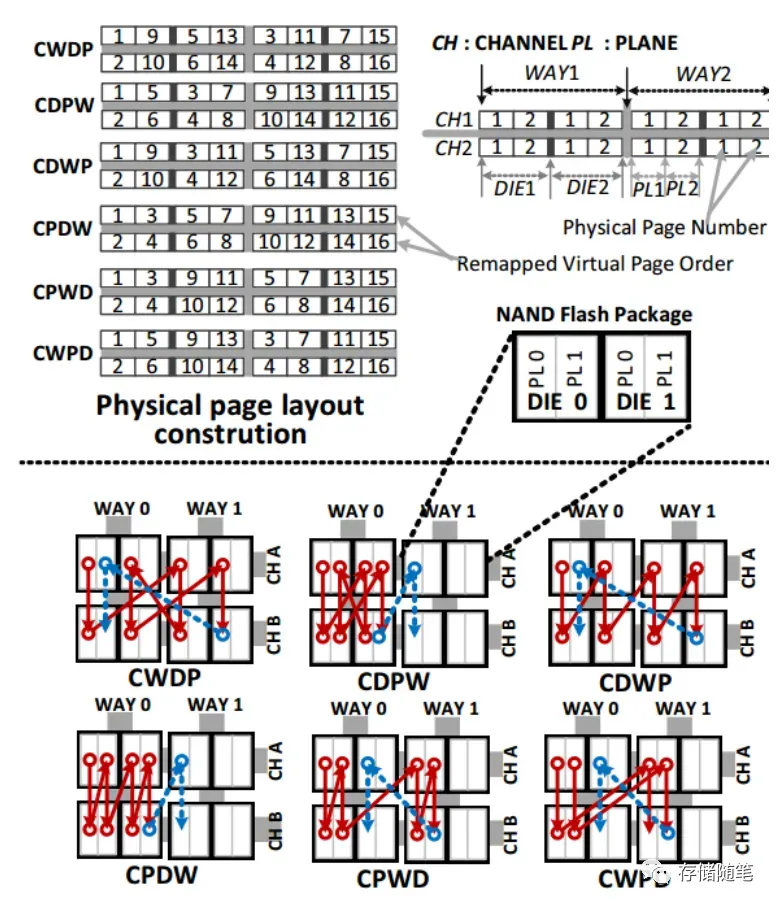

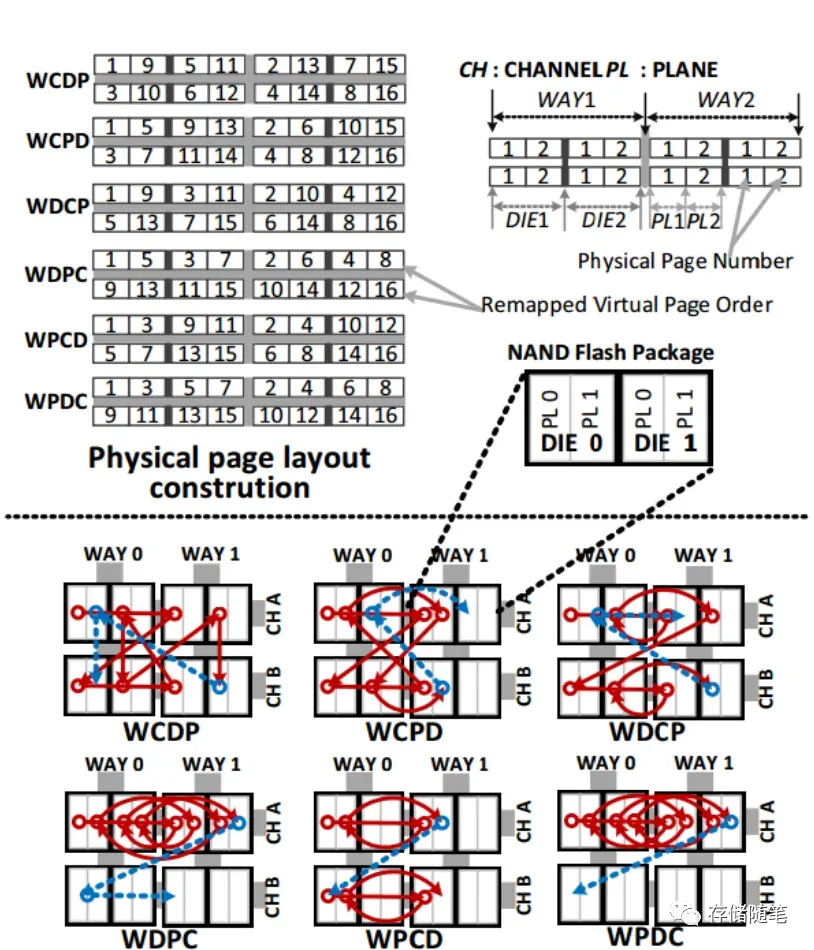

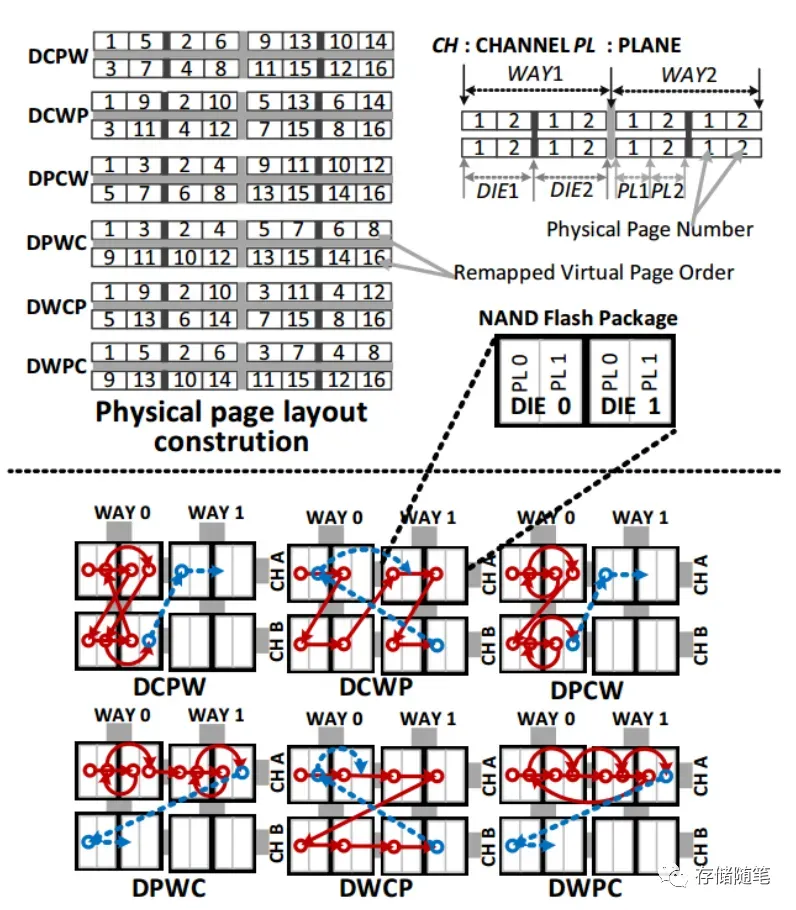

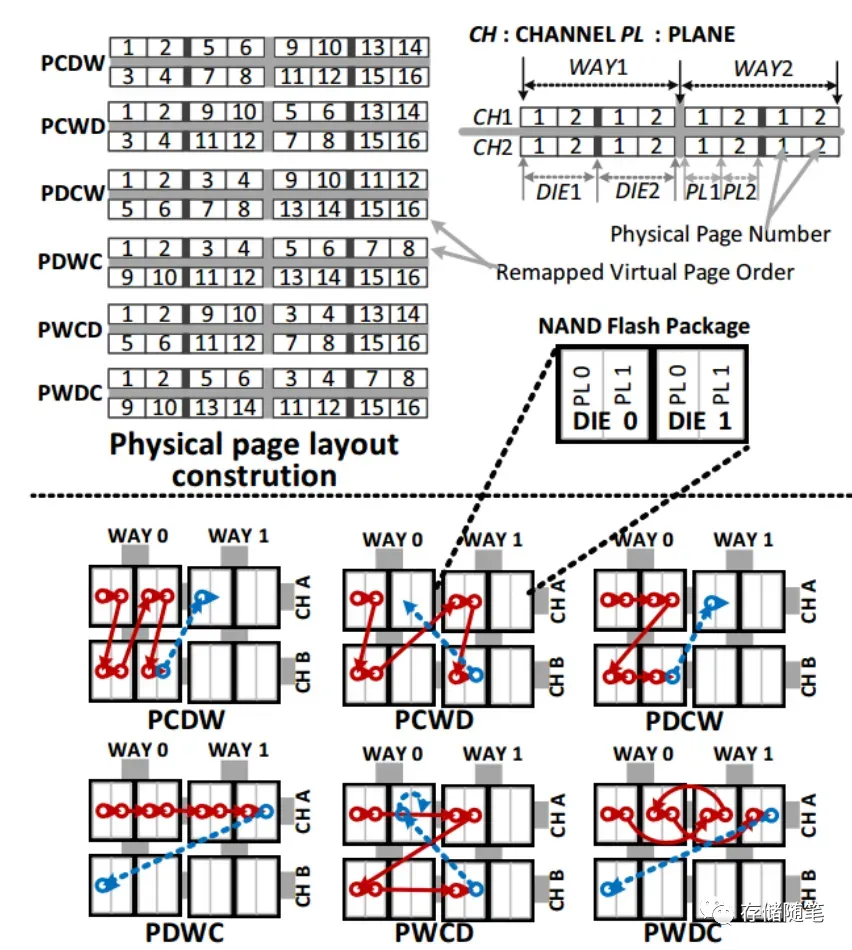

在进行数据写入数据页page时,不同的分配规则(比如Way优先、CH优先、Die优先),对性能有很大的影响。

如果以Channel优先进行Page页的分配策略,结合Way、Die、Plane的组合排列,数据分布的可能组合如下:

如果以Way优先进行Page页的分配策略,结合Channel、Die、Plane的组合排列,数据分布的可能组合如下:

如果以Die优先进行Page页的分配策略,结合Channel、Way、Plane的组合排列,数据分布的可能组合如下:

如果以Plane优先进行Page页的分配策略,结合Channel、Way、Die的组合排列,数据分布的可能组合如下:

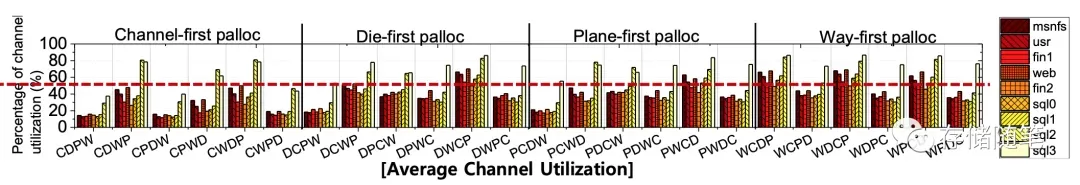

不同的page分配策略中,整体的有效利用率在43%。

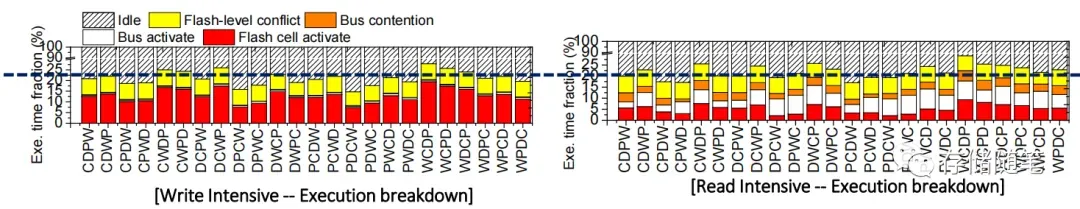

不同的page分配策略,在读写过程中,有80%的时间处于idle状态。

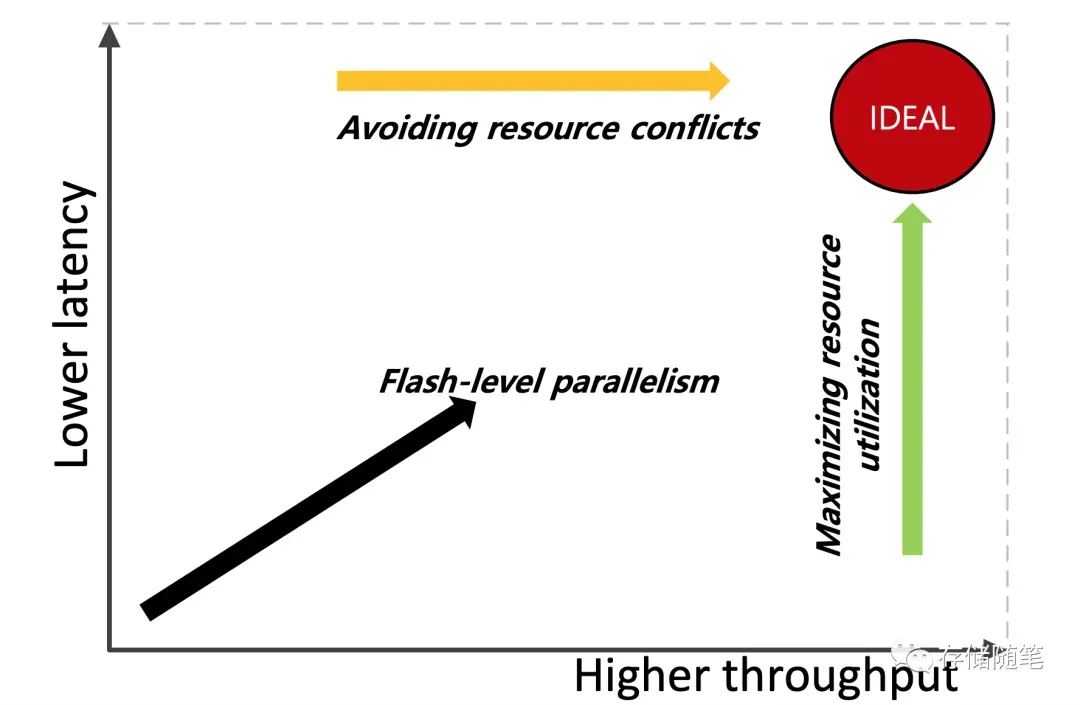

SSD整体优化策略就是要低延迟,高带宽,增加NAND的并发度。

声明:本文内容参考 Yonsei University Myoungsoo Jung教授团队研究比较早期成果,如果有不当之处,恭请留言指正,感谢!

文章出处登录后可见!