DMA(Direct Memory Access 直接内存访问),它允许某些计算机内部的硬件子系统可以独立地直接读写系统内存,而不需中央处理器(CPU)介入处理。

DMA存储传输的过程如下:

1. 处理器发出一条DMA命令,用以配置DMA,使DMA传输数据到存储器。

2. DMA控制器把数据从外设传输到存储器或从存储器到存储器或存储器到外设,而让CPU腾出手来做其它操作。

3. 数据传输完成后,向CPU发出一个中断来通知它DMA传输可以关闭了。

在PS和PL两端都有DMA,其中PS端的是硬核DMA,而PL端的是软核AXI DMA。

如何选用这两个DMA呢?

在ARM CPU设计的过程中,已经考虑到了大量数据搬移的情况,因此在CPU中自带了一个DMA控制器DAMC,这个DAMC驻留在PS内,而且必须通过驻留在内存中的DMA指令编程,这些程序往往由CPU准备,因此需要部分的CPU参与。DMAC支持高达8个通道,所以多个DMA结构的核可以挂在单个DMAC上。DAMC与PL的连接是通过AXI_GP接口,这个接口最高支持到32位宽度,这也限制了这种模式下的传输速率,理论最高速率为600MB/s。这种模式不占用PL资源,但需要对DMA指令编程,会增加软件的复杂性。如果从PS端的内存DDR3到I/O、DDR3、OCM,少量的数据传输的情况下就选择PS端的DMA;

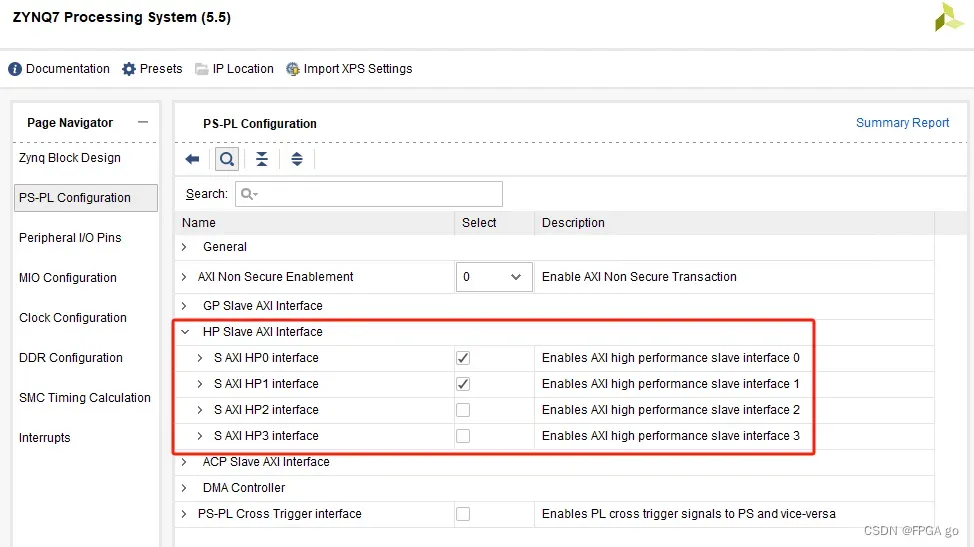

为了获取更高的传输速率,可以以空间换时间(内存换速率),在PL中添加AXI DMA IP核,并利用AXI_HP接口完成高速的数据传输。其缺点是会占用FPGA的一部分逻辑资源。

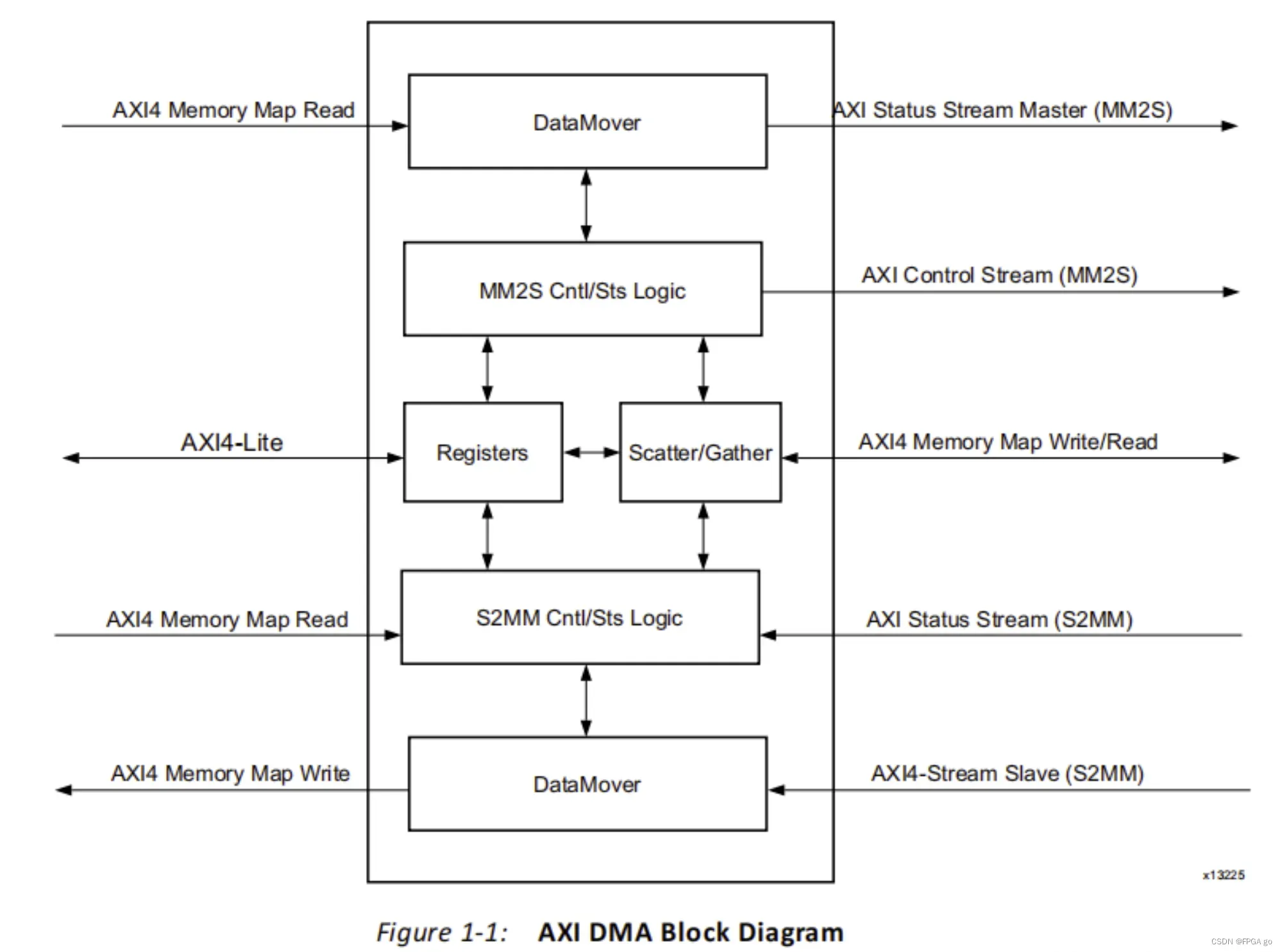

AXI DMA为内存和AXI4-Stream外设之间提供了高带宽的直接内存访问

其可选择的SG模式可以将CPU从数据搬运任务中解放出来

AXI DMA通过AXI-Lite接口对寄存器做一些配置和获取。

MM2S: MemoryMap to Stream 存储器映射(AXI4-Full)到AXI4-Stream

S2MM: Stream to MemoryMap AXI4-Stream到存储器映射(AXI4-Full)

AXI DMA 用到了三种总线,AXI4-Lite 用于对寄存器进行配置,AXI4 Memory Map 用于与内存交互,又分为 AXI4 Memory Map Read 和 AXI4 Memory Map Write 两个接口,一个是读一个是写。AXI4 Stream 接口用于对外设的读写,其中 AXI4 Stream Master(MM2S,Memory Map to Stream)用于对外设写,AXI4-Stream Slave(S2MM,Stream to Memory Map)用于对外设读。总之,在以后的使用中需要知道 AXI_MM2S 和AXI_S2MM 是存储器端映射的 AXI4 总线,提供对存储器(DDR3)的访问。AXIS_MM2S 和 AXIS_S2MM是 AXI4-streaming 总线,可以发送和接收连续的数据流,无需地址。

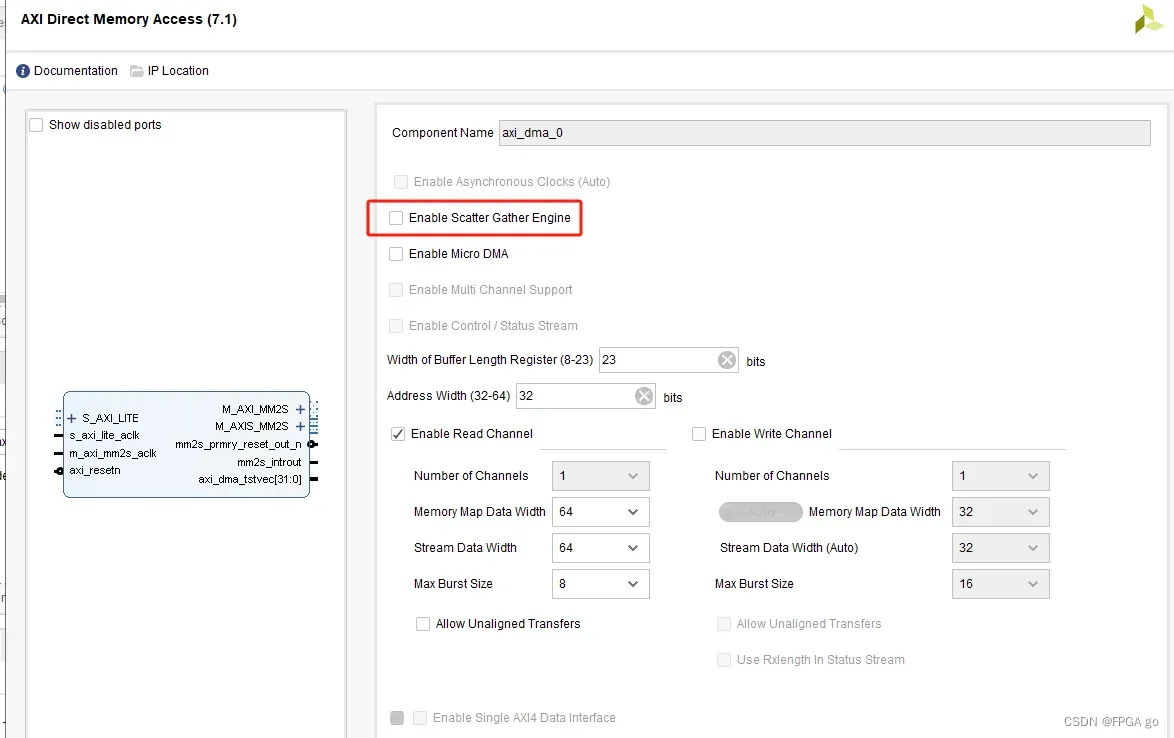

DMA分为两种模式:Simple DMA(简单模式)和Scatter Gather DMA(SG模式)

①简单模式

简单DMA模式(禁用SG模式即可)提供了一种可在MM2S和S2MM通道上执行简单DMA传输的配置,只需要较少的FPGA资源。通过访问DMACR(DMA控制寄存器)、源地址或目标地址和长度寄存器来启动DMA传输。当传输完成时,如果使能了产生中断输出,那么DMASR(DMA状态寄存器)相关联的通道位IOC_Irq会有效,便会产生中断。

DMA的MM2S(存储器映射到Stream)通道的启动顺序:

1、使能MM2S通道(令MM2S_DMACR.RS = 1);

2、如果需要的话,可以使能中断;

3、写一个有效的源地址到MM2S_SA寄存器(源地址寄存器)

注:如果没有使能DRE的功能,在指定起始地址时,需要注意字节地址对齐,哪些地址是对齐或者不对齐的,取决于stream流的数据位宽。如果启用了 DRE 并且

数据流位宽 < 128,则源地址可以是任意字节偏移。

4、写传输的字节数到MM2S_LENGTH寄存器。

注:一个长度位0的值是无效的,而一个非0的值,将会决定存储器映射到Stream流的数据个数;并且必须最后一个配置MM2S_LENGTH寄存器,而其他寄存器的配置顺序没有要求。这表明配置完数据长度,此时整个配置过程已经结束。

DMA的S2MM(Stream到存储器映射)通道的启动顺序:(和MM2S非常相似)

1、使能S2MM通道(令S2MM_DMACR.RS = 1);

2、如果需要的话,可以使能中断;

3、写一个有效的源地址到S2MM_DA寄存器(目的地址寄存器)

注:如果没有使能DRE的功能,在指定起始地址时,需要注意字节地址对齐,哪些地址是对齐或者不对齐的,取决于stream流的数据位宽。如果启用了 DRE 并且

数据流位宽 < 128,则源地址可以是任意字节偏移。

4、写传输的字节数到S2MM_LENGTH寄存器。

注:一个长度位0的值是无效的,而一个非0的值,将会决定Stream流到存储器映射的数据个数;并且必须最后一个配置S2MM_LENGTH寄存器,而其他寄存器的配置顺序没有要求。这表明配置完数据长度,此时整个配置过程已经结束。

②SG模式

在SG模式下,它把传输的基本参数,存储在内存中;

这些参数就是被称为BD(Buffer Descriptor)

在工作时,通过SG接口加载和更新BD中的状态。

版权声明:本文为博主作者:FPGA go原创文章,版权归属原作者,如果侵权,请联系我们删除!