FPGA驱动AD9226采集模拟信号并读取转换结果至寄存器。

文章目录

- 前言

- 一、AD9226时序图

- 二、具体思路

- 1.需求分析

- 2.代码示例

- 总结

前言:

AD9226是一种流水线形式的单通道ADC模数转换器。它支持12位宽、65MHz的采样精度和速度。

FPGA是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物,是作为ASIC专用集成电路领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点,优势显著。

因此,利用FPGA驱动AD9226实现瞬时信号的数据高速采集具有重大意义。

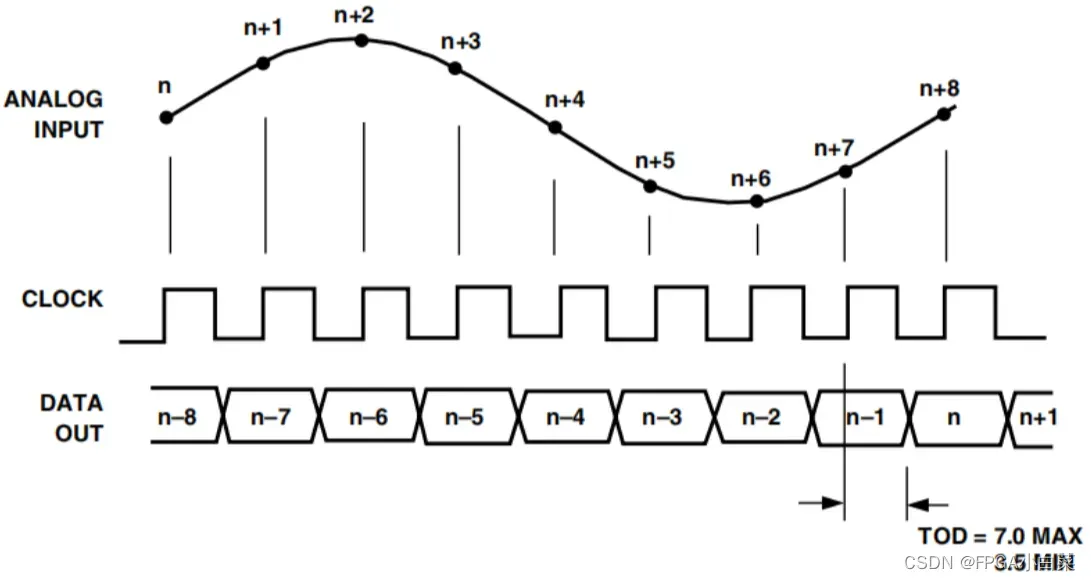

一、AD9226时序图

根据时序图书写Verilog代码。

二、具体思路

1.需求分析

首先定义一个ad9226_driver模块来实现AD9226的数据采集。该模块包括一个简单的状态机和一个计数器,用于控制AD9226的数据采集过程。在IDLE状态中,等待来自FPGA的采集开始信号。一旦接收到信号,将状态机转换到START状态,向AD9226发送启动转换命令。在CONVERSION状态中,等待AD9226完成数据采集,并从AD9226读取采集结果。一旦读取到结果,将状态机转换回IDLE状态,并将结果存储在adc_data中。

2.代码示例

代码如下(示例):

module ad9226_driver(

input clk, // 输入时钟信号

input reset, // 复位信号

output reg cs_n, // SPI片选信号

output reg sclk, // SPI时钟信号

input din, // SPI数据输入信号

output reg [15:0] adc_data, // AD转换结果输出信号

output reg conversion_done // 数据采集完成信号

);

// 定义状态机状态

parameter IDLE = 2'b00;

parameter START = 2'b01;

parameter CONVERSION = 2'b10;

// 状态机定义

reg [1:0] fsm_state;

// 计数器定义

reg [3:0] count;

// 初始化状态机和计数器

initial begin

fsm_state = IDLE;

count = 0;

end

// 状态机转换

always @(posedge clk) begin

case (fsm_state)

IDLE: begin

cs_n <= 1; // 禁用AD转换器

sclk <= 0; // SPI时钟信号置为低电平

adc_data <= 0; // 清零输出结果

conversion_done <= 0; // 数据采集完成信号置为低电平

if (reset) begin // 如果复位信号为高电平,则返回到IDLE状态

fsm_state <= IDLE;

end else if (din) begin // 如果SPI数据输入信号为高电平,则开始数据采集

fsm_state <= START;

end

end

START: begin

cs_n <= 0; // 启用AD转换器

sclk <= 0; // SPI时钟信号置为低电平

count <= 0; // 计数器清零

fsm_state <= CONVERSION; // 转换到CONVERSION状态

end

CONVERSION: begin

sclk <= 1; // SPI时钟信号置为高电平

count <= count + 1; // 计数器加1

if (count == 14) begin // 如果计数器达到14,则完成数据采集

adc_data <= {din, din}; // 从SPI数据输入信号读取AD转换结果

sclk <= 0; // SPI时钟信号置为低电平

cs_n <= 1; // 禁用AD转换器

conversion_done <= 1; // 数据采集完成信号置为高电平

fsm_state <= IDLE; // 返回到IDLE状态

end

end

default: fsm_state <= IDLE; // 默认返回到IDLE状态

endcase

end

endmodule

总结

以上就是FPGA驱动AD9226实现高速数据采集的思路分享,看完别忘点个关注和投币!谢谢!

文章出处登录后可见!

已经登录?立即刷新