写在前面

在自己准备写verilog教程之前,参考了许多资料—-FPGA Tutorial网站的这套verilog教程即是其一。这套教程写得不错,只是没有中文,在下只好斗胆翻译过来(加了自己的理解)分享给大家。

这是网站原文:https://fpgatutorial.com/verilog/

这是系列导航:Verilog教程系列文章导航

这篇文章将讨论 verilog 中一个重要的结构—- always 块(always block)。

verilog 中可以实现的数字电路主要分为两类—-组合逻辑电路和时序逻辑电路。与组合逻辑电路相反,时序电路电路使用时钟并一定需要触发器等存储元件。因此,输出信号与时钟同步,而不是立即发生变化。

在verilog中需要使用 always 块来编写时序逻辑电路,这一点至关重要。

1、Verilog 中的 Always 块(Always Block)

在编写 verilog 时,可以使用过程块(procedural blocks)来创建顺序执行的语句,过程块对于实现时序电路特别重要。相反,连续赋值语句在设计中并发(即并行)执行,这与底层电路的性质相匹配—-底层电路由许多独立的逻辑门组成。

always 块是 verilog 中最常用的过程块之一,每当敏感列表中的一个信号改变状态时,always 块中的所有语句都会按顺序执行。

下面的 verilog 代码显示了 always 块的一般语法。

always @(<sensitivity_list>) begin

//这里写要实现的代码

end使用这个结构时需要小心,因为有一些 verilog 独有的特性,特别是初学者经常很难理解信号在 always 块中更新的方式。

在使用 always 块时,可以并行或顺序(串行)更新信号的值。这取决于使用的是阻塞赋值(blocking assignment)还是非阻塞赋值(non-blocking assignment)。要想成为一名高效的 verilog 设计者,就必须很好地理解 always 块。

1.1、敏感列表(Sensitivity Lists)

在 always 块中编写的任何代码都会连续运行,这意味着代码块中的语句会按顺序执行,直到最后一行。一旦执行完序列中的最后一行,程序就会循环回到第一行,然后,always 块中的所有语句将再次按顺序执行。

然而,这种行为并不能描述这样一种电路—-其中一个输入信号改变状态之前将保持稳定状态的真实电路。verilog使用 alway 块中的敏感列表来模拟这种行为,所以,always 块中的代码将仅在敏感列表中的信号之一更改状态后执行。

1.1.1、触发器(Flip Flop )示例

与所有触发器一样,D 触发器的输出仅在时钟上升沿时才改变状态,因此可以将时钟信号包含在敏感列表中,以便 always 块仅在时钟信号出现上升沿时执行。

下面的 verilog 代码展示了如何使用 always 块实现 D 触发器。

always @(posedge clock) begin

q <= d;

end在此代码示例中使用了 posedge 来确定何时存在从 0 到 1 的转换(即时钟上升沿)。

当posedge的计算结果为真时,将执行 always 块中的单行代码,这行代码将输入D 的值分配给输出 Q。在 verilog 中使用 posedge 时,所有其他的状态变化都会被忽略,这正符合对 D 触发器的设计期望。

Verilog 也有一个具有相反功能的 negedge 。当使用negedge时,只要时钟从 1 变为 0(即时钟下降沿),always 块就会被执行。

设计者也可以不使用posedge/negedge,在这种情况下,只要敏感列表中的信号改变状态,代码就会执行。

1.1.2、敏感列表中的多个信号

在某些情况下,设计者希望在敏感列表中包含多个信号。一个常见的例子是要编写代码来实现一个具有异步复位的触发器,在这种情况下,设计师希望触发器在复位或时钟信号改变状态时才执行操作。

为此,可以在敏感度列表中列出两个信号,并用逗号分隔它们。下面的代码片段展示了如何实现这样一个触发器。

always @(posedge clock, posedge reset) begin

if (reset) begin

q <= 1'b0;

end

else begin

q <= d;

end

end由于此示例使用了高电平有效复位,高电平有效复位意味着复位仅在等于 1 时有效,因此再次在灵敏度列表中使用了 posedge ,然后使用了 if 语句的结构来确定 always 块是由复位信号还是时钟边沿信号触发。

使用Verilog-1995 标准的代码时,必须使用 or 关键字或逗号来分隔敏感列表中的信号。

下面的代码片段展示了如何使用 Verilog-1995 标准来实现异步可复位触发器。

always @(posedge clock or posedge reset) begin

if (reset) begin

q <= 1'b0;

end

else begin

q <= d;

end

end2、Verilog 中的阻塞赋值(Blocking Assignment)和非阻塞赋值(Non-Blocking Assignment)

到目前为止本文使用了两种不同类型的赋值运算符。这是因为 verilog 有两种不同类型的赋值——阻塞赋值和非阻塞赋值。使用非阻塞赋值编写代码时,使用 <= 符号,而阻塞赋值则使用 = 符号。

在verilog中使用连续赋值语句时时,只能使用阻塞赋值。但是,在过程块中可以使用这两种类型的赋值。

阻塞赋值通常会生成组合逻辑电路,而非阻塞赋值则通常会生成时序逻辑电路。

在 verilog 中使用阻塞赋值来对信号赋值时,信号会在代码行执行后立即更新它们的值,所以这种类型的赋值在 verilog 中通常被用来编写组合逻辑;相反,使用非阻塞赋值的信号在赋值后不会立即更新。

2.1、scheduled assignment

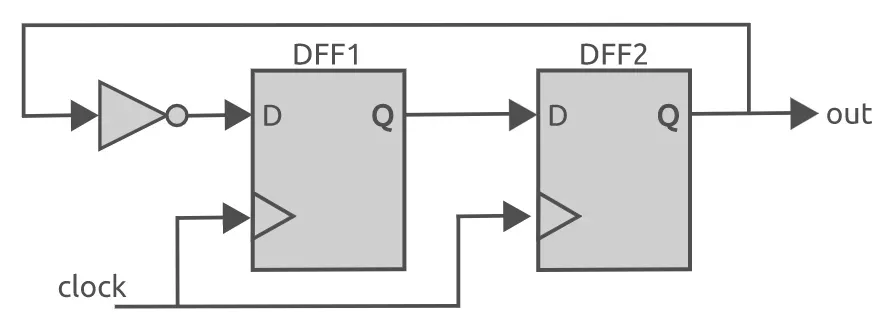

使用非阻塞赋值编写 verilog 代码时,代码仍然按顺序执行。但是,信号却不会以这种方式更新。为了说明为什么会这样,将以下面的扭环计数器电路(twisted ring counter)为例。

always @(posedge clock) begin

q_dff1 <= ~q_dff2;

q_dff2 <= q_dff1;

end首先来看看信号立即更新时的行为。假设当时钟边沿出现时两个触发器的输出都是 0,那么代码中的第二行会将 DFF1 的输出设置为 1,然后可以看到紧接其下方的代码行会将 DFF2 的输出设置为 1。但这显然不是该电路的预期行为。

为了克服这个问题,非阻塞赋值就会做scheduled assignment(预设赋值,这个术语我也不会翻译,大概意思是赋值的发生会“ 有计划性地安排在未来的某一个时间”)。因此,信号的更改不会在赋值后立即发生,而是在将来的某个时间发生。通常,信号会在仿真周期末尾更新它们的值—-这是指仿真工具在给定时间步长内执行所有代码所花费的时间。

为了更好地演示scheduled assignment的工作方式,请再次考虑简单的双触发器电路(dual flip flop circuit)。

当检测到上升沿时,模拟器首先执行更新 DFF1 的语句,然后将计划对 DFF1 的输出进行更新。当模拟器运行第二行代码,这次使用 DFF1 触发器的原始值并安排 DFF2 的更新。

由于此设计中只有两个语句,因此仿真周期现已完成。此时,所有计划的更改都将被实现并更新两个触发器的值。

2.2、综合案例(Synthesis Example)

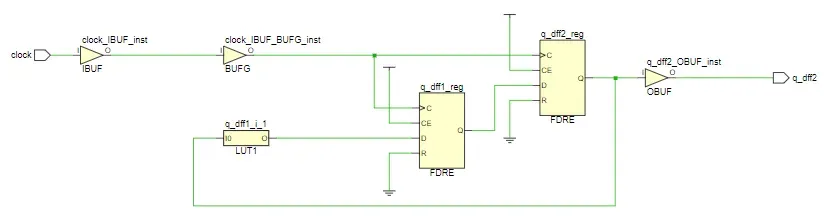

为了进一步展示 verilog 中阻塞赋值和非阻塞赋值之间的区别,接下来将再次模拟一个基本的双触发器扭环计数器电路。下面的代码片段展示了如何实现该电路。

always @(posedge clock) begin

q_dff1 <= ~q_dff2;

q_dff2 <= q_dff1;

end可以看下vivado所生成的电路图,如下所示。电路中有两个触发器,而非门是则使用 LUT1 实现的。

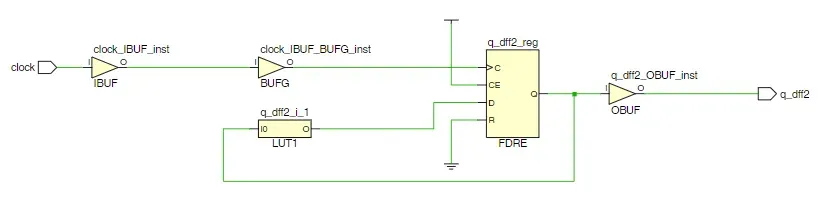

接着来看看如果在代码中使用阻塞赋值将会得到何种电路。下面的 verilog 代码展示如何尝试使用阻塞赋值来实现该电路(错误的示范)。

always @(posedge clock) begin

q_dff1 = ~q_dff2;

q_dff2 = q_dff1;

end这导致综合后的电路如下所示。

从这里可以看出,使用阻塞赋值导致电路中的第二个触发器被移除了。这样做的原因应该是相当明显的。由于 q_dff2 的值立即赋给与 q_dff1 相同的值,所以该信号路径中不应该有触发器。

这个例子实际上展示了 verilog 中阻塞赋值和非阻塞赋值之间最重要的一个区别—-使用非阻塞赋值时,综合工具总是会在电路中放置一个触发器。这意味着设计者只能使用非阻塞赋值来实现时序逻辑电路。相反,设计者可以使用阻塞来创建时序电路或组合电路。

但是,设计者应该只使用阻塞赋值来实现 verilog 中的组合逻辑电路,这样做的主要原因是编写的代码将更容易理解和维护。

3、Always 块中的组合逻辑

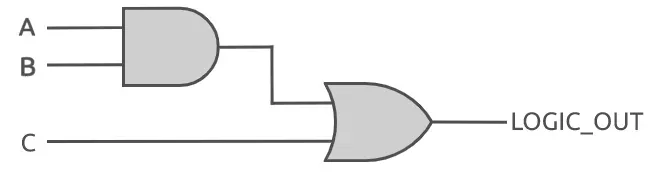

到目前为止,本文只考虑了使用 always 块的时序电路建模。虽然这是最常见的用例,但设计者也可以使用这种方法对组合逻辑进行建模。

例如,下面的代码展示了如何使用 always 块来实现如下所示的 AND-OR 电路。

// verilog-2001标准

always @(a, b, c) begin

logic_out = (a & b) | c;

end

// verilog-1995标准

always @(a or b or c) begin

logic_out = (a & b) | c;

end这段代码几乎与在连续赋值语句中实现的方法不同,主要区别就是被其封装在了一个 always 块中。此外还从语句中删除了assign关键字,因为在此情况下已经不再需要它了。

从这个例子中还可以看出,组合逻辑电路的敏感列表比时序逻辑电路更复杂。在实现组合逻辑电路时,实际上有两种方法可以用来编写敏感类别。

第一种方法是列出电路的每个输入,用 or 关键字或逗号分隔,这也是上面的示例代码中所使用的方法。

第二种方法是使用 * 字符来告诉综合工具自动决定将哪些信号包含在敏感列表当中。这种技术更可取,因为它更易于维护,但是,此方法是作为verilog-2001标准的一部分引入的,这意味着它不能与 verilog-1995标准的代码一起使用。

下面的代码片段展示了如何使用这两种方法。

// 穷举出所有信号的敏感列表

always @ (a, b, c)

// 使用 * 实现的敏感列表

always @ (*)一般来讲,只在少数情况下使用 always 块对组合逻辑电路进行建模,因为它可以简化复杂组合逻辑的建模。

多路选择器(Multiplexors)

如果想要实现多路选择器,使用 always 块来实现这种组合逻辑可能是一个很有用的办法。在这种情况下,可以使用被称为 case 语句的结构来实现多路选择器。这是一种更简单、更直观的大型多路选择器的实现方法。

下面的代码片段展示了如何使用 case 语句来实现一个简单的4选1多路选择器。

always @(*)

case (addr) begin

0 : begin

mux_out = a; //当addr = 0时,执行这条语句

end

1 : begin

mux_out = b; //当addr = 1时,执行这条语句

end

2 : begin

mux_out = c; //当addr = 2时,执行这条语句

end

3 : begin

mux_out = d; //当addr = 3时,执行这条语句

end

endcase

endcase 语句很容易理解,因为它通过一个变量来选择要执行哪条分支语句。在case语句中,设计者可以包含尽可能多的不同分支。此外,应该使用默认(default )分支来实现那些未被列出来的case条件值。

为了将其用作多路选择器,变量将被用作地址引脚,然后可以根据正在执行的分支将对应的值赋给多路选择器的输出。

📣您有任何问题,都可以在评论区和我交流📃!

📣本文由 孤独的单刀 原创,首发于CSDN平台🐵,博客主页:wuzhikai.blog.csdn.net

📣您的支持是我持续创作的最大动力!如果本文对您有帮助,还请多多点赞👍、评论💬和收藏⭐!

文章出处登录后可见!