文章目录

- ISE开发环境

- Vivado开发环境

- 方式1:XDC文件约束

- 方式2:生成选项配置

ISE开发环境

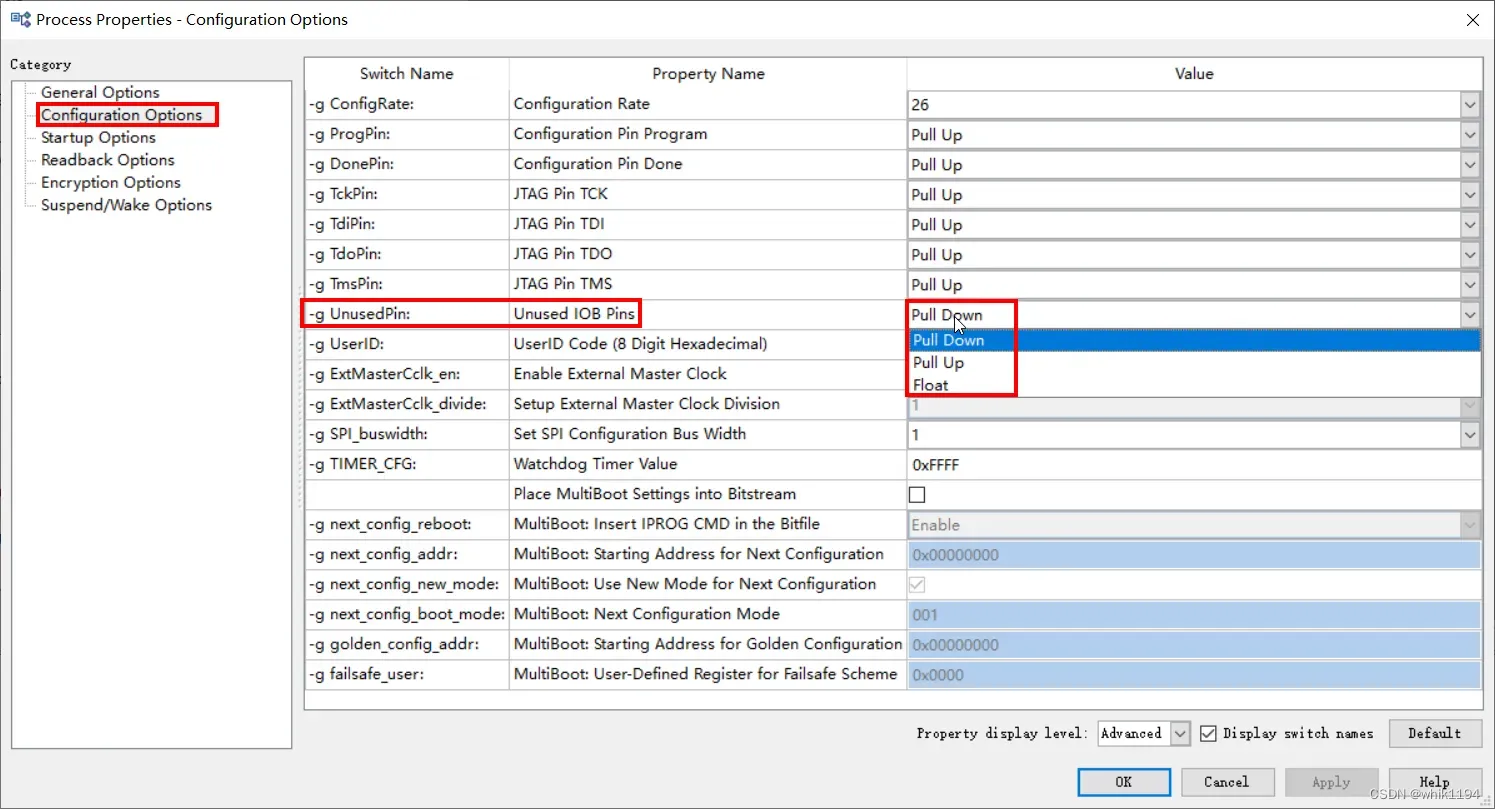

ISE开发环境,可在如下Bit流文件生成选项中配置。

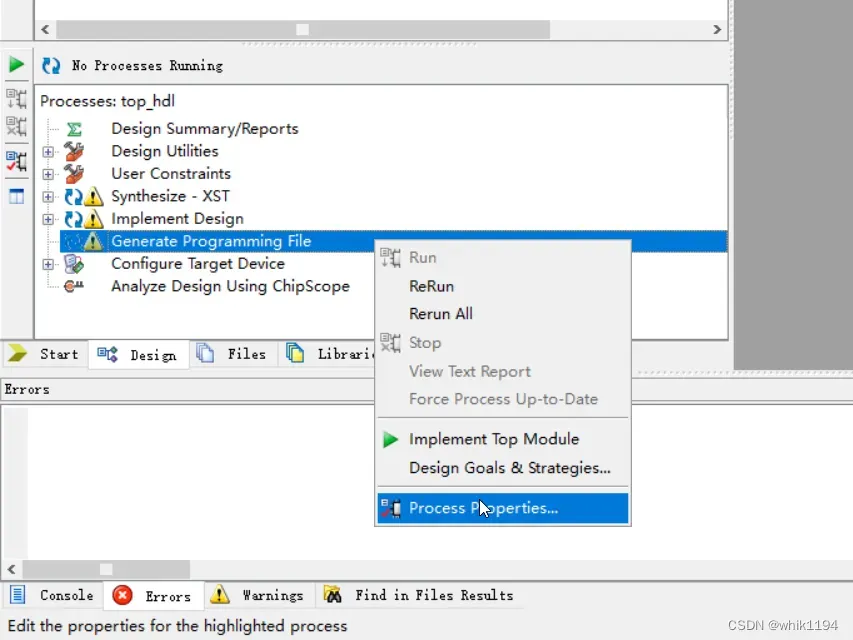

右键点击Generate Programming File,选择Process Properties,

在弹出的窗口选择Configuration Options->Unused Pin,选择Pull Down、Pull Up或者Float。

可以看到,除了未使用管脚,一些系统管脚,比如JTAG,Program、Done管脚等等都可以配置上下拉模式。

配置完成之后,重新生成Bit流文件即可。

Vivado开发环境

对于Vivado开发环境,共有两种方式可以设置未使用管脚的上下拉状态。

方式1:XDC文件约束

可以在XDC约束文件中根据需要添加以下约束语句,即可对未使用管脚电平状态进行设置:

#上拉

set_property BITSTREAM.CONFIG.UNUSEDPIN Pullup [current_design]

#下拉

set_property BITSTREAM.CONFIG.UNUSEDPIN Pulldown [current_design]

#悬空

set_property BITSTREAM.CONFIG.UNUSEDPIN Pullnone [current_design]

方式2:生成选项配置

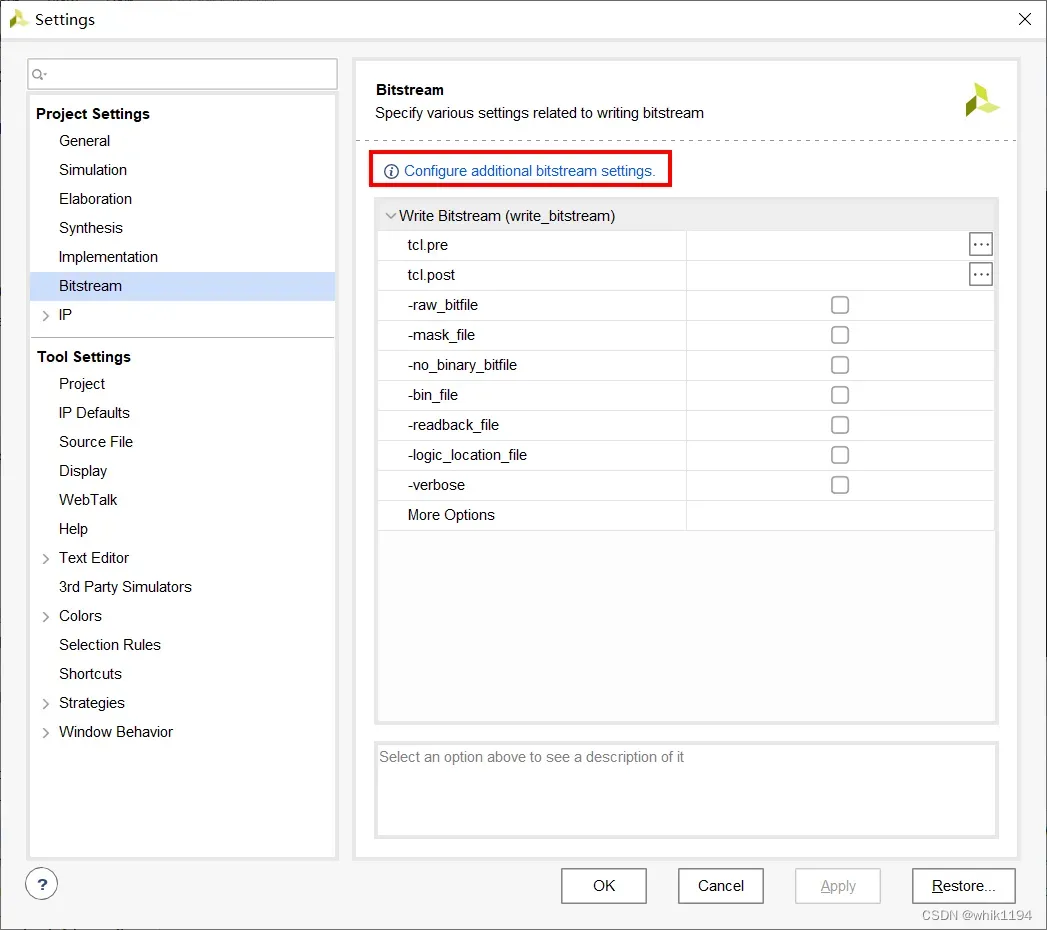

在Generate Bitstrem右键,选择Bitstream Settings,点击图中蓝色字体

如果没有出现蓝色字体,需要先Open Implemented Design,之后就可以进行配置了。

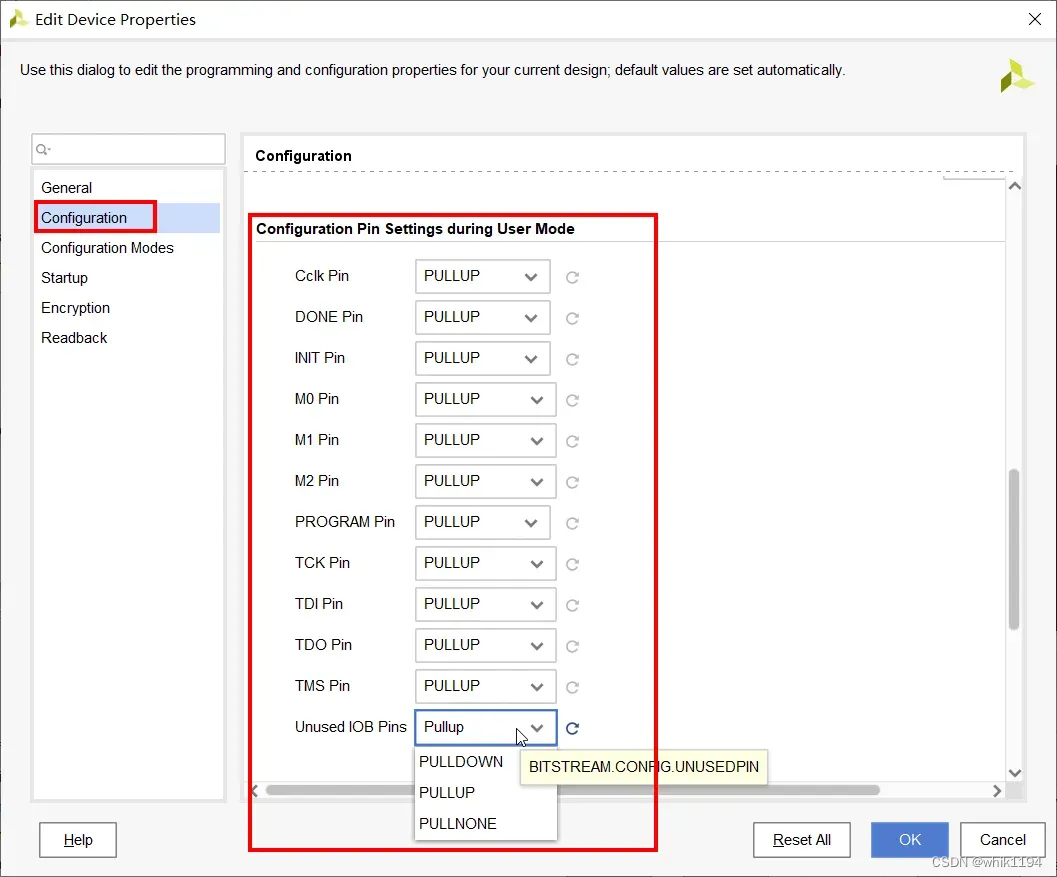

选择Configuration,下拉找到系统管脚配置,选择自己所需要的上下拉状态。

当把鼠标放在对应的选项时,会提示XDC约束语句的名称。

和ISE的生成选项配置类似,Vivado同样也可以配置JTAG管脚、Done、Prog等系统管脚的状态。

这两种配置方式的作用是一样,我更倾向于XDC文件约束的方式,方便在不同工程直接进行导入,设置完成之后,需要重新生成Bit流文件才能生效。

文章出处登录后可见!

已经登录?立即刷新