Global Clock Buffer Primitives(全局时钟缓冲器基本单元)在FPGA(现场可编程门阵列)和其他数字系统中扮演着至关重要的角色。这些基本单元被设计用于处理、分配和增强时钟信号,以确保系统中的各个组件都能以精确和同步的方式工作。

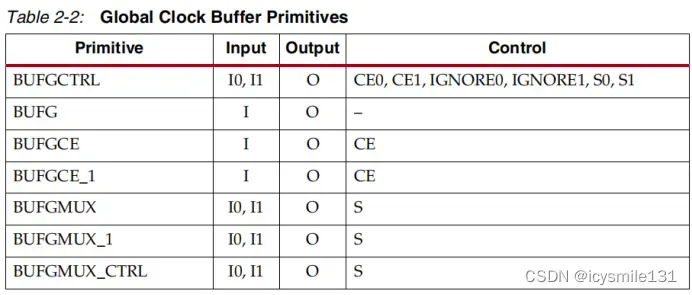

表2-2中的基本单元代表了全局时钟缓冲器的不同配置。

1. BUFGCTRL

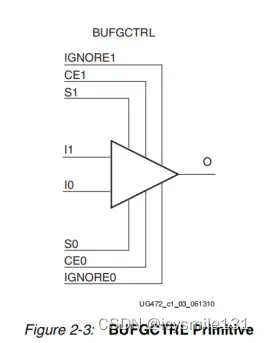

BUFGCTRL基本单元如图2-3所示,可以在两个异步时钟之间切换。所有其他全局时钟缓冲器基本单元都是基于BUFGCTRL的某些配置推导而来的。

BUFGCTRL具有四个选择线,即S0、S1、CE0和CE1。它还有两条额外的控制线,即IGNORE0和IGNORE1。这六条控制线用于控制输入I0和I1。

BUFGCTRL的工作机制是通过选择线和控制线来确定哪个输入时钟信号被传递到输出。选择线S0和S1用于选择输入I0或I1,而CE0和CE1则用于使能或禁用相应的输入。IGNORE0和IGNORE1控制线提供了额外的灵活性,可以在某些条件下忽略输入时钟的变化。

BUFGCTRL的设计是为了在两个时钟输入之间切换,而不会出现任何毛刺(glitch)。当目前所选的时钟在S0和S1改变后从高电平过渡到低电平时,输出将保持低电平状态,直到另一个(待选)时钟从高电平过渡到低电平。然后,新的时钟开始驱动输出。BUFGCTRL的默认配置是对下降边沿敏感的,并且在输入切换之前保持在低电平状态。通过使用INIT_OUT属性,BUFGCTRL也可以配置为对上升边沿敏感,并在输入切换之前保持在高电平状态。

在某些应用中,之前描述的条件可能并不理想。断言IGNORE引脚将使BUFGCTRL绕过检测两个时钟输入之间切换的条件。换句话说,当断言IGNORE时,多路复用器(MUX)会在选择引脚变化的瞬间切换输入。IGNORE0会在选择引脚变化时立即使输出从I0输入切换开,而IGNORE1则会在选择引脚变化时立即使输出从I1输入切换开。

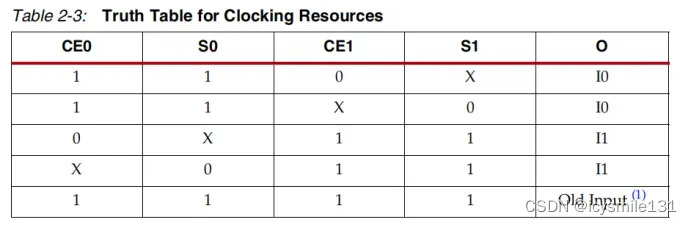

选择一个输入时钟需要一对“选择”信号(S0和CE0,或S1和CE1)被断言为高电平。如果S或CE中的任何一个没有被断言为高电平,那么期望的输入将不会被选中。在正常情况下,不期望S和CE对(所有四个选择线)同时被断言为高电平。通常,一个“选择”对中的一个引脚用作选择线,而另一个引脚则连接高电平。真值表如表2-3所示。

注意:

①旧输入指的是在此状态达到之前的有效输入时钟。

②对于所有其他状态,输出将变为INIT_OUT属性的值,并且不会切换(toggle)。

对于两个控制信号:S和CE。尽管两者都用于选择所需的输出,但仅建议使用S进行无故障切换。这是因为当使用CE切换时钟时,时钟选择的变化可能比使用S时更快。如果CE引脚的建立/保持时间(Setup/Hold time)被违反,时钟输出可能会产生故障(glitch)。故障是指电路中的瞬时错误信号,可能导致电路功能异常。

另一方面,使用S引脚可以在不考虑建立/保持时间的情况下在两个时钟输入之间切换。因此,使用S切换时钟不会导致故障。

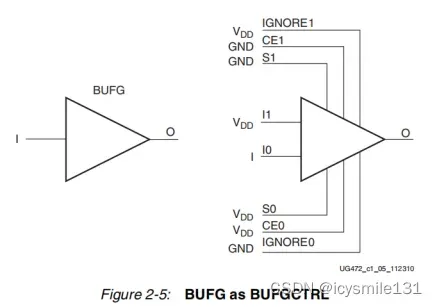

2. BUFG

BUFG是一个具有一个时钟输入和一个时钟输出的时钟缓冲器。这个基本单元是基于BUFGCTRL的,其中一些引脚被连接到逻辑高电平或低电平。BUFG通常用于确保时钟信号的稳定性和质量,减少时钟信号的抖动和偏斜。

图2-5展示了BUFG和BUFGCTRL之间的关系。可以使用LOC约束来手动放置BUFG的位置。

BUFGCTRL是一个更高级别的控制单元,用于配置和管理BUFG的行为。它提供了更多的配置选项,允许用户根据需要调整BUFG的工作方式。然而,BUFG可以被视为BUFGCTRL的一个简化版本,其中某些引脚被固定连接到高电平或低电平,从而限制了其配置选项。

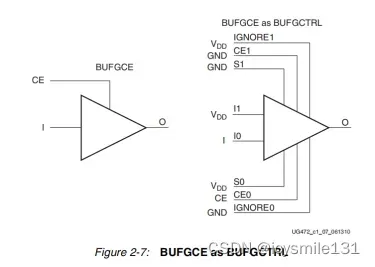

3. BUFGCE和BUFGCE_1

都是具有一个时钟输入、一个时钟输出以及一个时钟使能(enable)线的时钟缓冲器。这些基本单元都是基于BUFGCTRL的,其中一些引脚被连接到逻辑高电平或低电平。图2-7展示了BUFGCE和BUFGCTRL之间的关系。

BUFGCE的时钟使能线允许设计者动态地控制时钟信号的传递。当使能线被激活(通常是置为高电平)时,时钟信号会从输入传递到输出;当使能线被禁用(置为低电平)时,时钟输出会被停止或保持在当前状态,这取决于具体的FPGA实现。

BUFGCE的切换条件与BUFGCTRL类似。如果CE(时钟使能)输入在即将到来的上升时钟边沿之前为低电平,那么接下来的时钟脉冲不会通过时钟缓冲器,并且输出将保持低电平。在时钟信号处于高电平期间,CE的任何电平变化都不会产生影响,直到时钟信号变为低电平。当时钟被禁用时,输出保持低电平。然而,当时钟正在被禁用时,它会完成时钟高电平的脉冲。

由于时钟使能线使用BUFGCTRL的CE引脚,因此选择信号必须满足建立时间要求。违反这个建立时间可能会导致出现毛刺(glitch)。建立时间是指信号在到达其目标之前必须保持稳定的最短时间,以确保电路能够正确响应。在BUFGCE的情况下,如果CE信号在时钟边沿到达之前没有足够的建立时间,可能会导致输出不稳定或产生意外的脉冲,这可能会对系统的稳定性和性能产生负面影响。

BUFGCE_1与BUFGCE非常相似,但它们的切换条件有所不同。如果CE输入在即将到来的下降时钟边沿之前为低电平,那么接下来的时钟脉冲不会通过时钟缓冲器,并且输出将保持高电平。在时钟信号处于低电平期间,CE的任何电平变化都不会产生影响,直到时钟信号变为高电平。当时钟被禁用时,输出保持高电平。然而,当时钟正在被禁用时,它会完成时钟低电平的脉冲。

与BUFGCE一样,BUFGCE_1的CE引脚也用于控制时钟信号的传递。不同的是,BUFGCE_1对下降时钟边沿敏感,而BUFGCE则对上升时钟边沿敏感。这种差异使得BUFGCE_1能够在不同的应用场景中提供更大的灵活性。

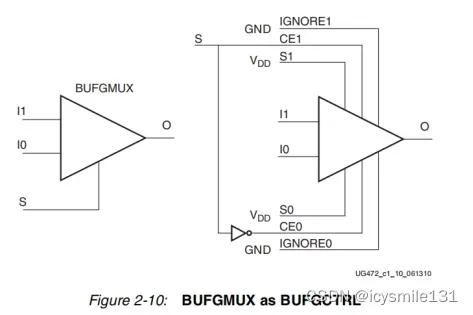

4. BUFGMUX和BUFGMUX_1

都是带有两个时钟输入、一个时钟输出以及一个选择线的时钟缓冲器。这些基本单元基于BUFGCTRL,其中一些引脚被连接到逻辑高电平或低电平。图2-10展示了BUFGMUX和BUFGCTRL之间的关系。

BUFGMUX的主要功能是根据选择线的状态来选择并传递两个输入时钟信号中的一个到输出。选择线通常是一个二进制信号,当它为高电平时,BUFGMUX会选择并输出第一个时钟输入;当它为低电平时,则会选择并输出第二个时钟输入。这种能力使得BUFGMUX在需要动态切换不同时钟源的应用中非常有用,比如在不同工作模式之间切换、故障切换或时钟门控等场景。

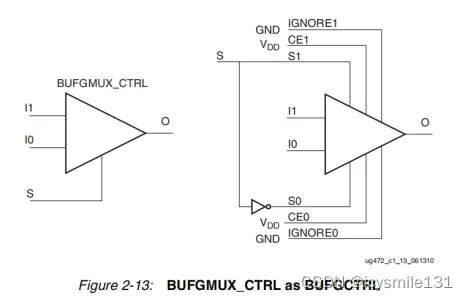

5. BUFGMUX_CTRL

BUFGMUX_CTRL具有两个时钟输入、一个时钟输出以及一个选择线,这使得它能够在两个不同的时钟源之间切换,并将选定的时钟信号传递到输出。图2-13展示了BUFGMUX_CTRL和BUFGCTRL之间的关系。

BUFGMUX_CTRL的设计基于BUFGCTRL,并通过一些引脚连接到逻辑高电平或低电平来实现其功能。这种设计使得BUFGMUX_CTRL能够利用BUFGCTRL的灵活性和性能优势,同时增加了额外的控制选项,以满足更复杂的时钟管理需求。

BUFGMUX_CTRL使用S引脚作为选择引脚。S可以在任何时候进行切换,而不会导致毛刺(glitch)的产生。S引脚的建立时间(Setup time)和保持时间(Hold time)用于确定在切换到新时钟之前,输出是否会传递之前所选时钟的额外脉冲。

6. 其他模型

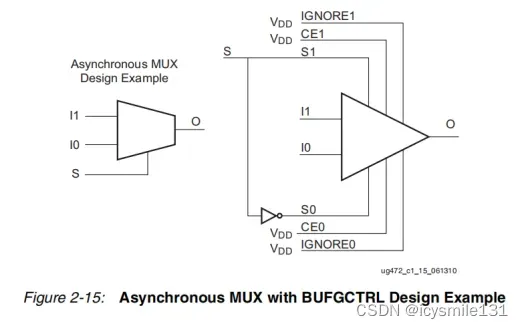

① 使用BUFGCTRL的异步MUX

在某些情况下,应用程序需要立即在时钟输入之间切换,或者绕过BUFGCTRL的边沿敏感性。一个例子是当其中一个时钟输入不再切换时。如果发生这种情况,时钟输出将不会具有正确的切换条件,因为BUFGCTRL从未检测到时钟边沿。在这种情况下,需要使用异步MUX。图2-15展示了使用BUFGCTRL的异步MUX设计示例。

异步MUX允许在不考虑时钟边沿的情况下进行时钟信号的切换。它不受BUFGCTRL的边沿检测机制的限制,因此即使某个时钟输入停止切换,也能实现快速的时钟源切换。

在设计异步MUX时,需要特别注意确保切换过程不会导致时钟信号的失真或毛刺。这通常涉及到对S引脚(选择引脚)的精确控制,以确保在切换过程中时钟信号的稳定性和连续性。

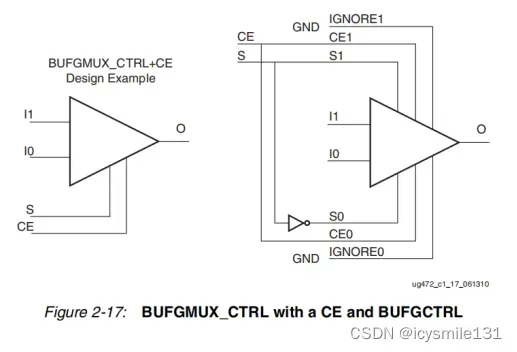

② 带有时钟使能的BUFGMUX_CTRL

带有时钟使能的BUFGMUX_CTRL和BUFGCTRL配置允许在选择输入时钟信号之间进行切换。如果需要,可以使用时钟使能来禁用输出。图2-17展示了BUFGCTRL的使用设计示例。

在这种配置中,BUFGMUX_CTRL用作多路复用器,它根据S引脚(选择引脚)的状态选择并传递一个输入时钟信号到输出。同时,BUFGCTRL提供时钟使能功能,通过控制CE引脚(时钟使能引脚)的状态来启用或禁用BUFGMUX_CTRL的输出。

当时钟使能被禁用(CE引脚为低电平)时,无论BUFGMUX_CTRL如何选择时钟输入,其输出都将被禁止,即输出时钟信号将被停止。这提供了一种灵活的方式来控制时钟信号的传播,以适应不同的系统需求和工作模式。

版权声明:本文为博主作者:icysmile131原创文章,版权归属原作者,如果侵权,请联系我们删除!

原文链接:https://blog.csdn.net/u011565038/article/details/137969219