什么是Cache?

Cache是一种用来提高计算机运行速度的一种技术。它是一种小而快的存储设备,位于CPU与内存之间,用于平衡高速设备与低速设备之间的速度差异。Cache可以存储常用的数据或指令,以便CPU更快地获取,从而减少对主存的访问次数,加快程序的执行速度。

为什么需要Cache(高速缓冲存储器)?

我们都知道CPU处理数据的速度非常快,虽然内存的读写速度也不慢,但是相对于CPU它的速度就显得太慢了,所以如果单纯地让CPU对内存进行读写,所消耗的时间绝大部分是在内存对数据的处理上,而这时候CPU就在空等,浪费了资源,因此就需要在CPU与内存之间连接一个Cache来作为缓冲。

Cache的基本特点

由于Cache是为了缓解内存处理数据太慢而出现的,因此Cache应该具备的一个基本特点就是读写数据的速度快,能够比较好地匹配CPU的速度,尽可能地让CPU忙起来,但是就是因为它处理速度快,所以就造成了它的容量比较小,如果能够既可以容量大又可以速度快的话直接把内存的速度提高到匹配到CPU的速度就好了,但是由于材料的价格,技术复杂度等等原因,Cache还是很必要的。

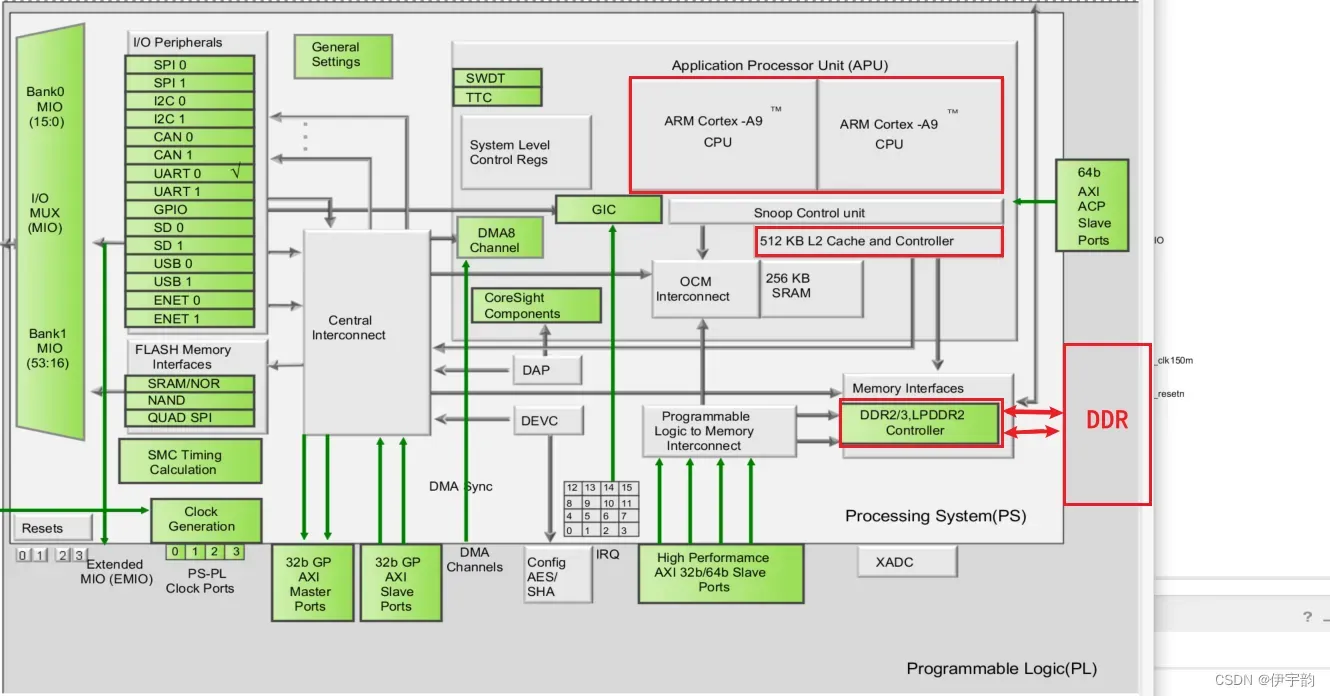

在ZYNQ中,如下图:

Cache就是缓存,作用就是提高CPU运行的效率。

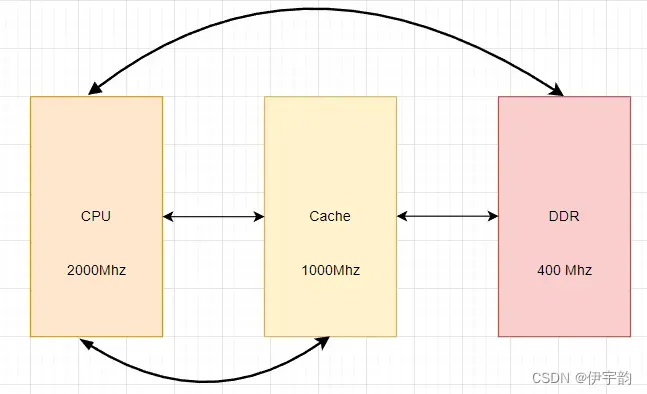

看下图:

假设CPU的时钟是2000Mhz,Cache的时钟100Mhz,DDR的时钟400Mhz,那么CPU往Cache里面写数据是快于CPU往DDR写数据的,这样的话CPU就忙起来,提高CPU运行的效率。

Cache一致性

PS往 DDR 里面写数据,路径是PS cpu–>Cache –>DDR,正常情况下,数据是会被写到 DDR 里面的,不过有时候出现Bug,PS 产生的数据写入 Cache之后,数据并没有写入 DDR。

读的过程也是一样的,PS 读取 ddr 数据路径相反,有时候也会出现 Bug,也就是PS读取DDR的数据出现错误。

解决方法

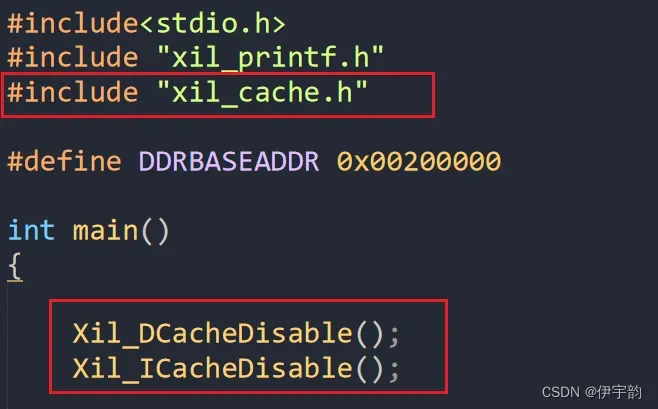

- 调试过程中,直接禁用cache,使用Xil_DCacheDisable()函数;CPU将直接访问DDR内存,读写都是直接的,这会降低CPU性能,但简化了数据传输操作。

2.使用Xil_CacheFlush和Xil_Cache Invalidate操作,

PS写完数据之后,添加Xil_CacheFlush函数,这个函数的作用是将数据从 Cache 刷新到 DDR 里面去,即将Cache内容推到DDR中;

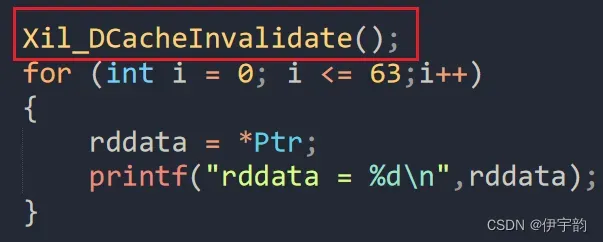

PS 从 DDR里面读取数据之前,添加 Xil_Cache Invalidate 函数,这个函数的作用是将 DDR里面的数据刷新到Cache里面去,即把数据从DDR中拉到Cache中。

总结

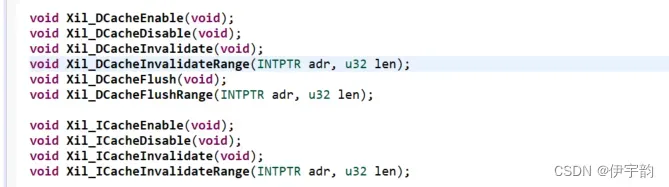

在xil_cache.h头文件中,有关于Cache的处理函数,如下图:

关于Cache的详细底层处理过程,可以查看这些函数。

版权声明:本文为博主作者:伊宇韵原创文章,版权归属原作者,如果侵权,请联系我们删除!

原文链接:https://blog.csdn.net/weixin_46897065/article/details/138046242