RAM(Random Access Memory),也就是随机存取寄存器,它可以随时把数据数据写入任一指定地址的存储单元,也可以随时从任一指定地址中读出数据,其读写速度是由时钟频率决定的。

在本例程汇总,实现了向RAM里面写入1024个数据,然后再读取出来,通过ILA(在线逻辑分析仪)进行查看。

1、新建工程

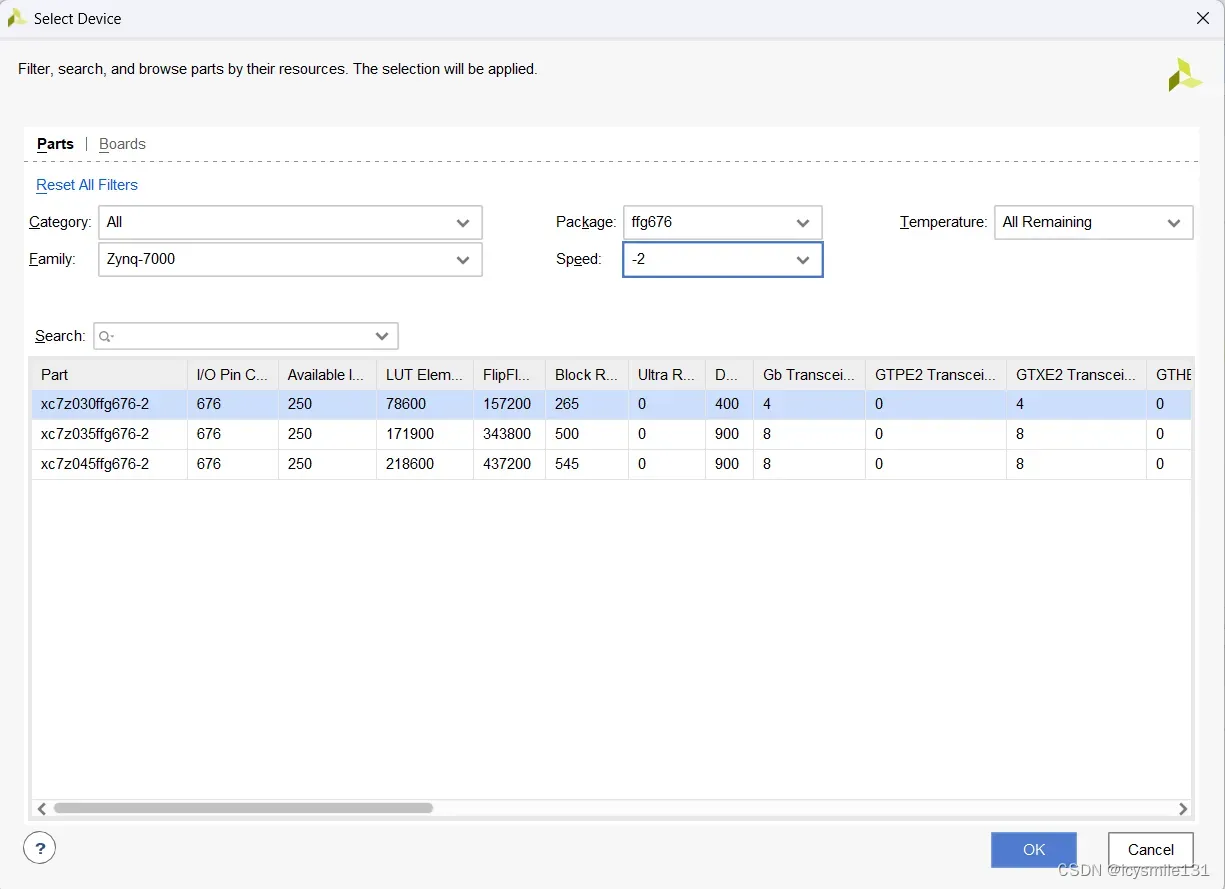

器件选择Zynq 7000系列中的xc7z030ffg676-2,其他按默认选项。

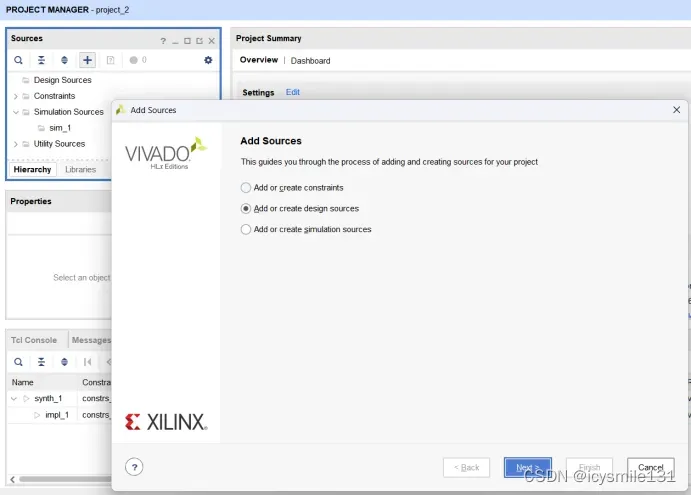

在Design source中,选择“+”来生成代码文件。

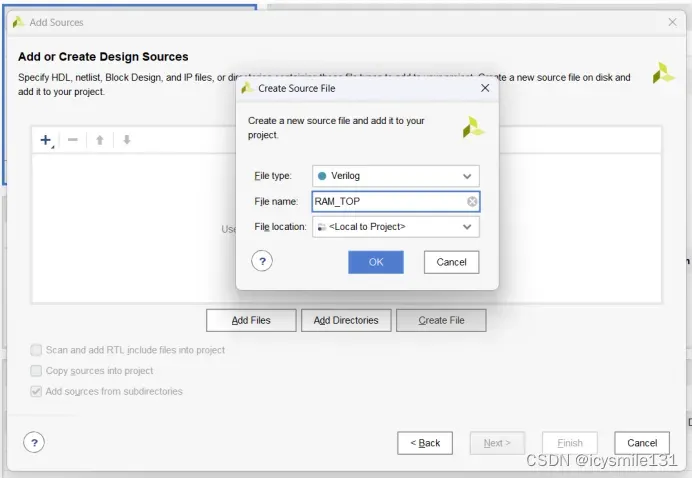

创建一个RAM_TOP文件,并且选择Verilog格式。

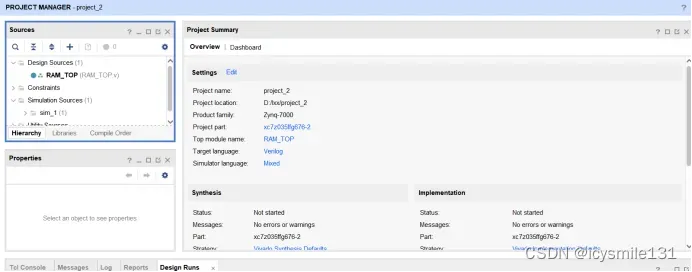

创建完成后,可以看到Design Sources文件夹中有一个RAM_TOP.v文件,这就是需要编写verilog程序的文件。

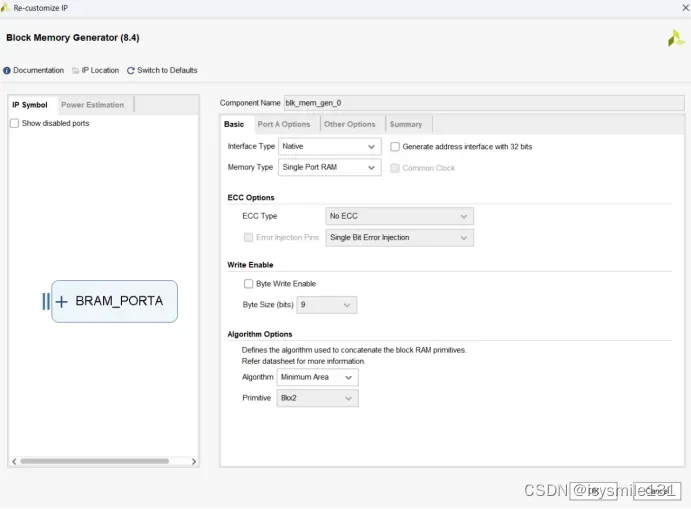

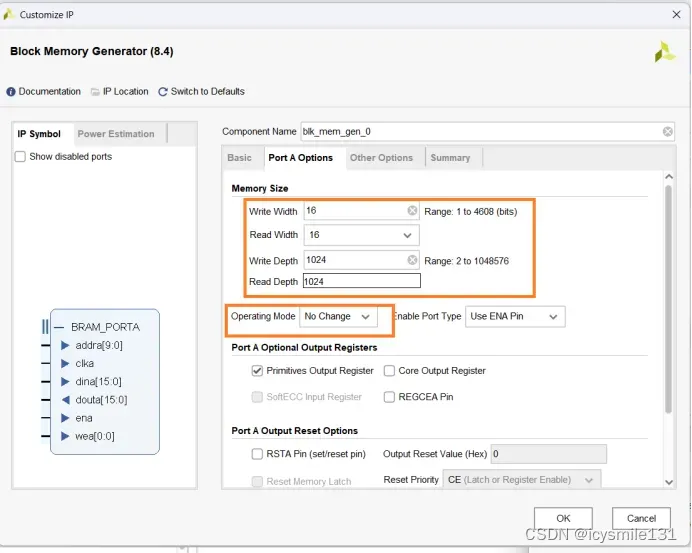

添加RAM IP到工程,如下图:

RAM IP配置如下(其他默认):

[

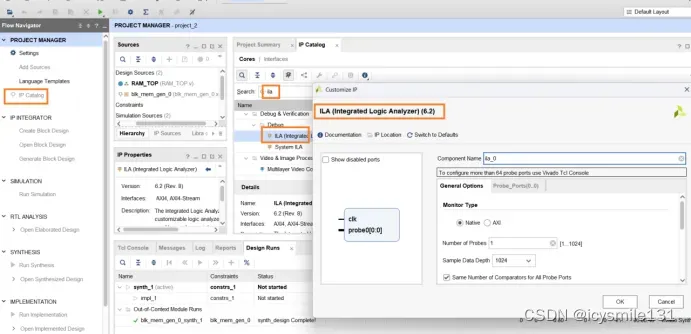

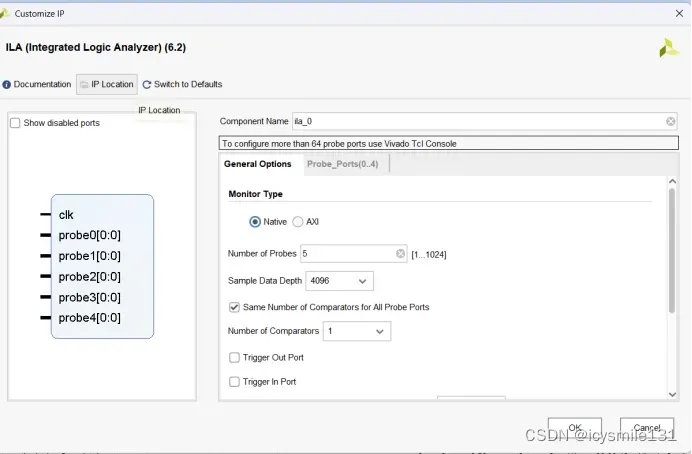

添加ILA IP到工程,如下图:

ILA IP配置如下(其他默认):

module RAM_TOP(

input clk_p,

input clk_n,

input rst

);

wire clk;

IBUFDS #(

.DIFF_TERM("FALSE"),

.IBUF_LOW_PWR("TRUE"),

.IOSTANDARD("DEFAULT")

) IBUFDS_inst(

.O(clk),

.I(clk_p),

.IB(clk_n)

);

wire ena;

reg [0:0] wea;

reg [9:0] addra;

reg [15:0] dina;

wire [15:0] douta;

assign ena = rst;

reg [2:0] ram_state;

always @(posedge clk or negedge rst)

if(!rst) begin

ram_state <= 'b0;

wea <= 'b1;

addra <= 'b0;

dina <= 'b0;

end

else begin

case(ram_state)

'b0: begin

if(addra < 1023) begin

wea <= 'b1;

addra <= addra + 'b1;

dina <= dina + 'b1;

end

else begin

ram_state <= 'b1;

wea <= 'b0;

addra <= 'b0;

dina <= 'b0;

end

end

'b1: begin

if(addra < 1023) begin

wea <= 'b0;

addra <= addra + 'b1;

end

else begin

ram_state <= 'b0;

wea <= 'b1;

addra <= 'b0;

dina <= 'b0;

end

end

default: begin

ram_state <= 'b0;

wea <= 'b0;

addra <= 'b0;

dina <= 'b0;

end

endcase

end

blk_mem_gen_0 u0 (

.clka(clk), // input wire clka

.ena(ena), // input wire ena

.wea(wea), // input wire [0 : 0] wea

.addra(addra), // input wire [9 : 0] addra

.dina(dina), // input wire [15 : 0] dina

.douta(douta) // output wire [15 : 0] douta

);

ila_0 u1 (

.clk(clk), // input wire clk

.probe0(ena), // input wire [0:0] probe0

.probe1(wea), // input wire [0:0] probe1

.probe2(addra), // input wire [9:0] probe2

.probe3(dina), // input wire [15:0] probe3

.probe4(douta) // input wire [15:0] probe4

);

endmodule

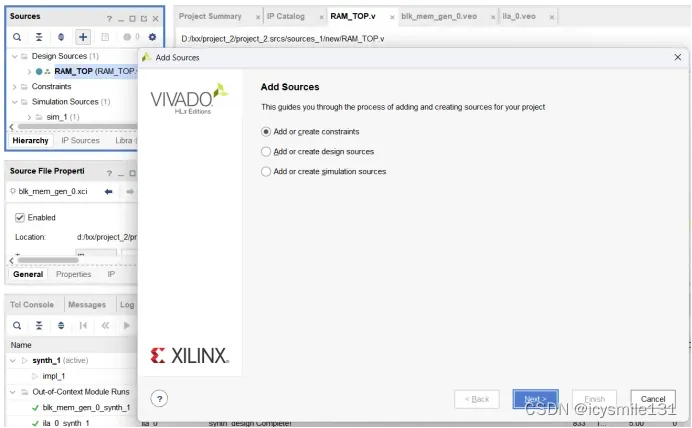

2、添加管脚约束文件

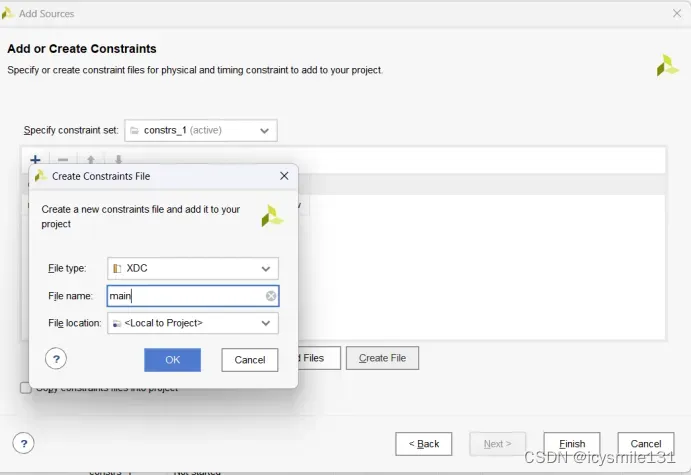

在Design Sources中选择“+”,在“Add Sources”对话框中选择添加约束文件main.xdc。

文件类型默认为xdc。

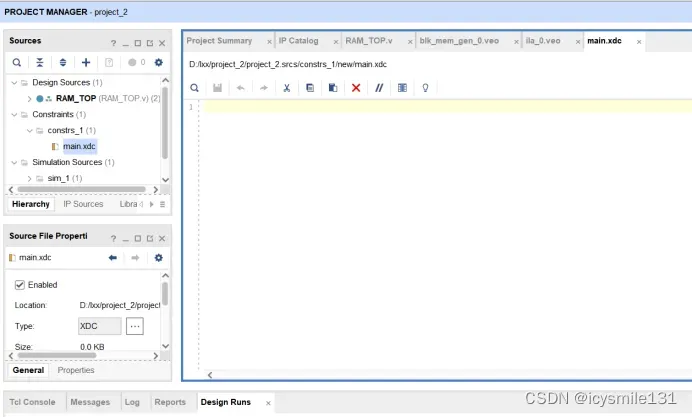

在Design Sources中点击main.xdc进行编辑。

约束文件代码如下:

set_property IOSTANDARD lVDS [get_ports clk_p]

set_property PACKAGE_PIN C8 [get_ports clk_p]

set_property IOSTANDARD SSTL135 [get_ports rst]

set_property PACKAGE_PIN G9 [get_ports rst]

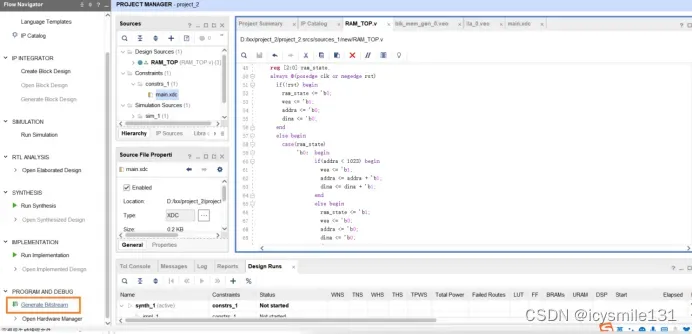

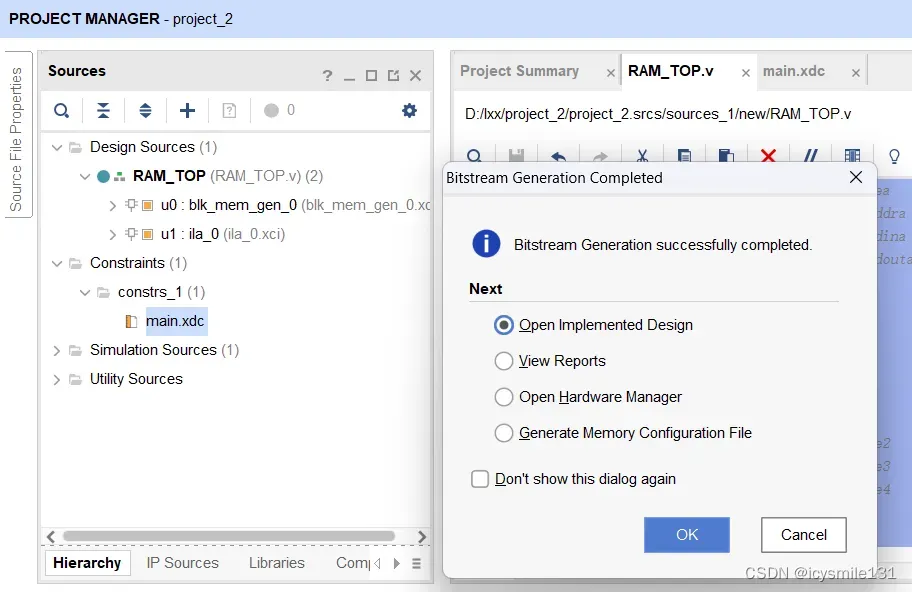

3、编译并生成bit文件

点击Flow Navigator中的Generate Bitstream,等待生成bit文件。

bit文件生成成功。

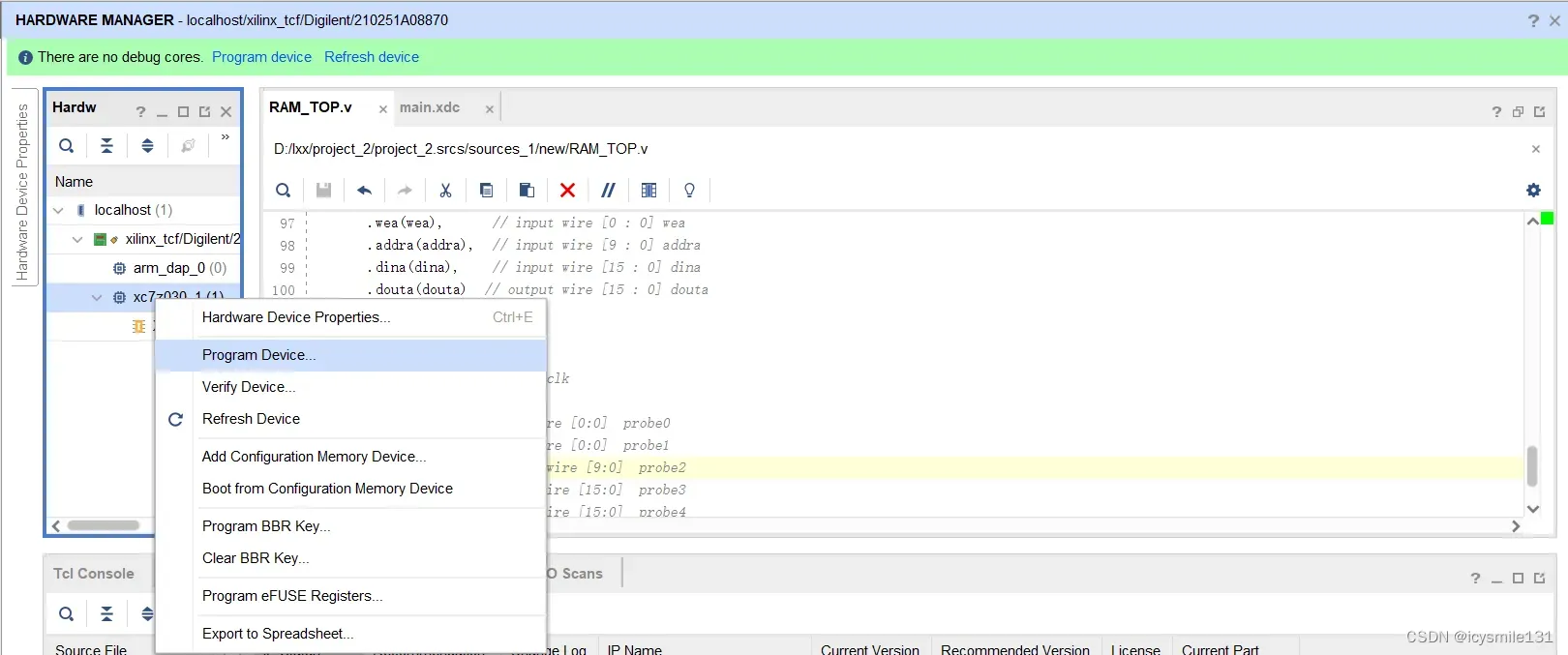

4、加电测试

连接仿真器,给设备加电。

注意:为了延长仿真器的使用时间,尽可能不要带电插拔仿真器。

点击Flow Navigator——>PROGRAM AND DEBUG——>Open Hardware Manager——>Open Target,在弹出界面上点击Auto Connect。

在HardWare的xc7z030_1上点击右键,选择Program Device…

选择刚刚生成的bit文件和ltx文件,点击Program。

下载完成后,自动跳出ILA界面,点击界面上的“》”即可开始抓取信号。

版权声明:本文为博主作者:icysmile131原创文章,版权归属原作者,如果侵权,请联系我们删除!

原文链接:https://blog.csdn.net/u011565038/article/details/137906579