Vivado中ILA(集成逻辑分析仪)的使用

一、写在前面

在FPGA设计上板过程中,如果出现问题难以定位具体问题的位置和原因,要观察一些信号的波形,可以使用ILA来捕获关键信号,以便分析问题并快速定位其原因。ILA(Integrated Logic Analyzer),集成逻辑分析仪,与Quqartus 中的 SignalTap II 作用类似。

二、ILA(Integrated Logic Analyzer)的使用

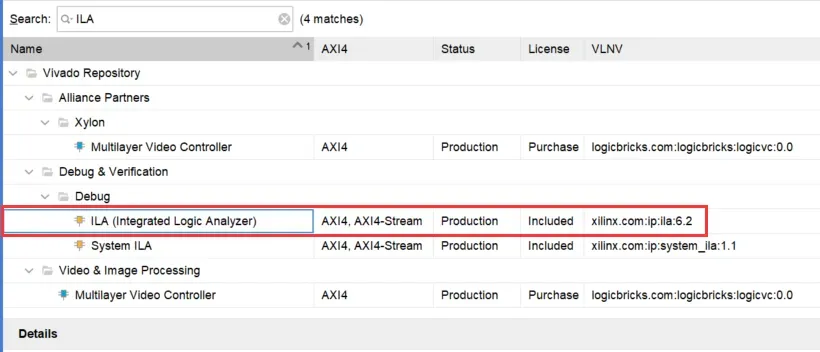

2.1 ILA查找

在IP Catalog中搜索ILA,可以找到该IP核,双击对该IP核进行配置。

2.2 ILA配置

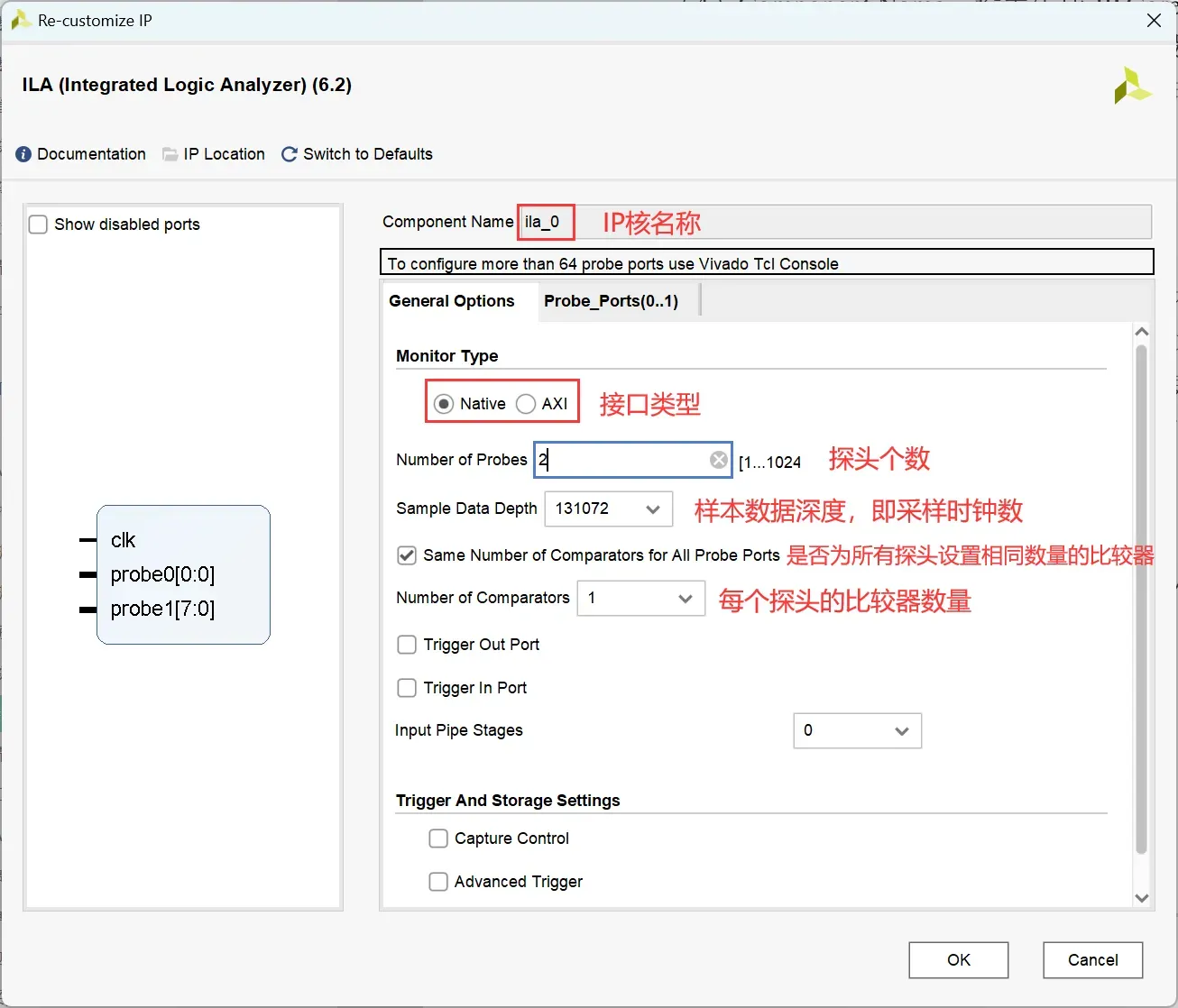

接下来可以对ILA进行配置,界面如下。

这里,我们仅对Native接口进行讲解,关于AXI接口的ILA使用,在这里不进行过多讲解。

2.2.1 General Options

- Component Name:IP核的名称,可根据需求进行设置;

- Native/AXI:接口类型

- Number of Probes:探头的数量,即需要查看的信号个数

- Sample Data Depth:样本数据深度,即采样的时钟个数,也可以认为显示在窗口中的时钟数量,最小为1024=

,最大为131072=

。假如设置该值为024,则在窗口中可以观察到1024个时钟周期的数据;

- Same Number of Comparators for All Probe Ports:是否为所有探头设置相同数量的比较器;

- Number of Comparators:该选项仅在勾选Same Number of Comparators for All Probe Ports时才会有,表示为每个探头设置的比较器数量;

- Trigger Out Port:触发输出端口,可用于 ILA 模块的级联或一些高级功能;

- Trigger In Port:触发输入端口,可用于手工设置添加触发信号或进行 ILA 模块的级联或一些高级功能;

- Input Pipe Stages:需观察信号打拍次数,可设置数值 0~6,一般情况下,采样时钟和探测信号是一个时钟域下,这里可以默认设置为 0 即可;

- Capture Control:勾选后可在调试的设置窗口中进行对Capture mode的设置,如果不勾选后面有关 Capture mode 就不可修改;

- Advanced Trigger:勾选后可在调试的设置窗口进行对 Trigger mode 的设置,如果不勾选后面有关 Trigger mode 就不可修改;

在这里有一个点值得关注:上述中比较器是什么?

在使用探头观察信号的值时,我们可以设置需要观察的信号在什么时候在窗口中显示波形?即什么是时候抓取信号的波形?比如需要观察一个8bit位宽的变量data,在其值等于8’hbb时,在窗口中显示其波形,则只需要一个比较器,当data==8’hbb为真时,抓取data波形,并在波形窗口中显示。那么如果需要使其值在区间8‘h11到8’hbb区间内时,在窗口中显示其波形,则需要设置两个比较器。

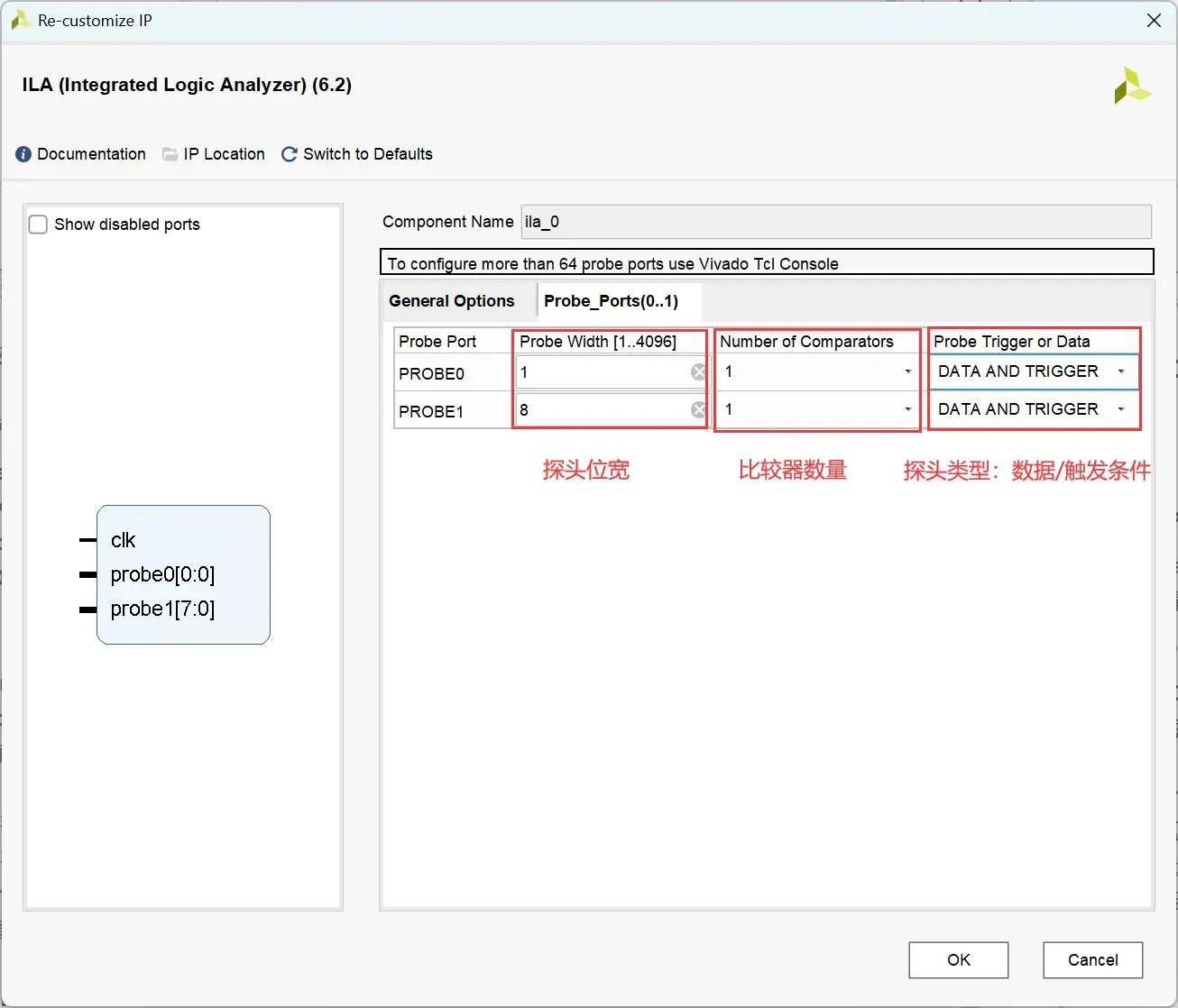

2.2.2 Probe Ports

在Probe Ports界面,可以对每个探头进行详细设置,可以设置每个探头的探头位宽、比较器数量、探头类型,如下图所示。

- Probe Width:探头的宽度,即需要观察的信号的位宽;

- Number of Comparators:比较器数量。如果在前面勾选了Same Number of Comparators for All Probe Ports,为所有探头设置了相同的比较器数量,那么在这里则不可设置;如果在前面没有为所有探头设置相同的比较器数量,则在这里就可以为每个探头设置不同的比较器数量。

- Probe Trigger or Data:探头作为触发条件还是数据;(DATA AND TRIGGER:既可作为触发条件,也可作为数据;DATA:仅作为数据;TRIGGER:仅作为触发条件;)

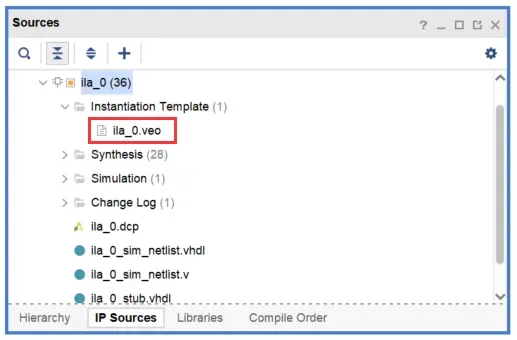

三、ILA调用

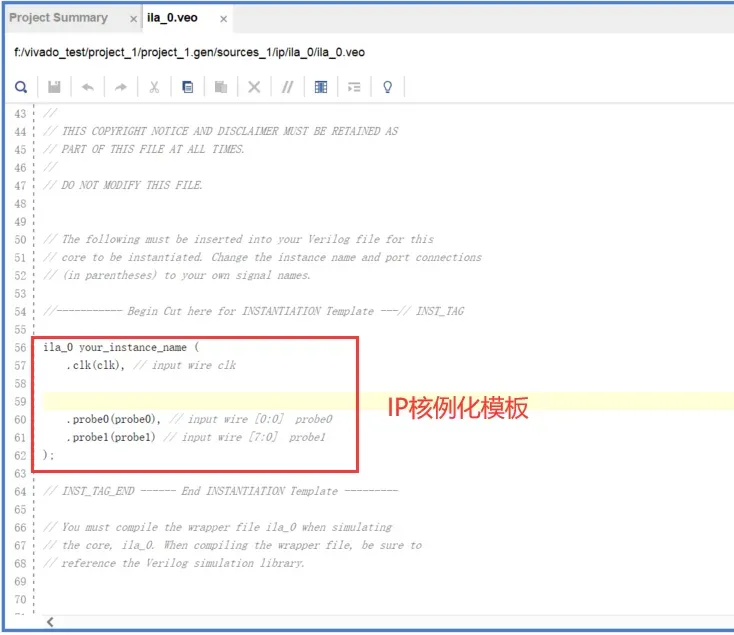

在配置好ILA IP核后,在IP Sources中可以看到已经生成的IP核,在Instantiation Template可以看到IP核例化模板,如下图所示。

四、ILA联调

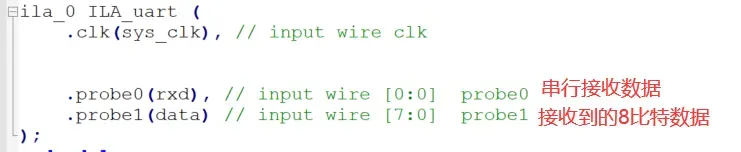

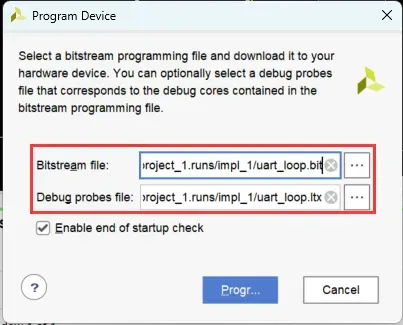

在这里,以串口回环为例,观察PC发送的串行数据rxd和FPGA开发板接收到的8bit数据。将生成比特流文件后将.bit文件和.ltx文件写入FPGA开发板。

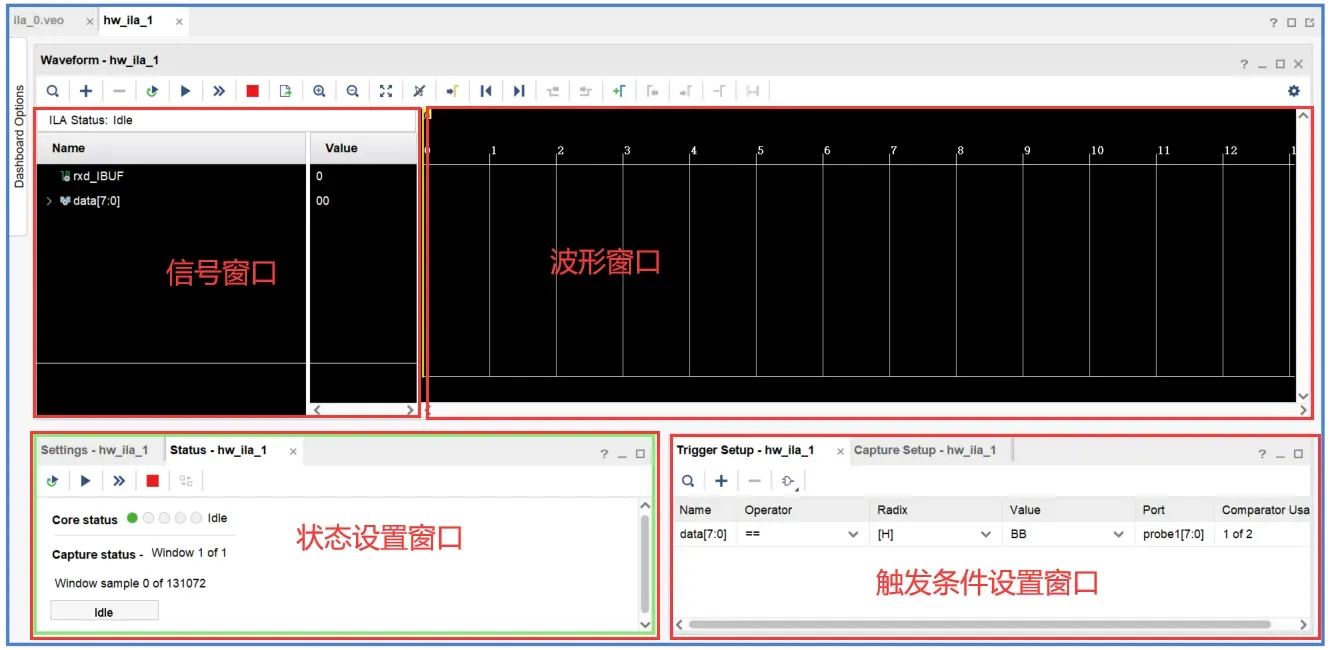

然后在调试窗口中,可以看到4个窗口:信号窗口、波形窗口、状态设置窗口和触发条件设置窗口。

4.1 信号窗口

在信号窗口中可以看到之前设置为DATA的探头信号,可以对其进行删减。

4.2 波形窗口

在波形窗口中,可以观察捕获的信号波形。

4.3 状态窗口

在状态窗口中,可以看到当前的状态。

4.4 设置窗口

在设置窗口中,可以对波形窗口显示的内容进行设置。

- Number of windows:显示窗口个数,默认为 1;

- Window data depth:窗口显示数据深度,最大可以设置为Sample Data Depth Sample Data Depth为IP核配置时配置的数据深度。(这里需要注意的是:Sample Data Depth = Number of windows X Window data depth)

- Trigger position in window:设置触发位置在窗口波形中显示的位置,比如前面设置的样本数据深度Sample Data Depth为131072,那么想要设置触发位置位于波形窗口的中间,则设置为131072/2=65536;

- Refresh rate:连续触发模式下,相邻触发之间的刷新时间;

4.5 触发条件设置窗口

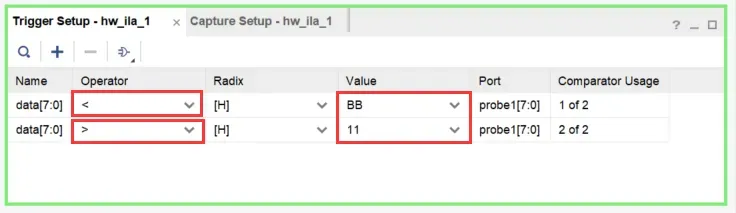

在触发条件设置窗口中,可以设置触发的条件,假如要观察8bit信号data大于8’h11且小于8’hBB,则这里设置2个比较器,一个比较器设置在Data大于8’h11时触发,输出高电平,另外一个比较器设置在Data小于8’hBB时触发,输出高电平。

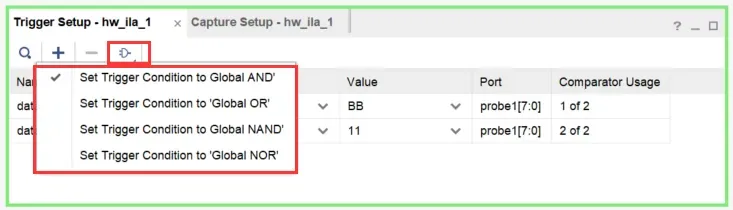

同时,可以设置这个几个触发条件之间的关系,可以设置为:与(AND)、或(OR)、与非(NAND)、或非(NOR)。在这里,我们设置为与(AND)。

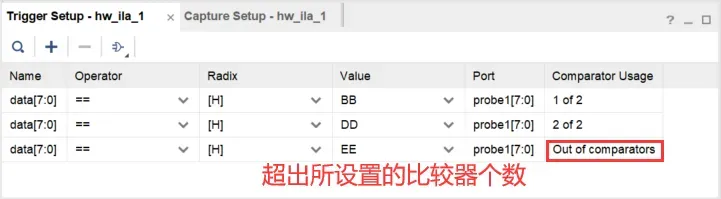

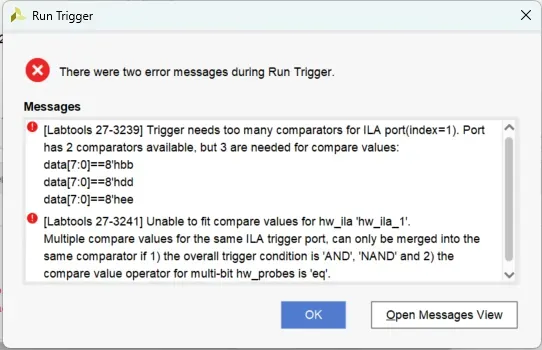

在这里有一点需要注意:对于单个观察信号,所使用的比较器个数不可以超过在ILA IP核配置时所设置的比较器个数(Number of Comparators),如果使用的个数大于所设置的比较器个数,则在触发条件设置窗口中可以看到提示Out of comparators,表示在这里使用的比较器个数超过我们前面设置的比较器个数。如果运行调试,则会出现报错!!!

4.6 联合调试

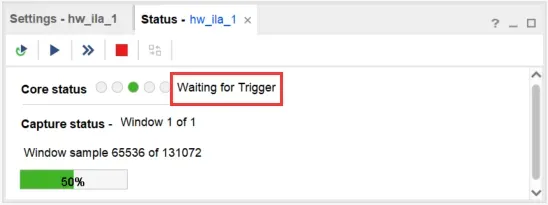

在设置好以上的选项后,运行调试,查看状态窗口中,可以看到当前状态为等待触发状态。

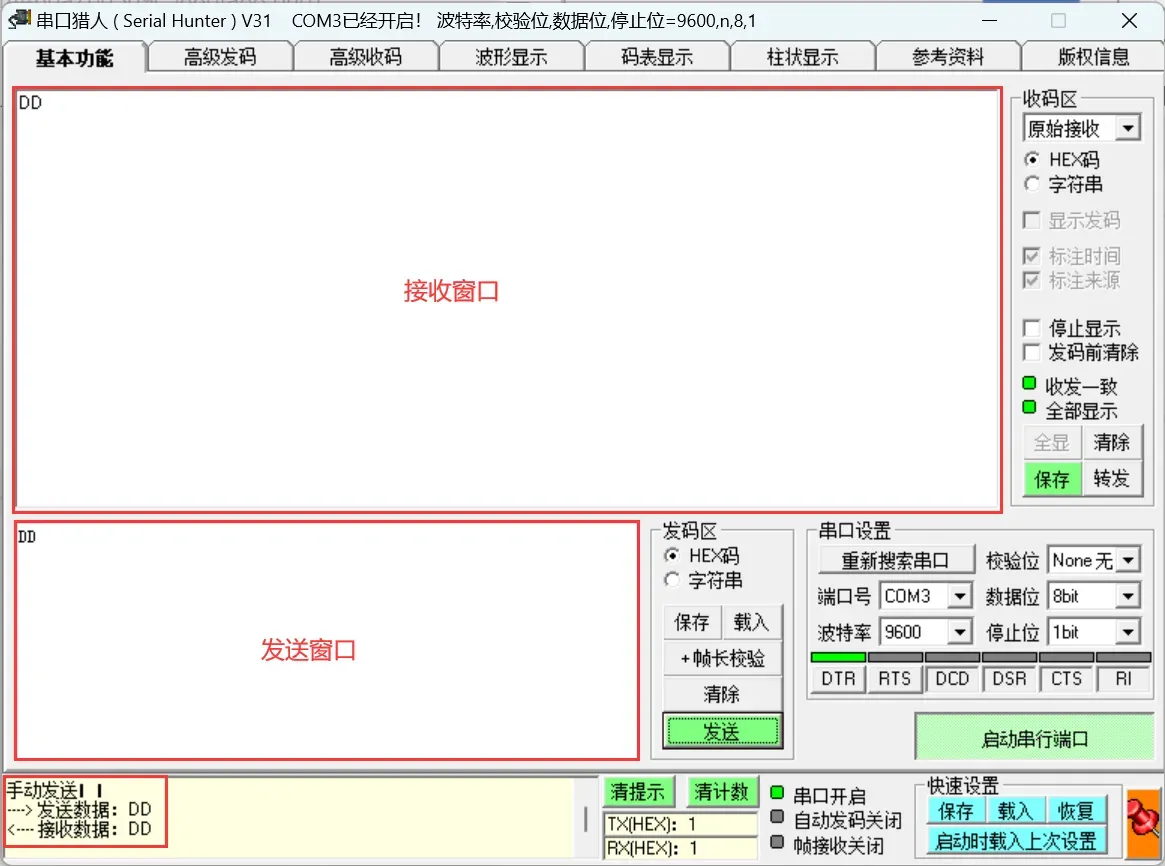

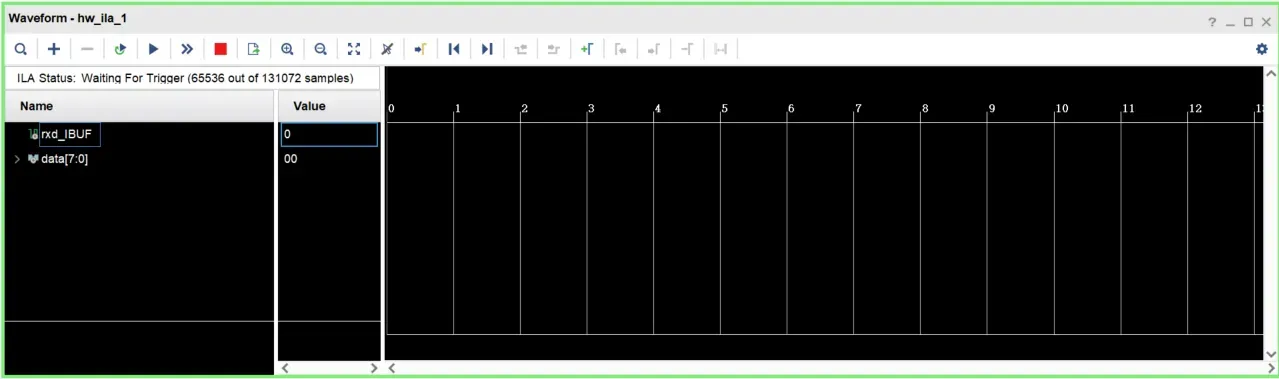

然后在串口助手中,发送数据8’hDD,再观察ILA调试窗口中波形,由于8’hDD不在区间[ 8’h11 , 8’hDD ]内,所以并未触发条件,波形窗口中也就无任何波形。

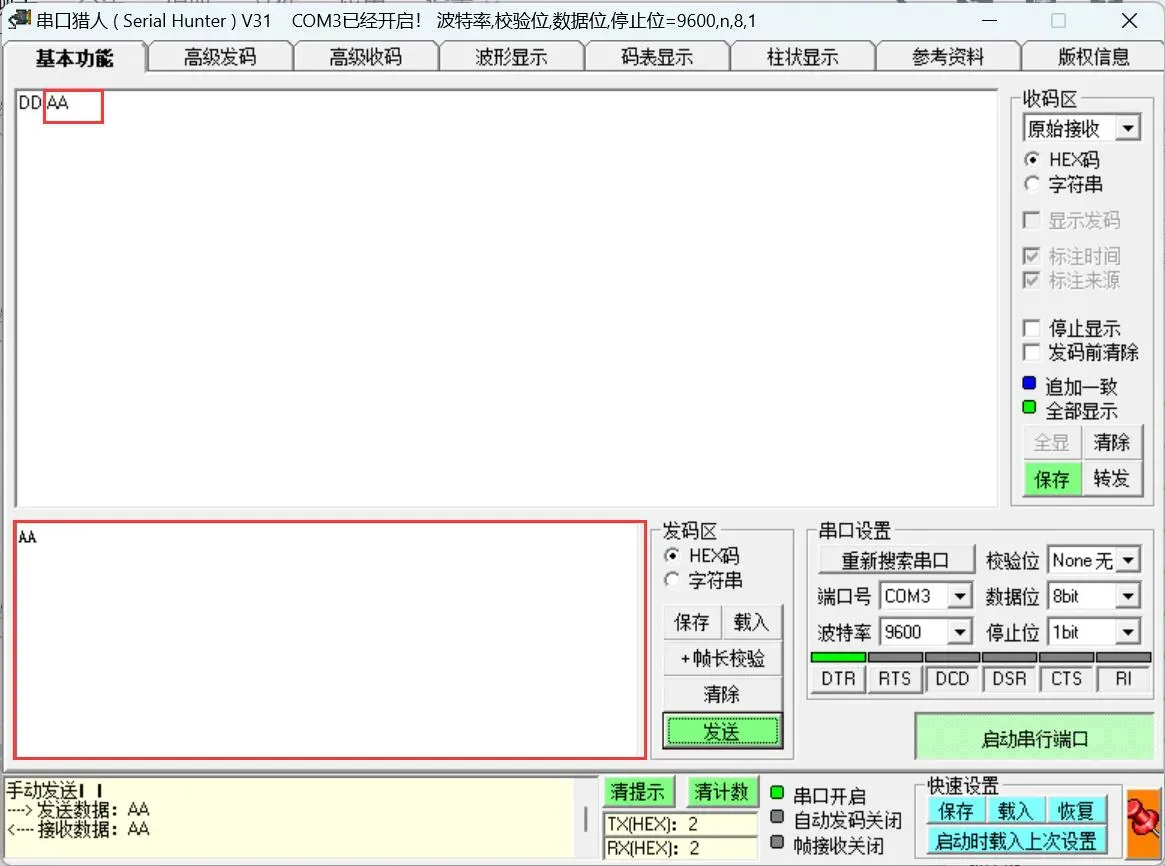

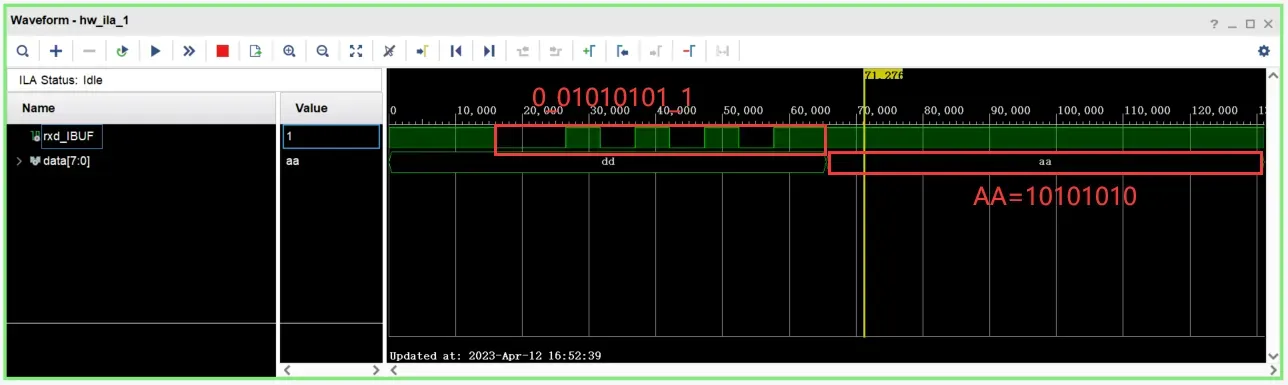

然后在串口助手中,再发送数据8’hAA,再观察ILA调试窗口中波形,由于8’hAA在区间[ 8’h11 , 8’hDD ]内,所以并触发了捕获条件,波形窗口中也可以看到接收到Data为8’hAA,触发时位于波形窗口的中间。

在这里可以看到,接收到8’hAA的上一个数据为8’hDD,同时可以看到我们接收到的串行数据为0_01010101_1,最高位0为起始位,最低位1为停止位,中间的8bit数据01010101为接收到的数据。由于串口发送是先发送数据的LSB,最后发送数据的MSB,所以实际上发送端发送的数据为10101010,即AA,与我们接收端接收到的数据data一致。

五、写在最后

在本文中,学习了Vivado中集成逻辑分析仪(Integrated Logic Analyzer,ILA)的使用,结合串口回环程序进行波形捕获实验,观察串行数据传输是否正确,这里只是对ILA的使用进行简单的演示,在具体设计中应根据项目需求进行配置。

好了,上面就是关于Vivado中ILA IP核的一些学习笔记,如果有疑义的地方欢迎评论区友好探讨学习!!!!!

文章出处登录后可见!