本原创教程由深圳市小眼睛科技有限公司创作,版权归本公司所有,如需转载,需授权并注明出处

一、Pango Design Suite 简介

Pango Design Suite 简称 PDS,是一款专用于紫光同创 FPGA 开发的 EDA 工具,其主要功 能包括设计输入、综合、仿真、实现和位流生成,并能够借助一些常用的第三方软件(主要 是逻辑综合工具和仿真工具)完成 FPGA 全流程开发。 本快速使用手册将基于 Compa 系列的 PGC2KG 介绍基本操作流程,无特殊说明均采用默认 选项配置。主要包括一下章节: 1.新建工程 2.Compile 3.Synthesize 4.Device Map 5.添加约束 6.Place&Route 7.Generate Bitstream 8.下载位流文件 9.复用管脚设置 10.Modelsim 与 PDS 联合仿真 11.Debugger

二、基本操作流程

a.新建工程

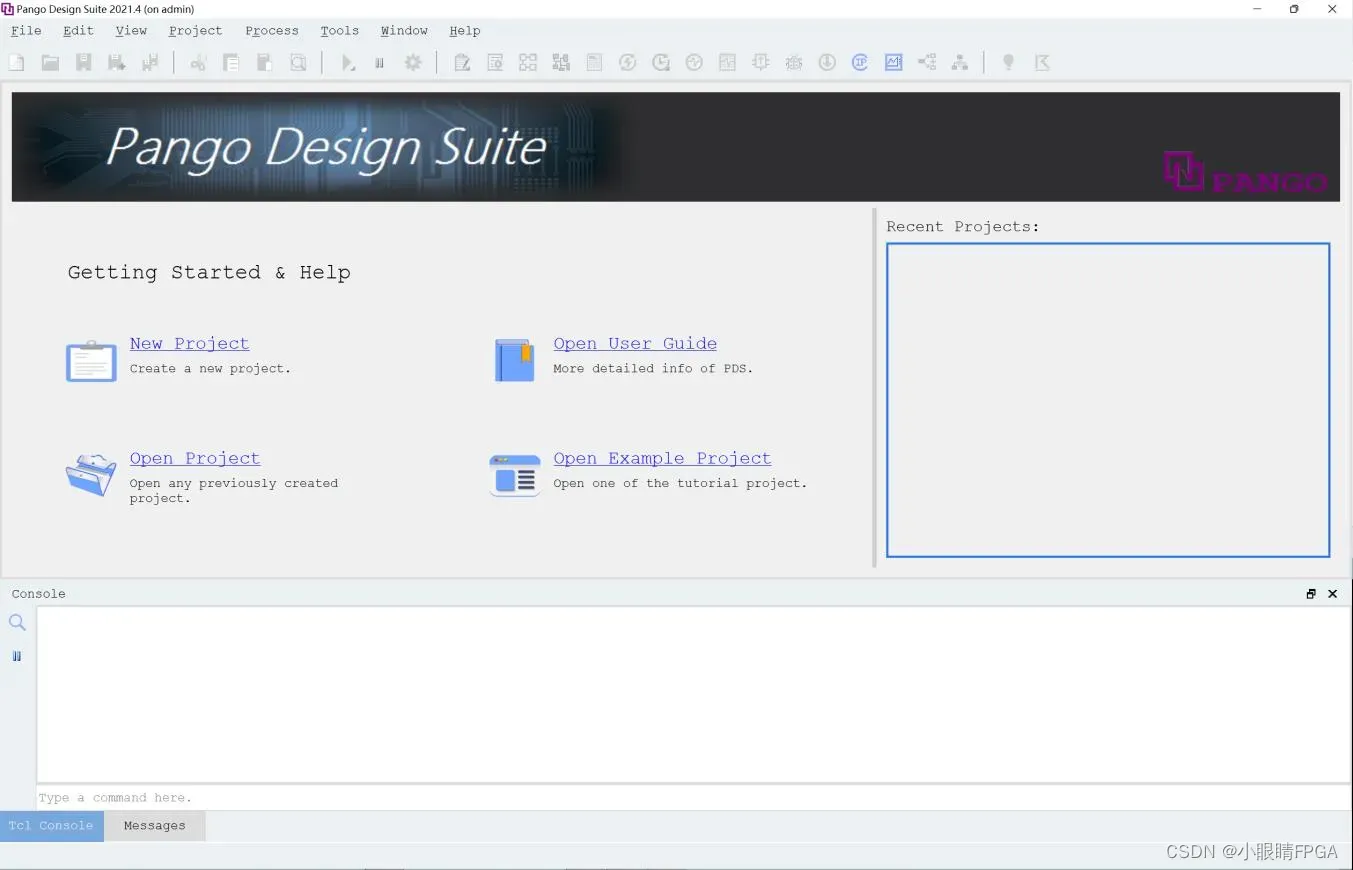

1.启动 PDS 软件 双击桌面 PDS 快捷方式,可启动软件,如下图所示:

PDS 桌面快捷方式

(不同版本会有不同版本名称,具体名称以发布版本为准)

PDS 软件开启后界面如下图所示:

PDS 软件开启后界面

2. 通过打开新建工程向导【New Project】,然后对其设置完成新建工程。

New Project 快捷方式

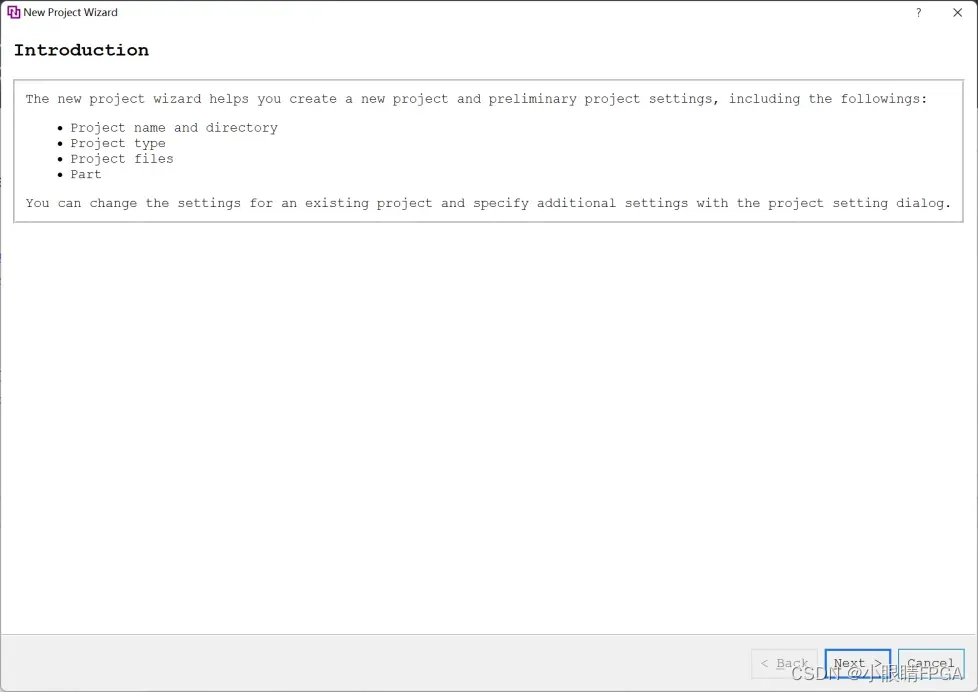

新建工程向导【New Project】,如下图所示:

新建工程向导

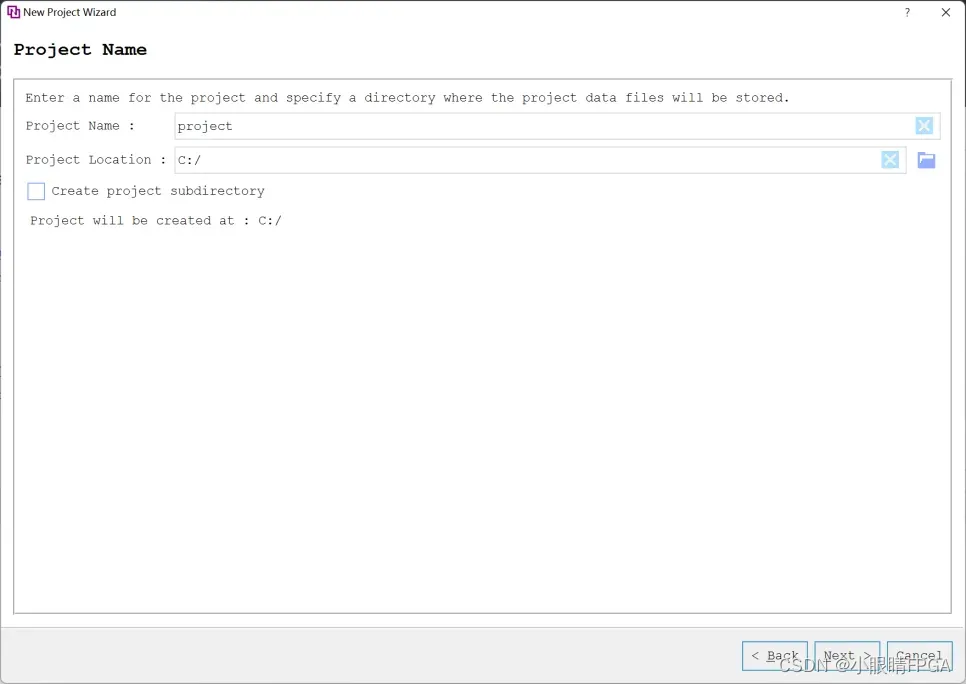

新建工程大致包括设置工程名和工程路径、工程类型、工程文件及器件信息。单击 Next 出现如下界面:

选择工程路径

【Project Name】是工程文件名称,默认为 project。(只允许字母、数字、下划线(_)、 杠(-)、点(.))。

【Project Location】用于选择新工程的工作路径,文件夹名只允许字母、数字、下划 线(_)、杠(-)、点(.)、@、~、,、+、=、#、空格( ),但空格不能出现在路径名首尾,即 工程文件放置的路径。

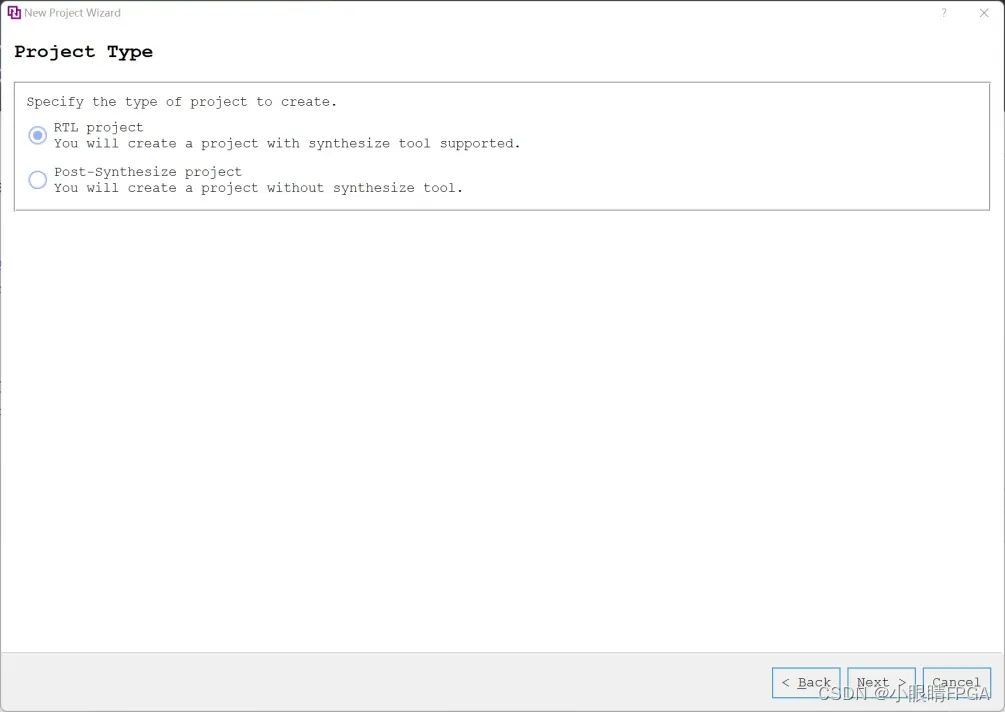

【Create Preject Subdirectory】将工程文件名作为工作目录的一部分。 设置好工程名和工程路径后,单击 Next 出现选择工程类型界面:

【RTL Project】用于创建 RTL 工程。新建的工程可以执行 synthesize,device map, place& route,report timing, report power, generate netlist 及 generate bitstream 等。

【Post-Synthesize Project】用于创建综合后工程。新建的工程可以执行 device map, place& route,report timing,report power, generate netlist 及 generate bitstream 等。

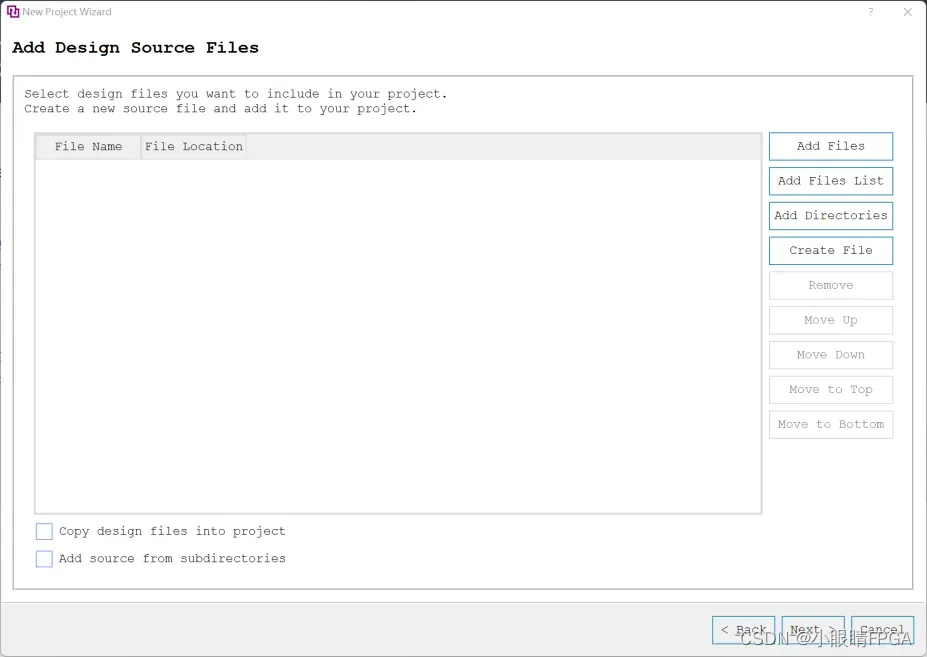

选择好工程类型后,点击 Next 出现添加 rtl 文件界面:

添加 design 文件

该界面可以 Add Files 和 Add Directories 来添加 rtl 源文件及新建 rtl 源文件,以 及调整 rtl 文件编译顺序,Add Files 添加选中的文件,Add Directories 添加选中的文件 夹下所有合适的文件,若勾选了下方的 Add source from subdirecotires 则添加所有的子目 录下合适的文件,也可直接 NEXT 跳过添加文件。

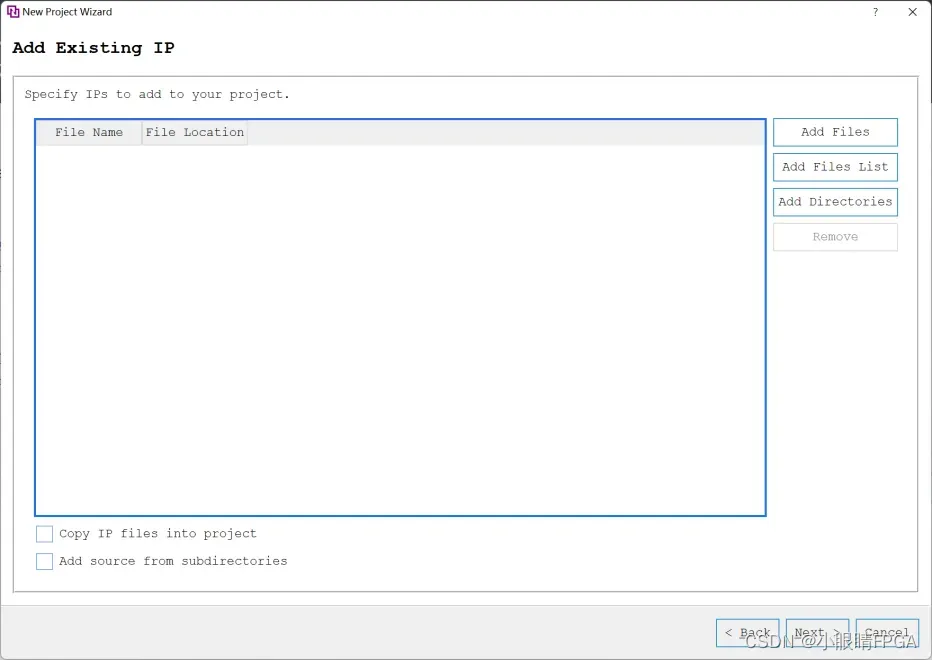

单击 Next 出现添加 IP 界面,IP 界面的 Add Files 与 Add Directories 与上述相同如 下,也可直接 NEXT 跳过添加文件:

添加 IP 文件

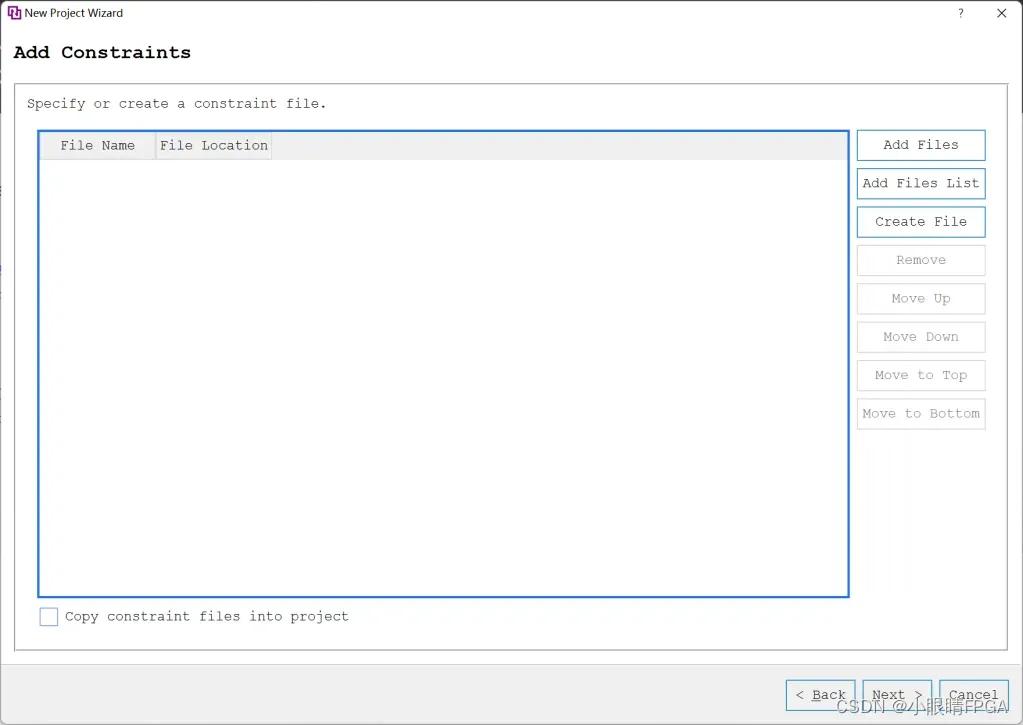

单击 NEXT 出现添加约束界面,也可直接 NEXT 跳过添加文件::

添加约束文件

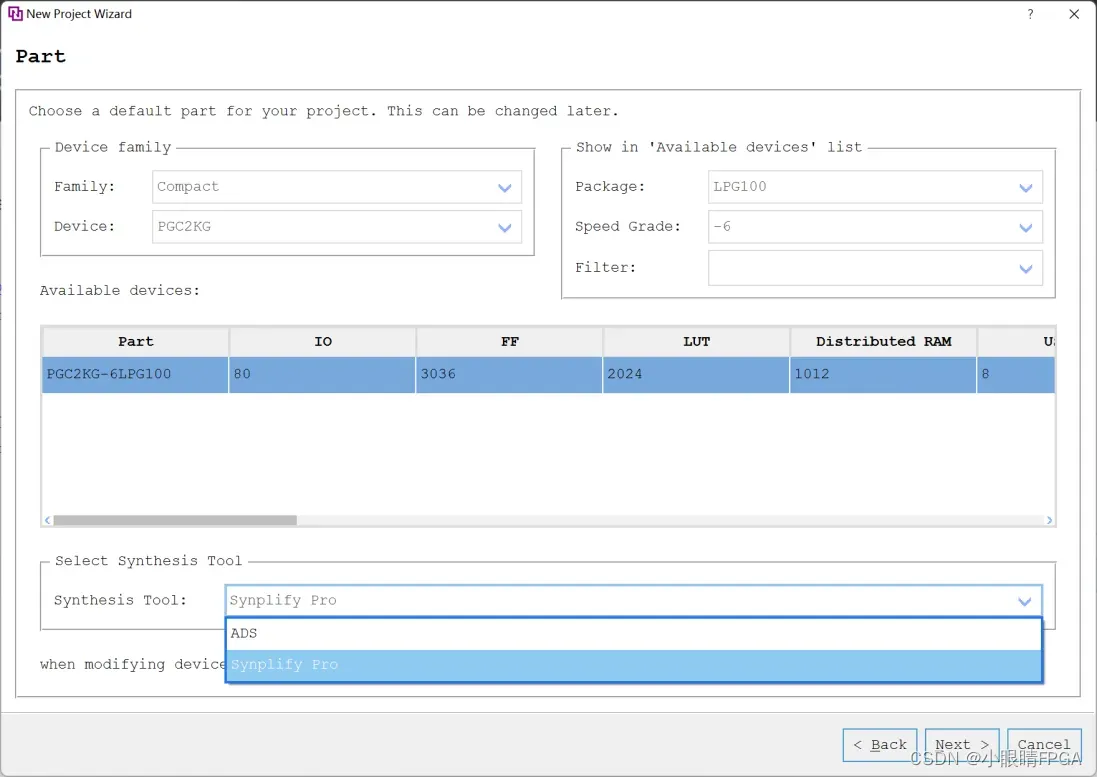

单击 Next 进入器件选择界面,synthesize tool 中可以选择综合工具为 Synplify Pro 或 ADS,本手册以 Compa 系列 PGC2KG-LPG100-6 综合工具 ADS 为例:

选择器件

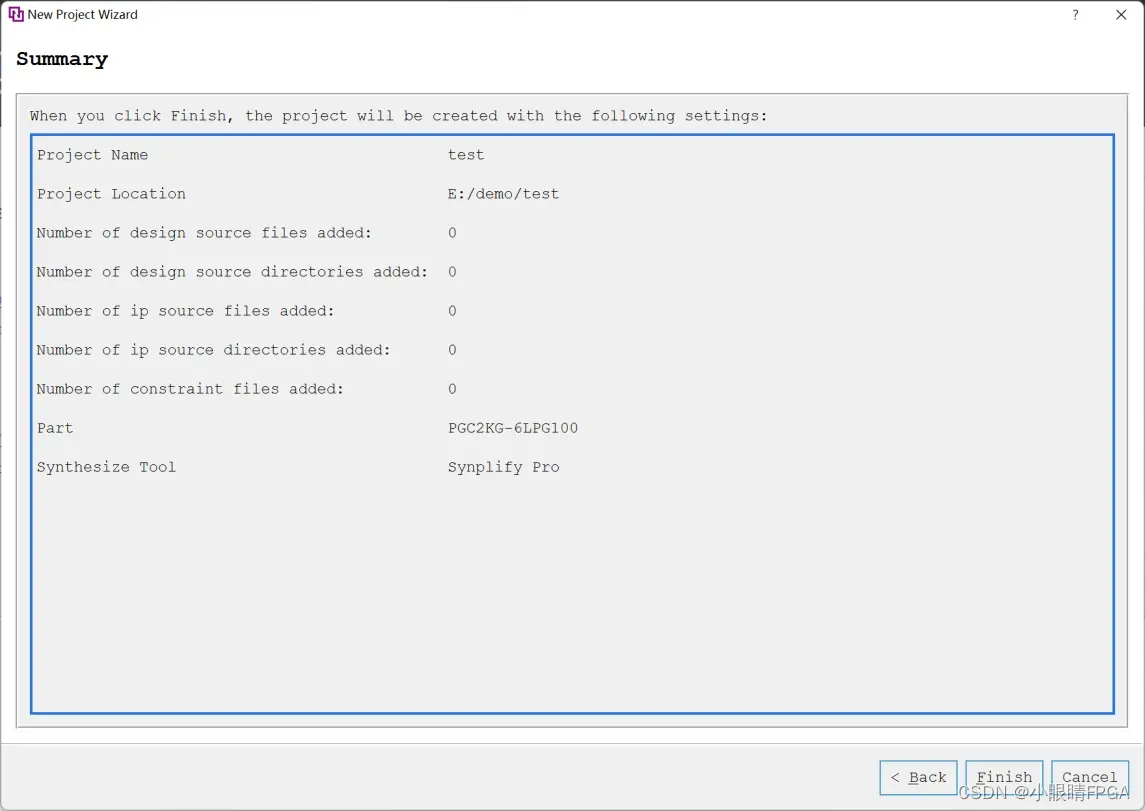

选好器件,单机 NEXT 进入 summary 界面:

新建工程 summary

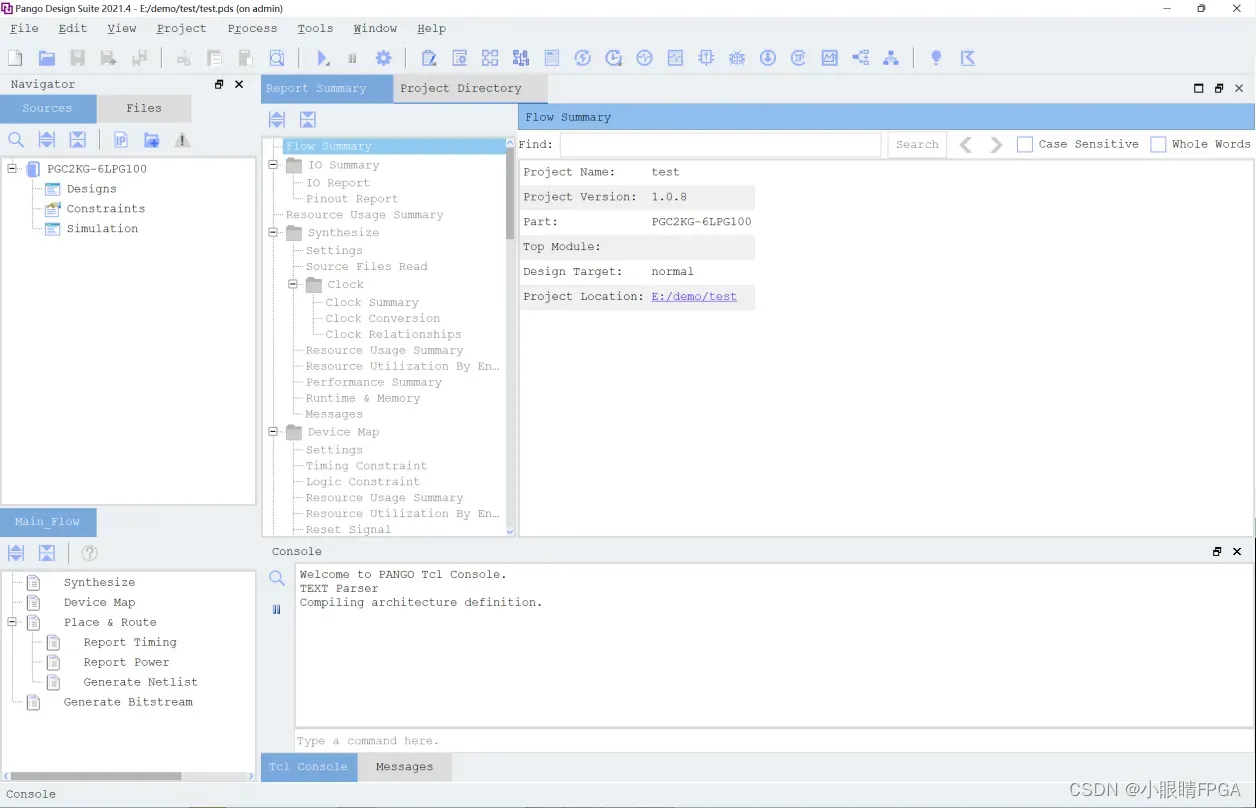

单机 Finish,新建工程结束,软件如下图所示:

新建工程后 PDS 主界面

b. Compile

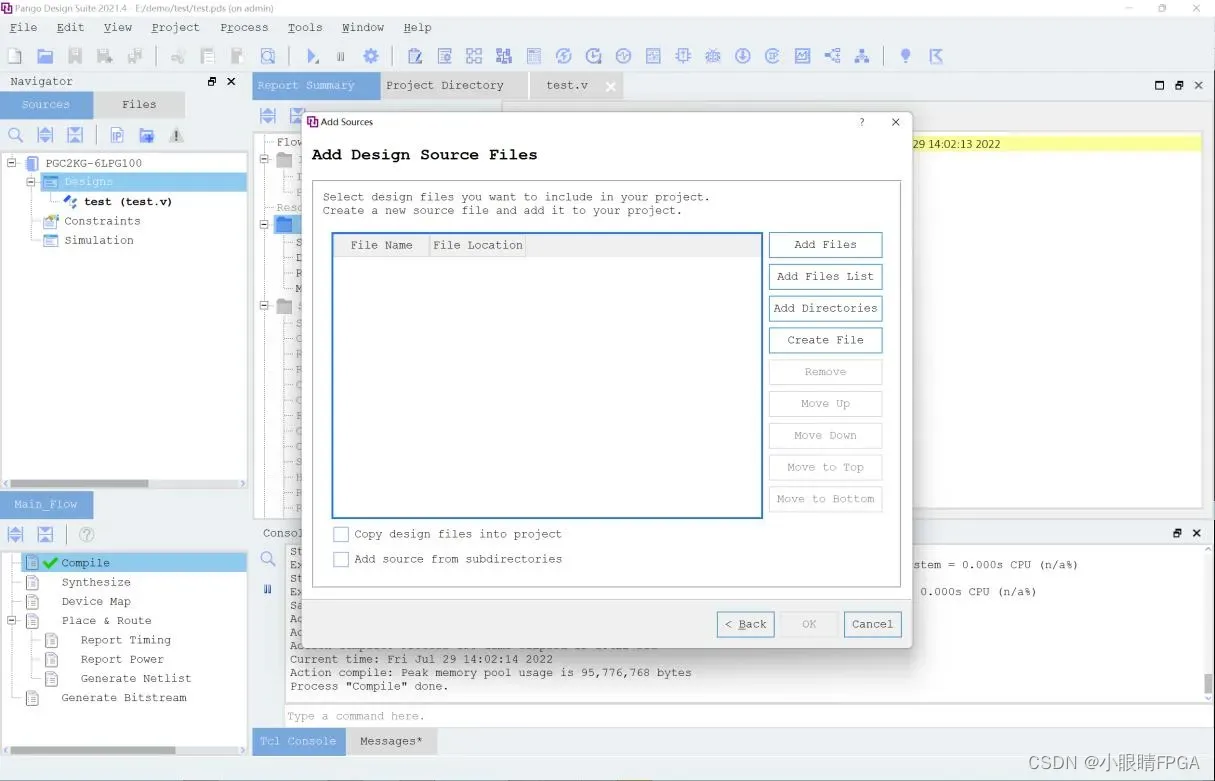

在选择使用 ADS 综合工具时,并按照上文添加综合前.V 文件,才会有该步骤。未添加.V 文件可双击 Designs 添加或新建.V 文件,如下图所示:

添加或新建 Designs 文件

可采用以下方式运行 Compile 流程:

(1)双击 Flow 中的 Compile 进行综合;

(2)右击 Compile 点击 Run 进行综合;

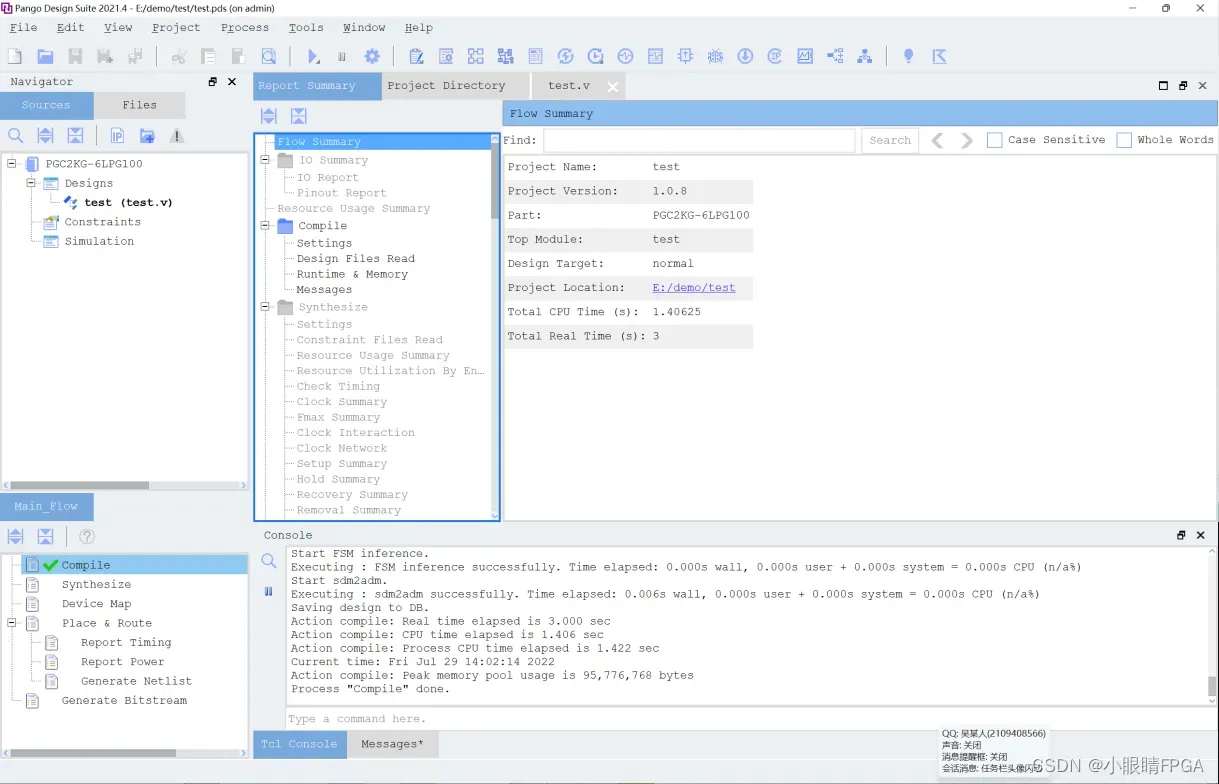

完成 Compile 操作后,会看到下图所示:

完成 Compile 界面

三、Synthesize

运行 Synthesize 流程有以下四种方式可以实现:

(1)双击 Flow 中的 Synthesize 进行综合;

(2)右击 Synthesize 点击 Run 进行综合;

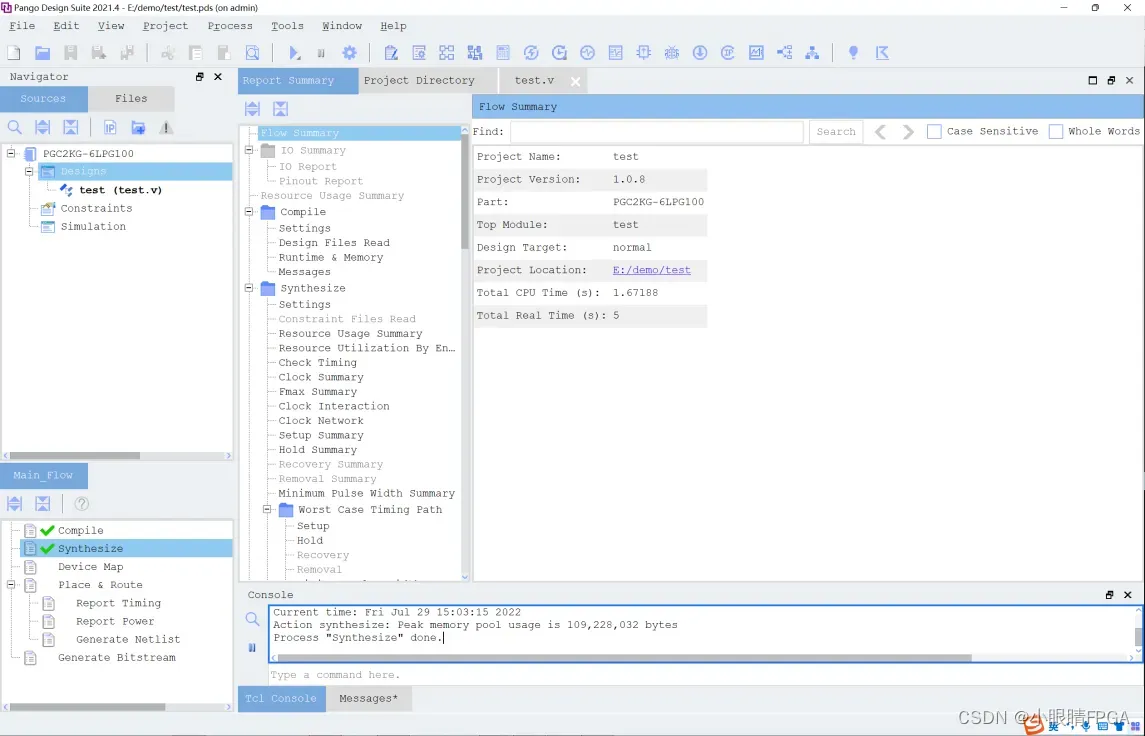

完成 Synthesize 操作后,会看到下图所示:

完成 Synthesize 界面

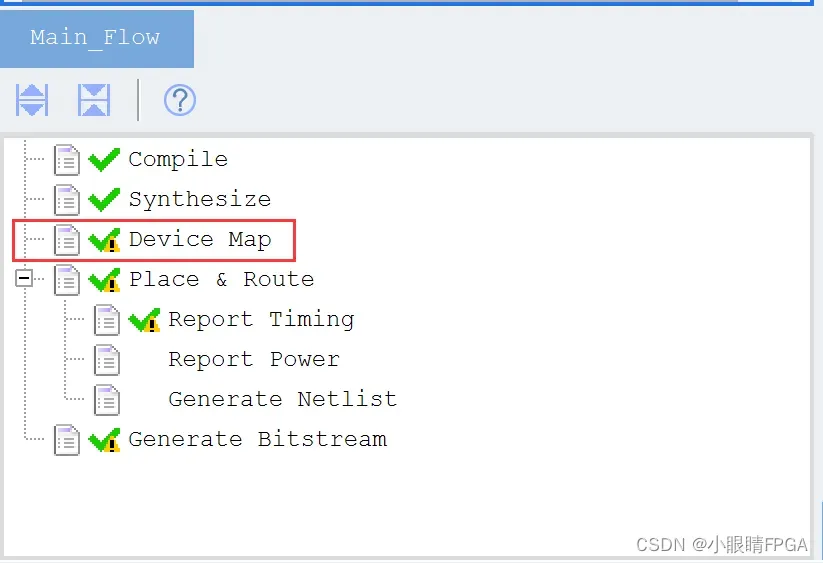

四、Device Map

Device Map 的主要作用是将设计映射到具体型号的子单元上(LUT、FF、Carry 等)。运 行 Device Map 流程有以下方式可以实现:

(1)直接双击 Device Map;

(2)右击 Device Map 点击 Run;

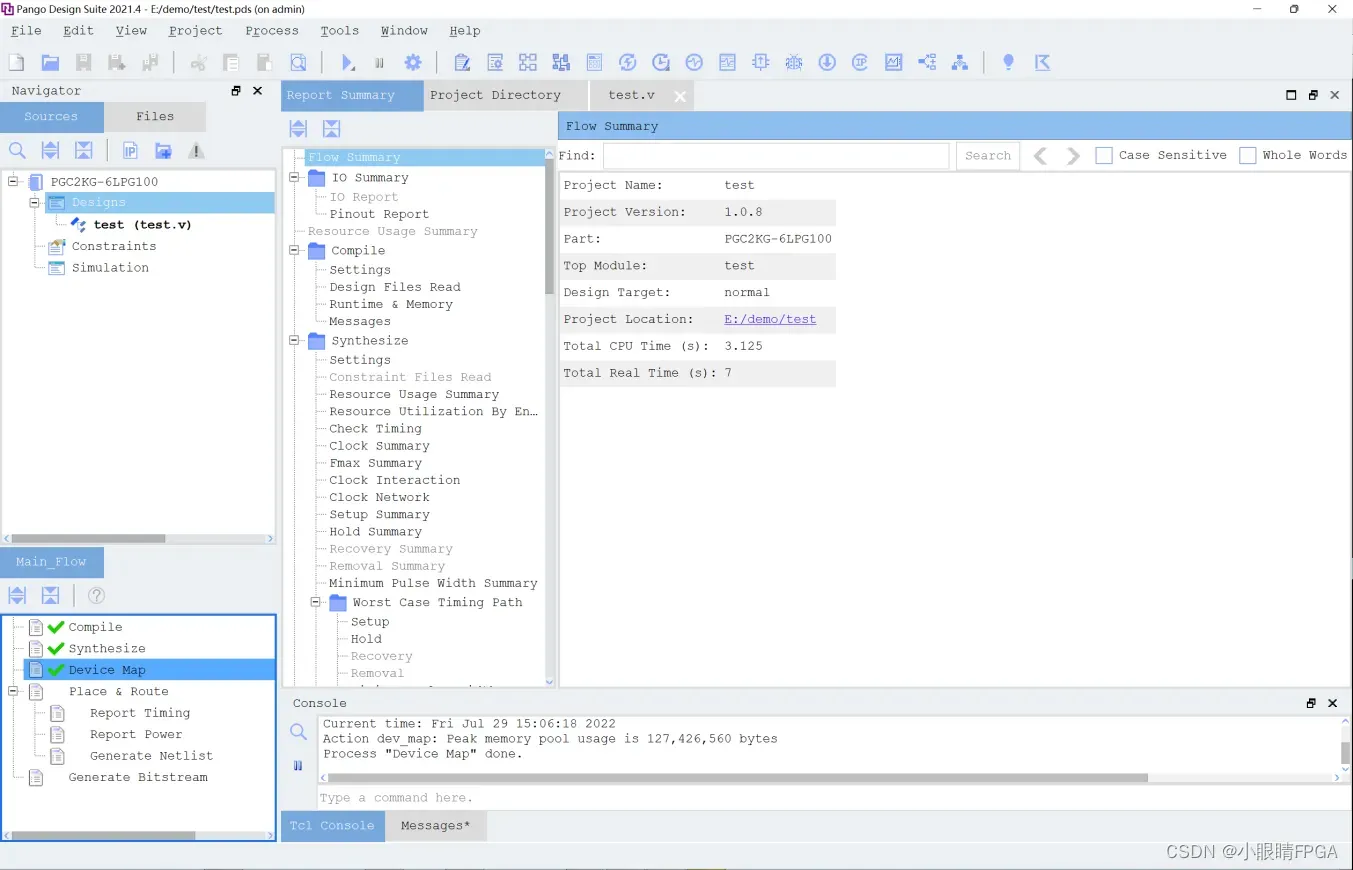

完成 Device Map 操作后,会看到下图所示:

五、添加约束

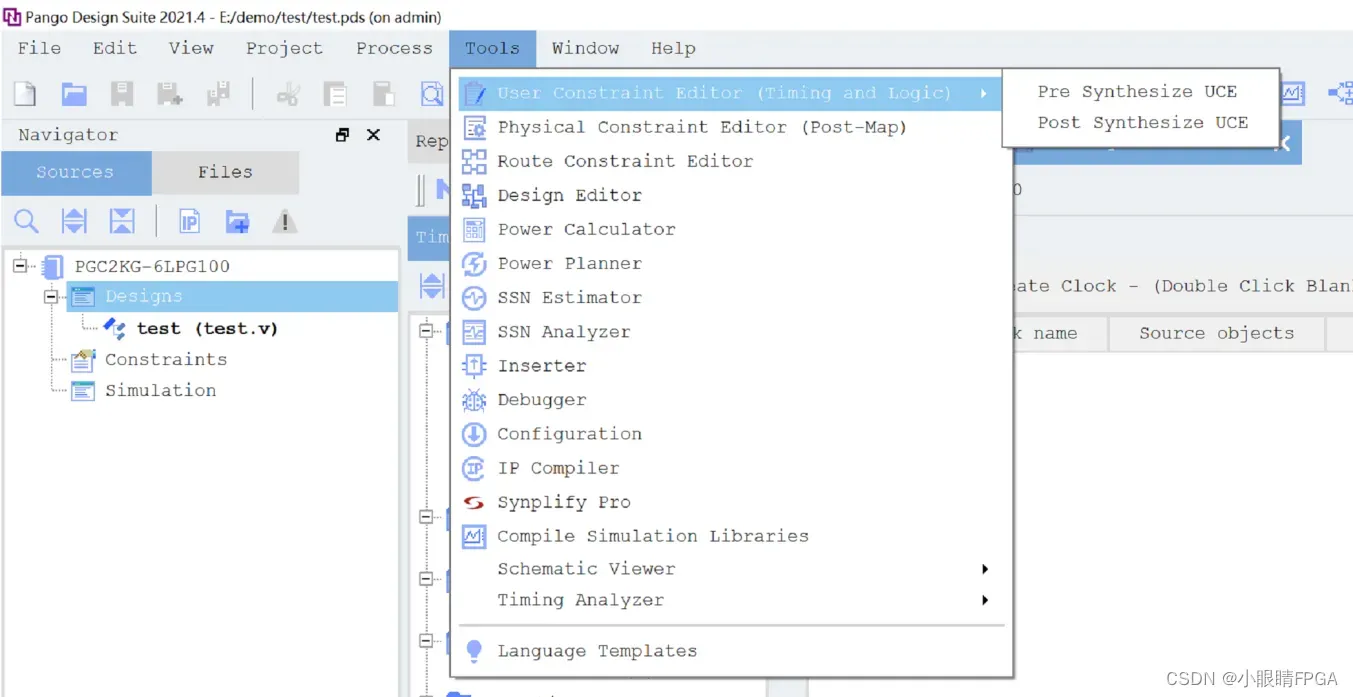

点击 Tools 选择 User Constraint Editor(Timing and Logic)或者点击工具栏图标 User Constraint Editor(Timing and Logic),如下图所示。

Tools 下的 User Constraint Editor(Timing and Logic)

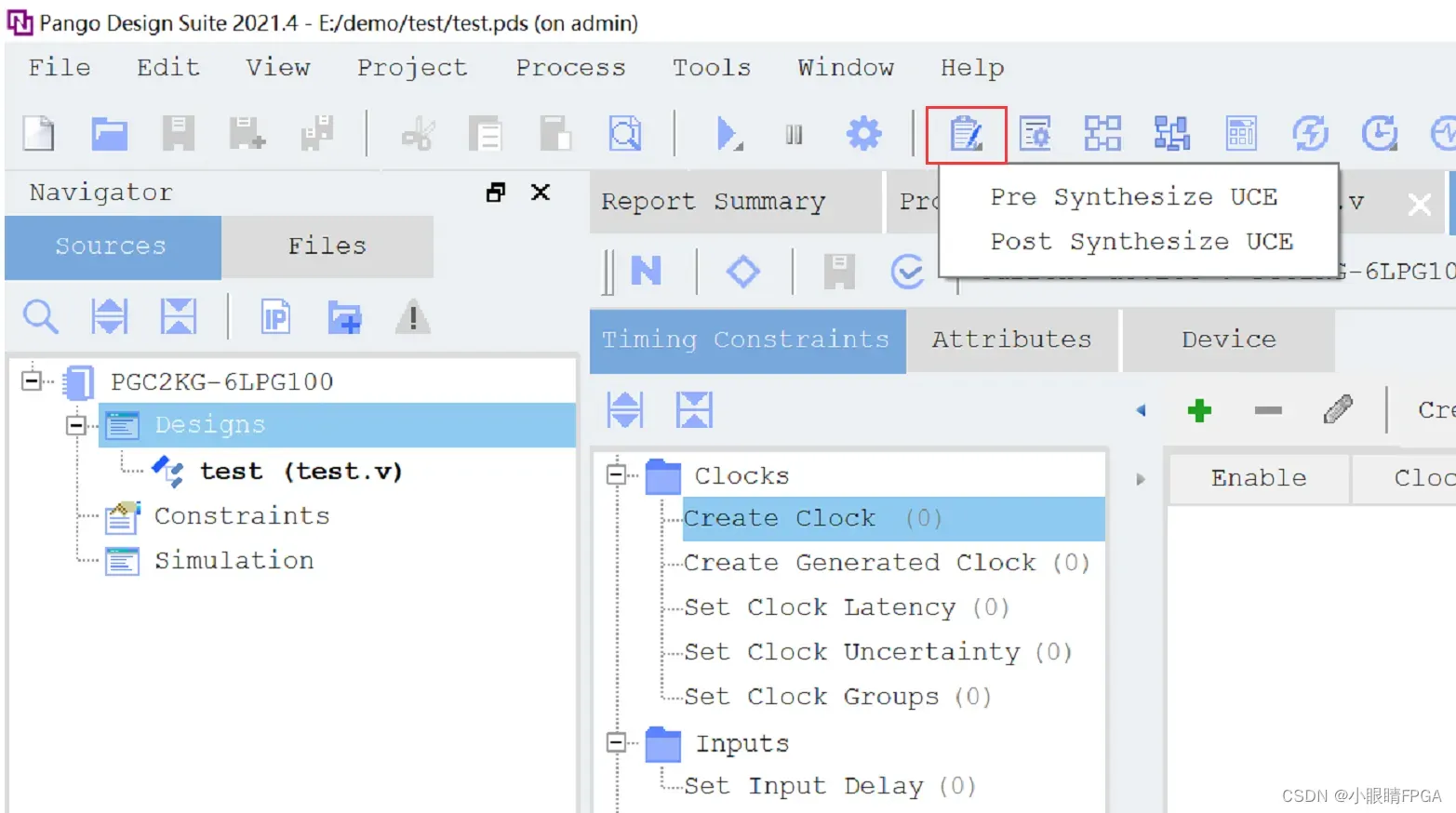

工具栏 User Constraint Editor(Timing and Logic)图标 点击按钮后二级菜单会有两个选项:Pre Synthesize UCE(综合之前打开约束编辑器)、 Post Synthesize UCE(综合之后打开约束编辑器)。根据选择进行打开。

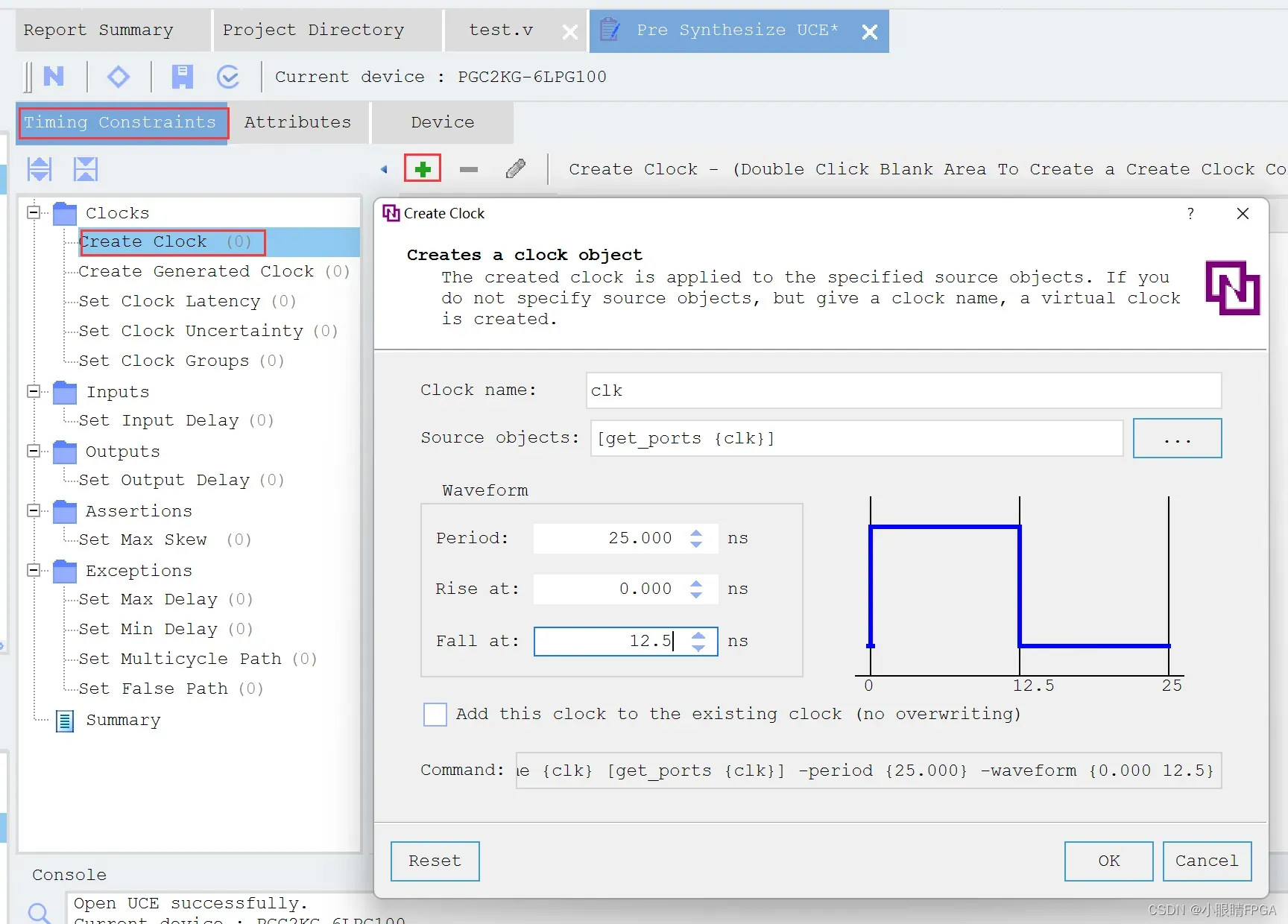

1.时钟约束

打开 UCE 后,选择 Timing Constraints 后选择 Create Clock 添加基准时钟,基准时钟 一般是通过输入 port 输入用户涉及的板上时钟。

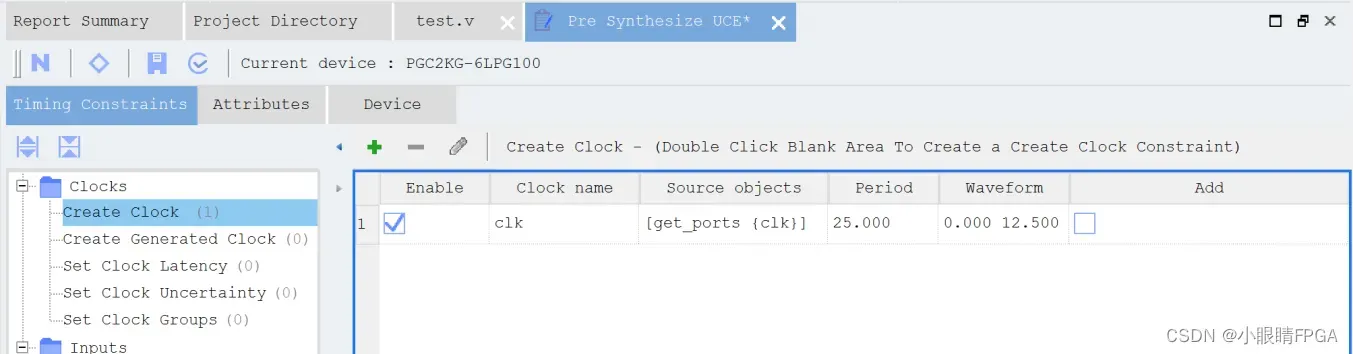

在弹窗中对时钟命名,关联时钟管脚,添加时钟参数,点击 OK 会创建一条时钟约束, Reset 重置该页面。创建完成如下图所示:

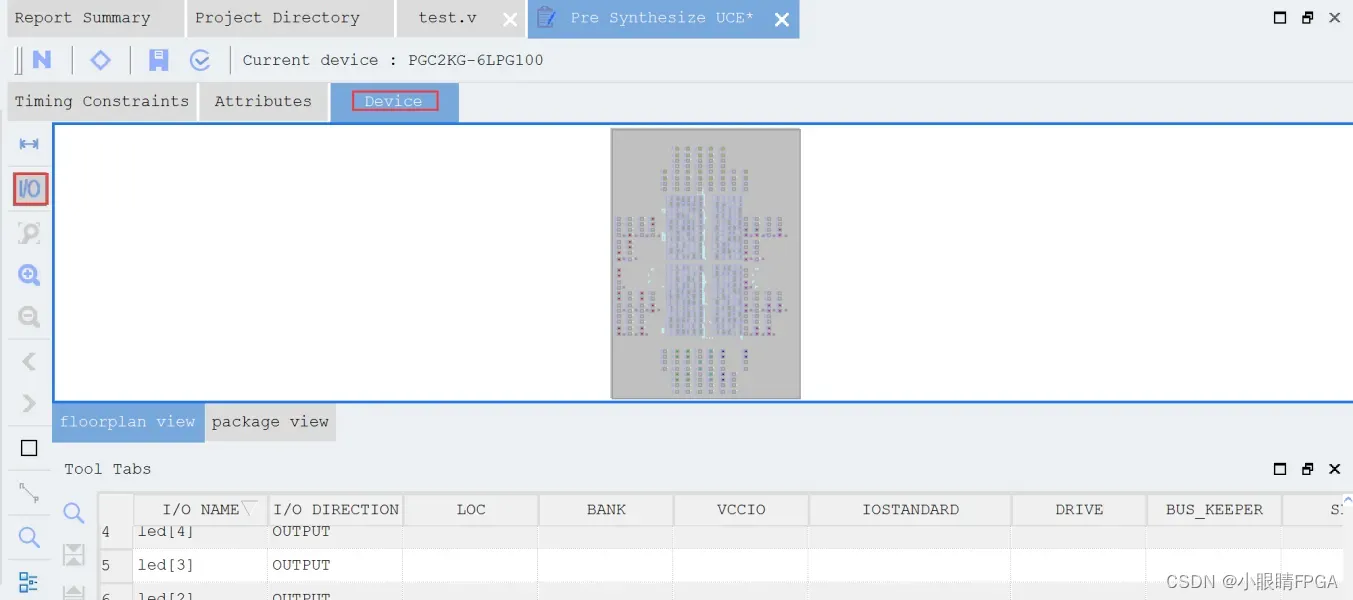

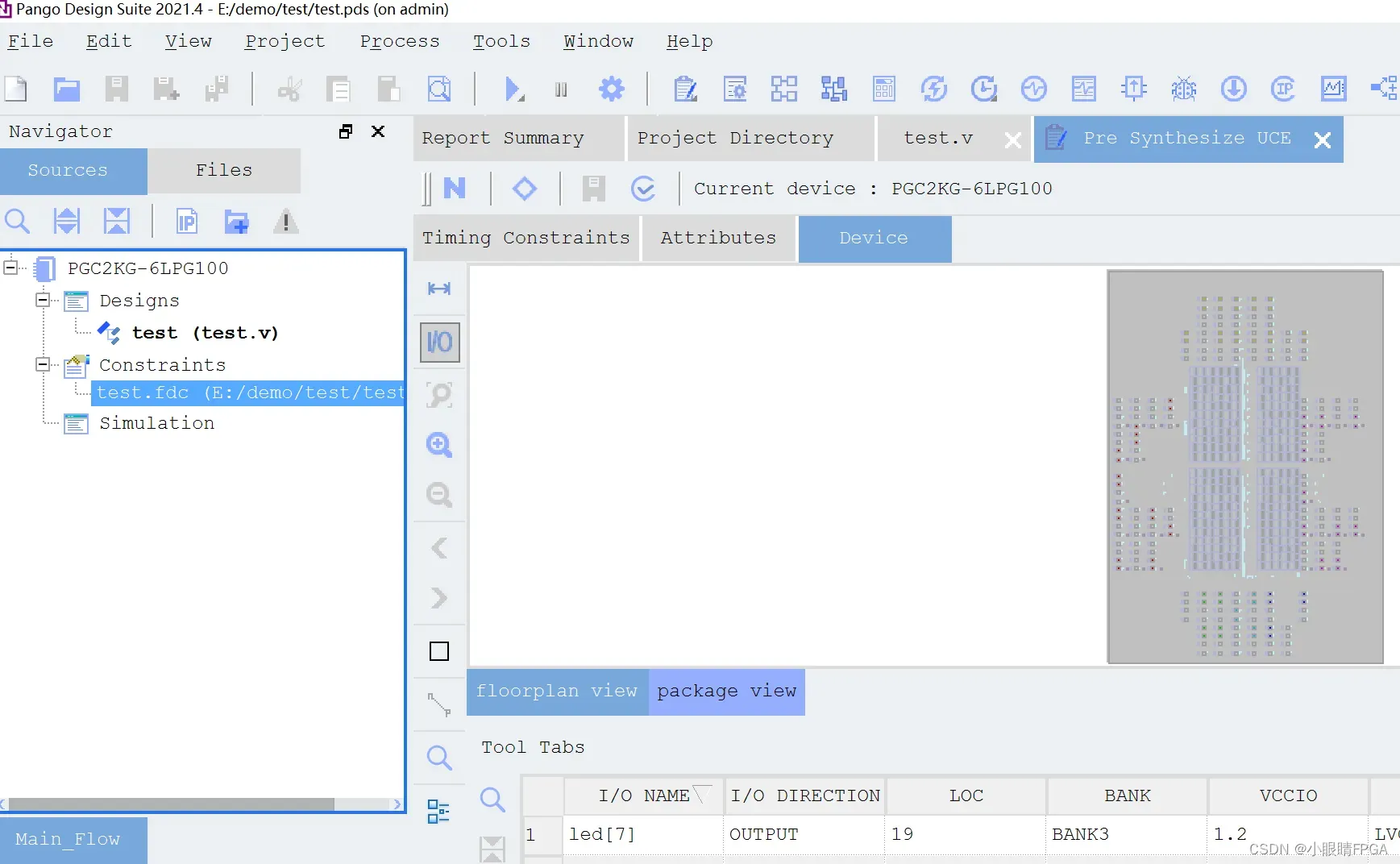

2.物理约束

打开 UCE 后,选择 Device 后选择 I/O,编辑 IO 的分配。

按照原理图编辑好 IO 分配后,点击保存,会生成.fdc 文件。

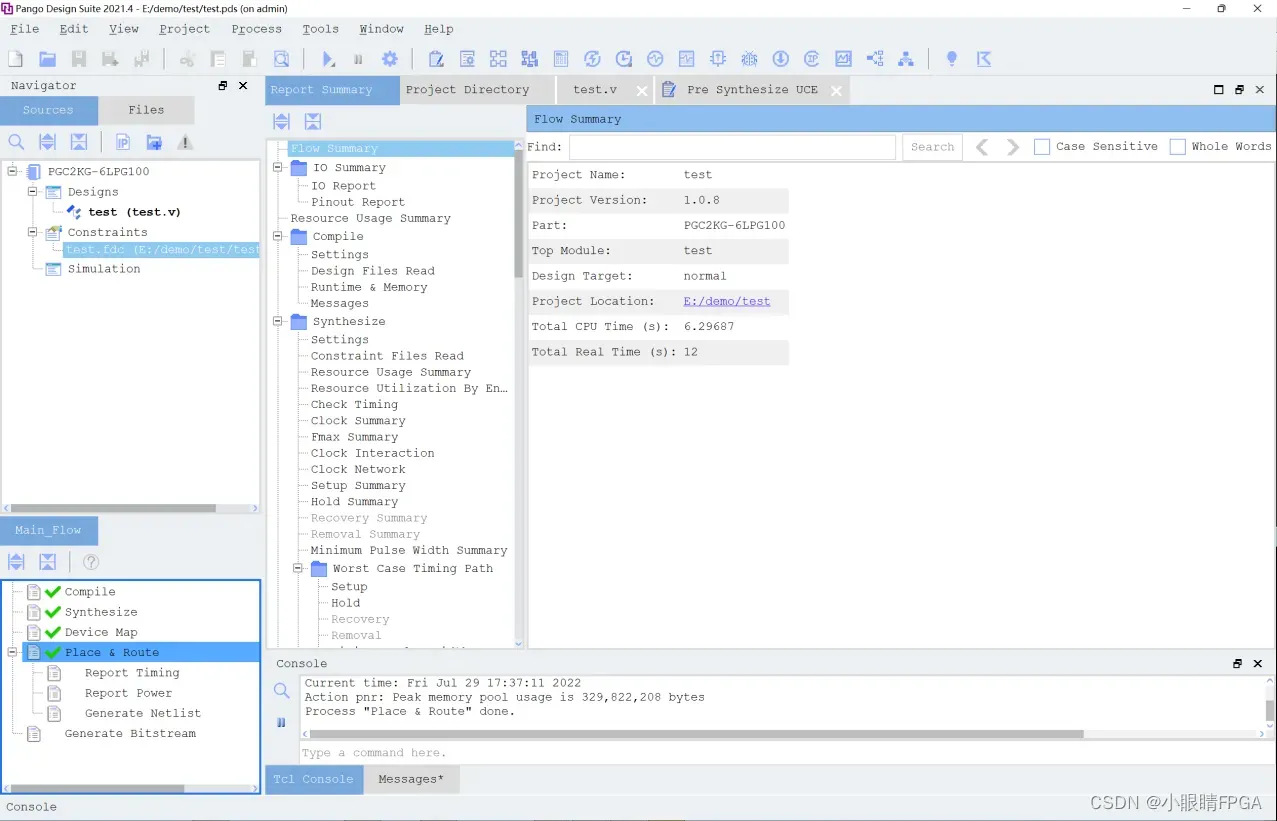

六、 Place&Route

布局布线(Place & Route)根据用户约束和物理约束,对设计模块进行实际的布局及布 线。 运行 Place & Route 流程有以下方式可以实现:

(1)直接双击 Place & Route;

(2)右击 Place & Route 点击 Run; 完成 Device Map 操作后,会看到下图所示:

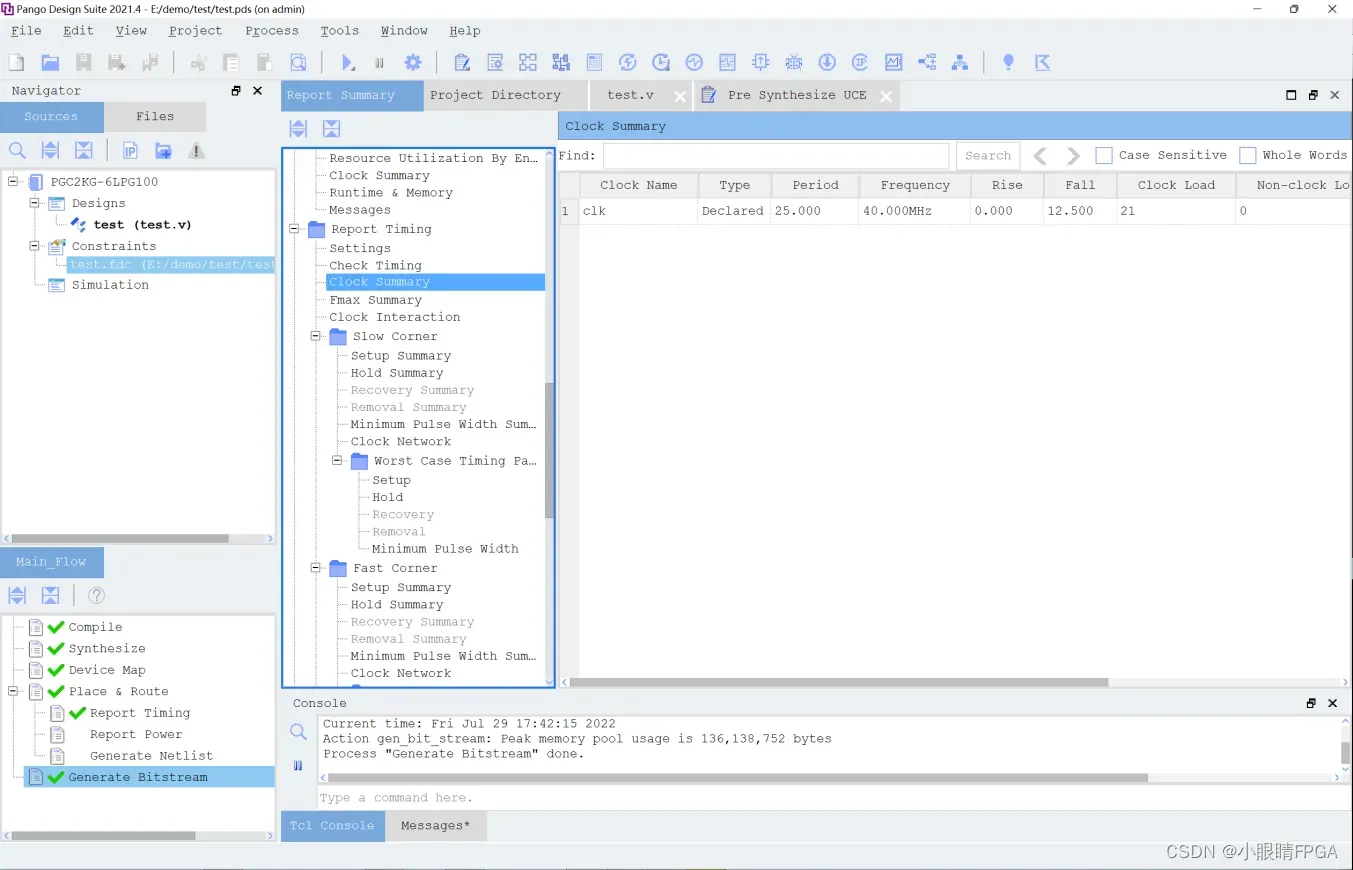

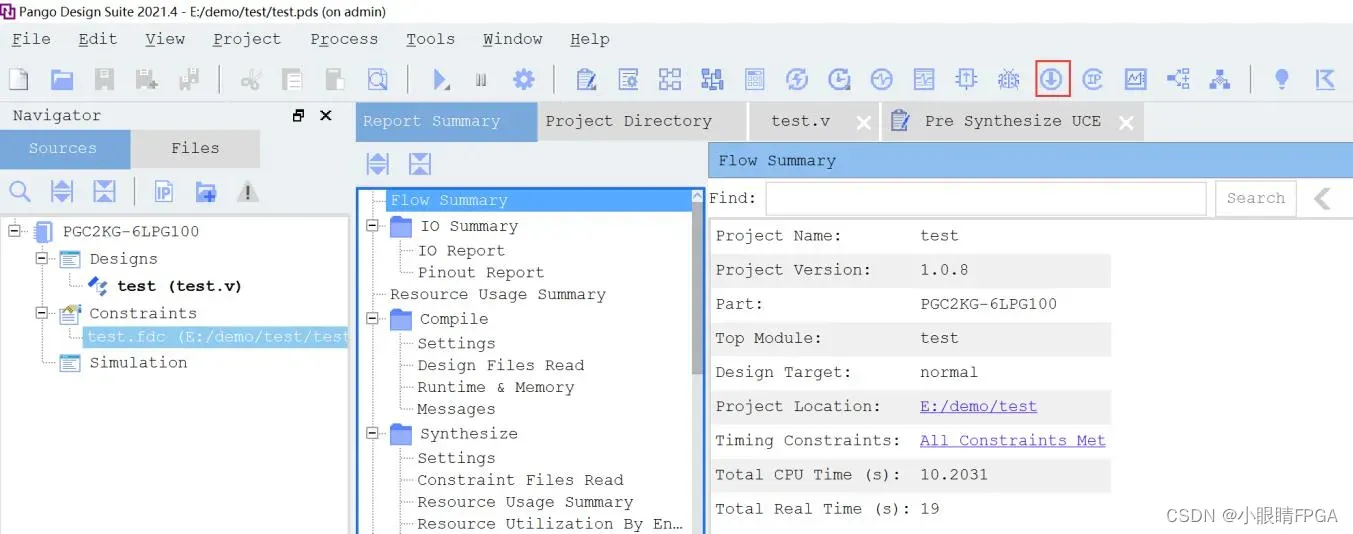

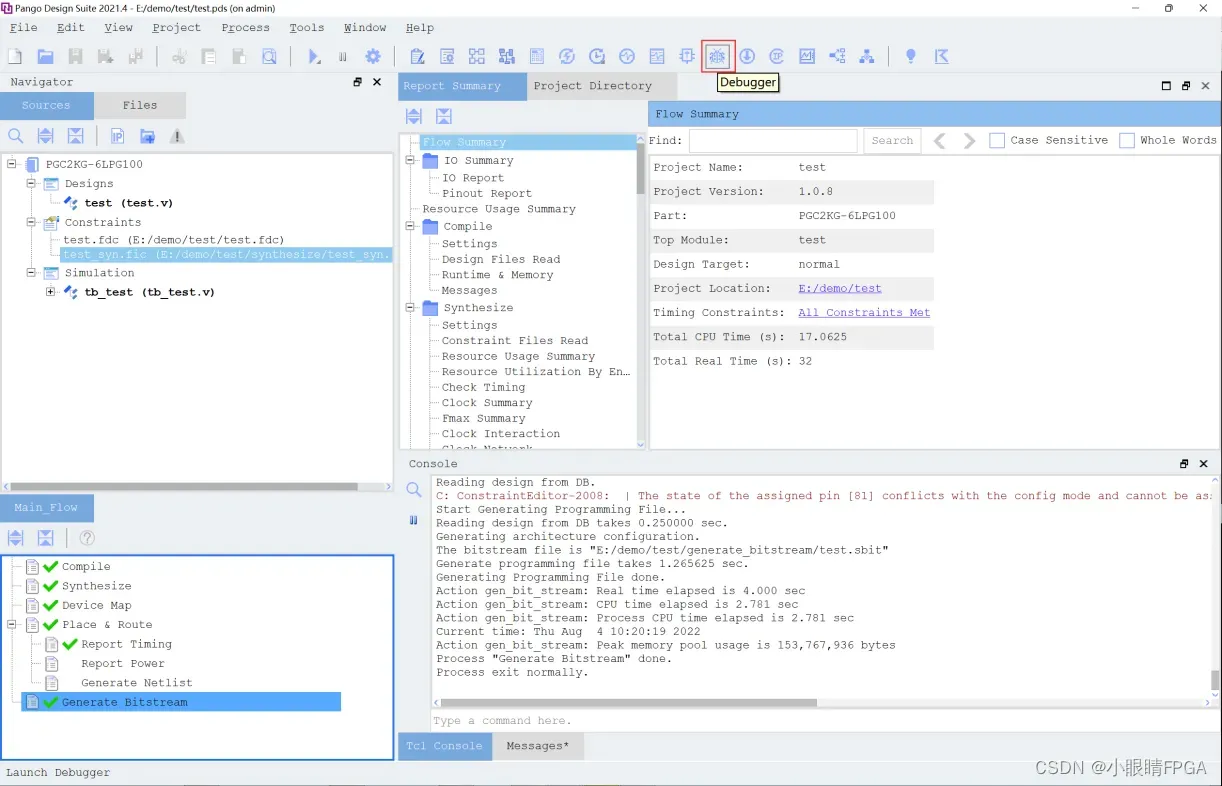

七、Generate Bitstream

Generate Bitstream 生成二进制位流文件。

运行 Generate Bitstream 流程有以下方式 可以实现:

(1)直接双击 Generate Bitstream;

(2)右击 Generate Bitstream 点击 Run;

完成以上操作,将会产生位流文件。运行 Generate Bitstream,可以看到界面如下图所 示:

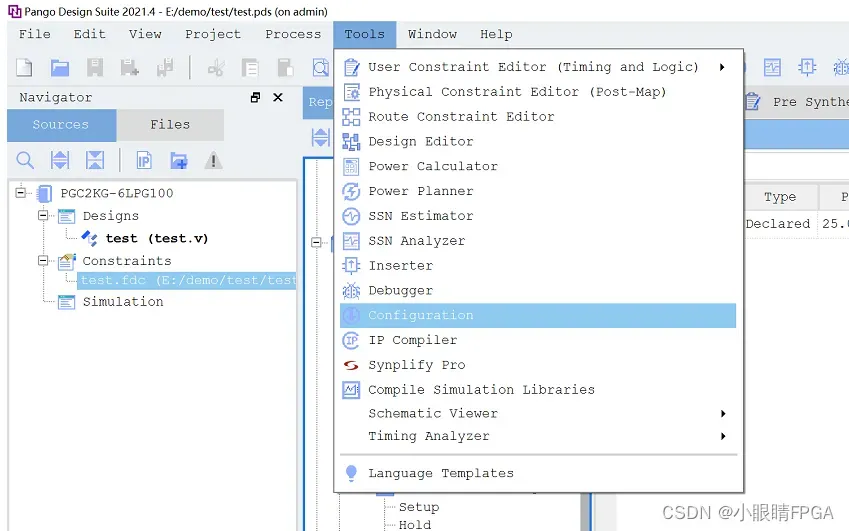

八、下载位流文件

点击 Tools 选择 Configuration 或者点击工具栏图标 Configuration,如下图所示。

Tools 下的 Configuration

工具栏 Configuration 图标

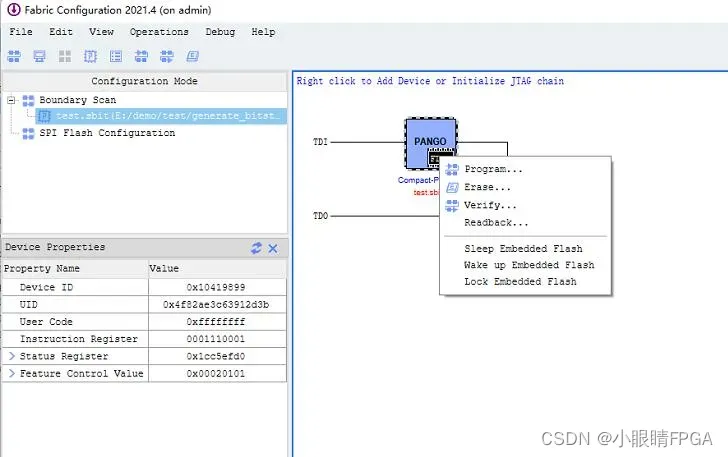

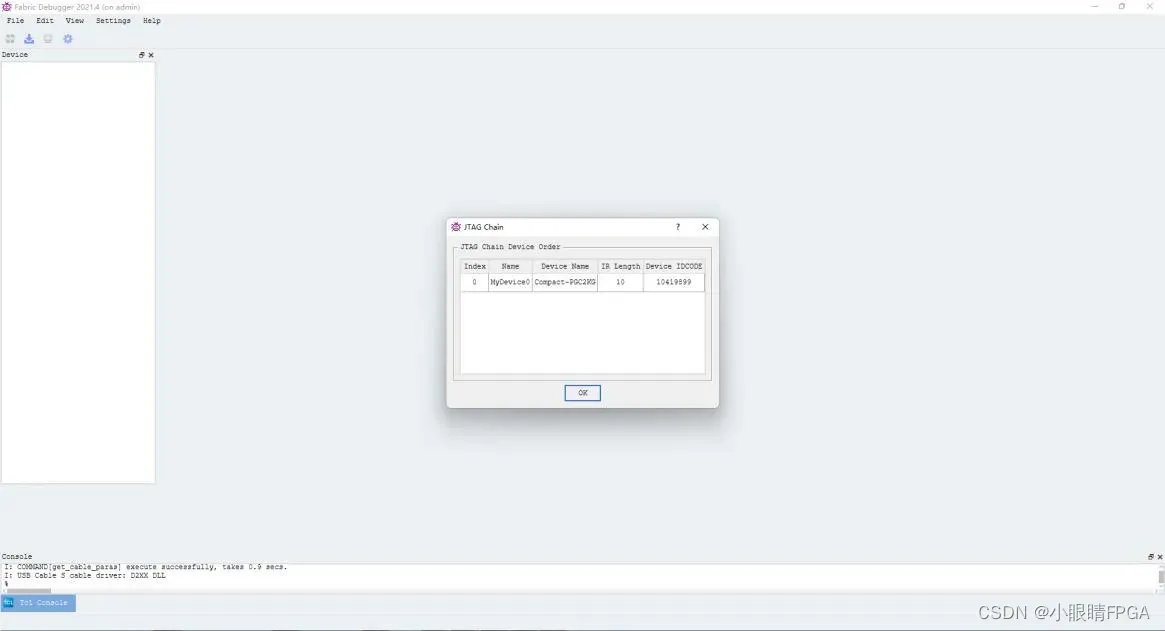

打开 Configuration 后直接选择 Scan Device 直接进行扫描 Jtag 链操作,初始化链成功, 会将链上扫描到的所有器件显示于工作区内,并在器件属性窗口显示当前器件的器件信息, 并弹出对话显示能够为器件添加的配置文件:

初始化链成功

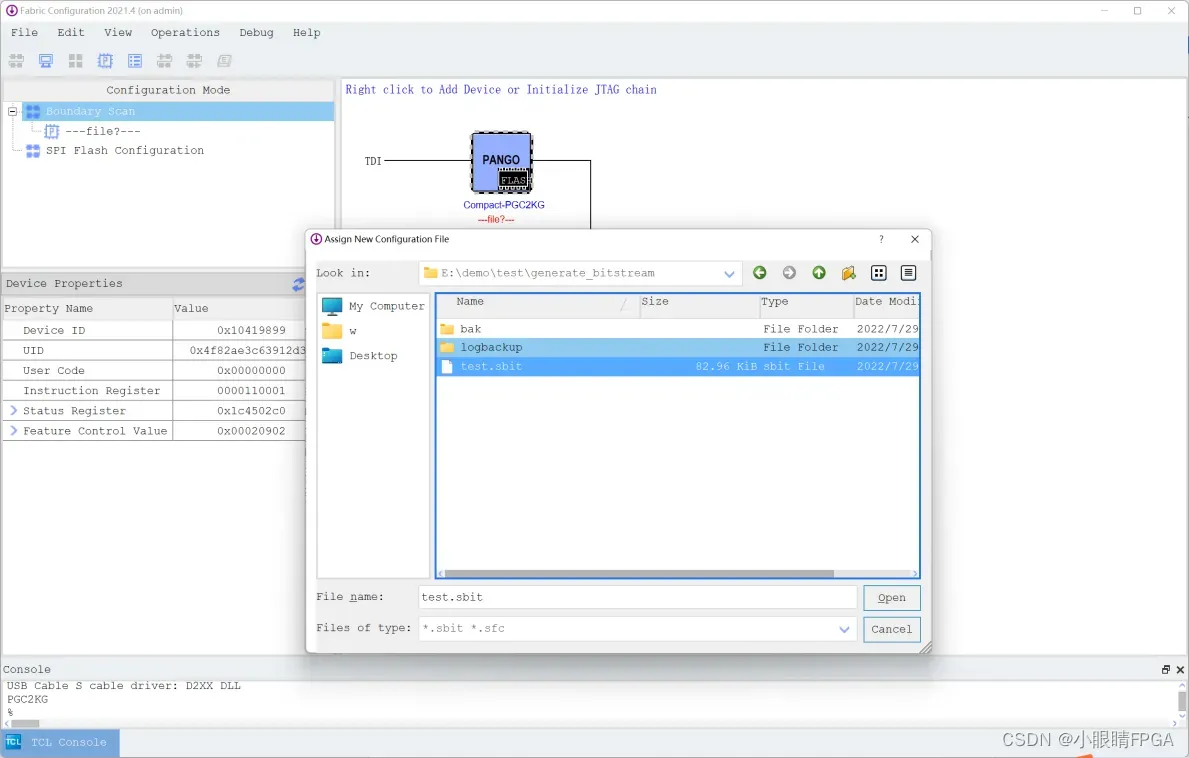

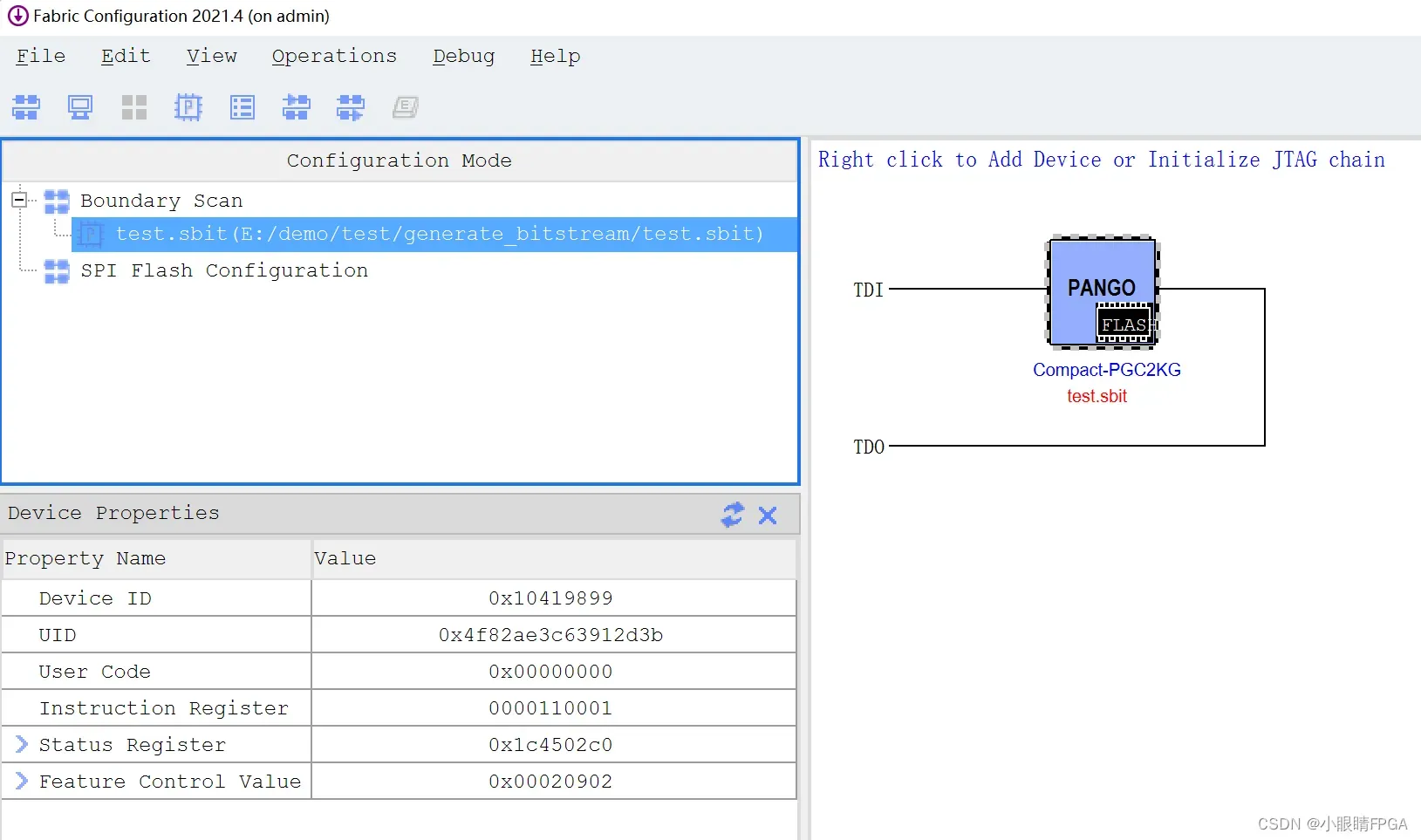

在对话框中选择位流文件,添加该配置文件,提示所载入文件的绝对路径并在信息栏中 显示,如下图所示:

为 Jtag 链上的器件添加配置文件

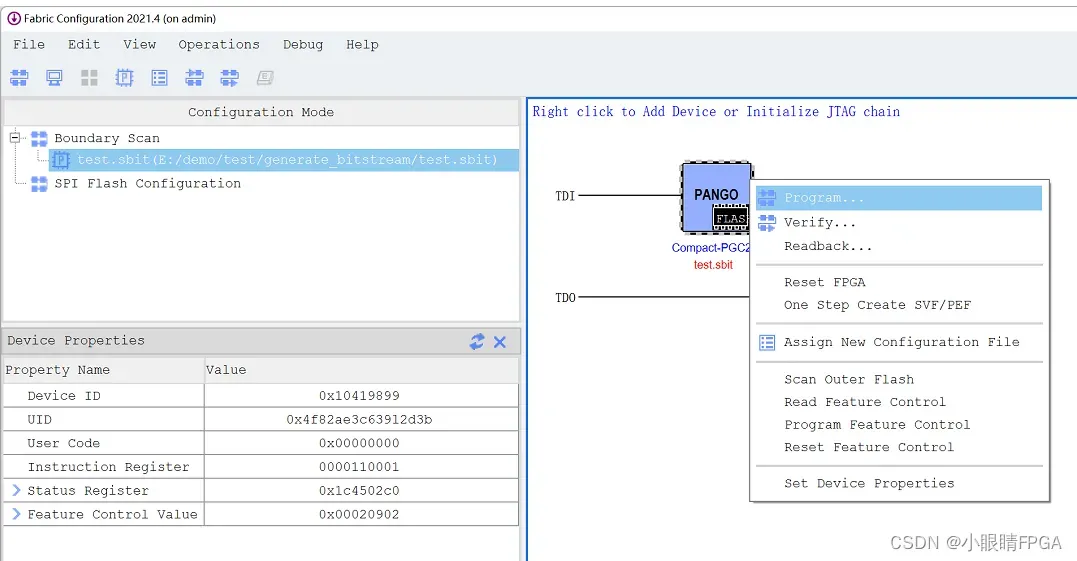

在配置位流文件后,便可将该文件下载到器件中。选中初始化链检测到的 FPGA 器件,然 后在该 FPGA 上单击鼠标右键,单击“Program”操作,软件开始将所配置的位流文件载入到 器件中。

下载位流文件

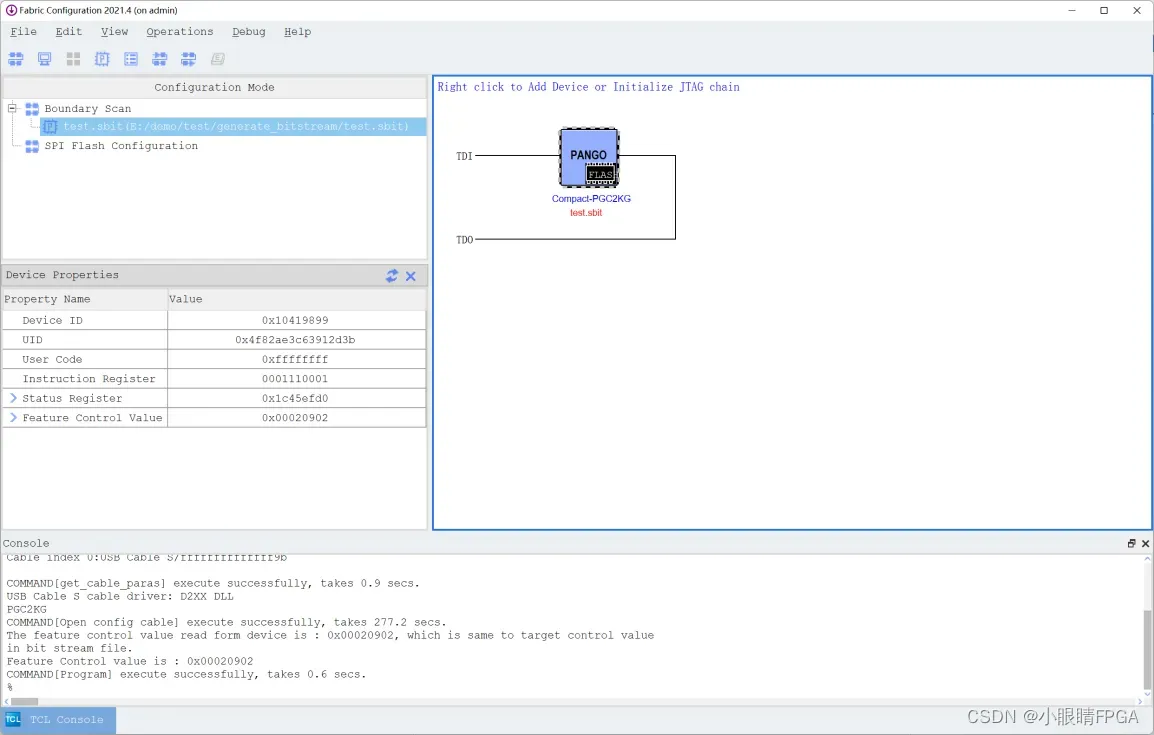

下载位流文件

下载位流文件成功

Compact 系列器件内部带有 Flash 模块。对 Embed Flash 进行操作时,用户可通过右键 菜单->Set Device Properties->编程选项中的 Embed FlashProperties 项进行嵌入式 Flash 的下载属性配置。(注意启动模式选择,详见 2.9(1))

对 Embed Flash 进行操作

九、复用管脚设置

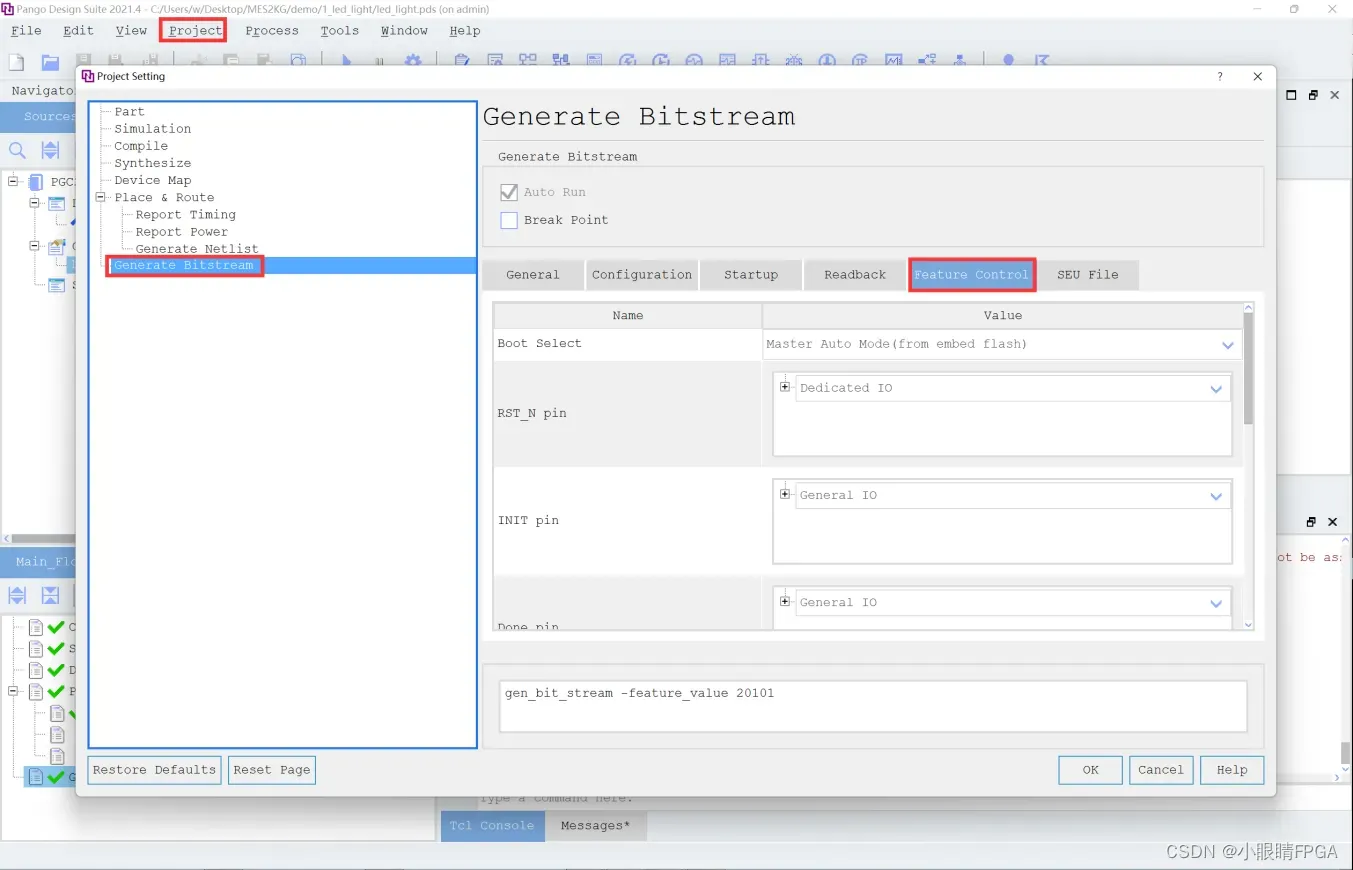

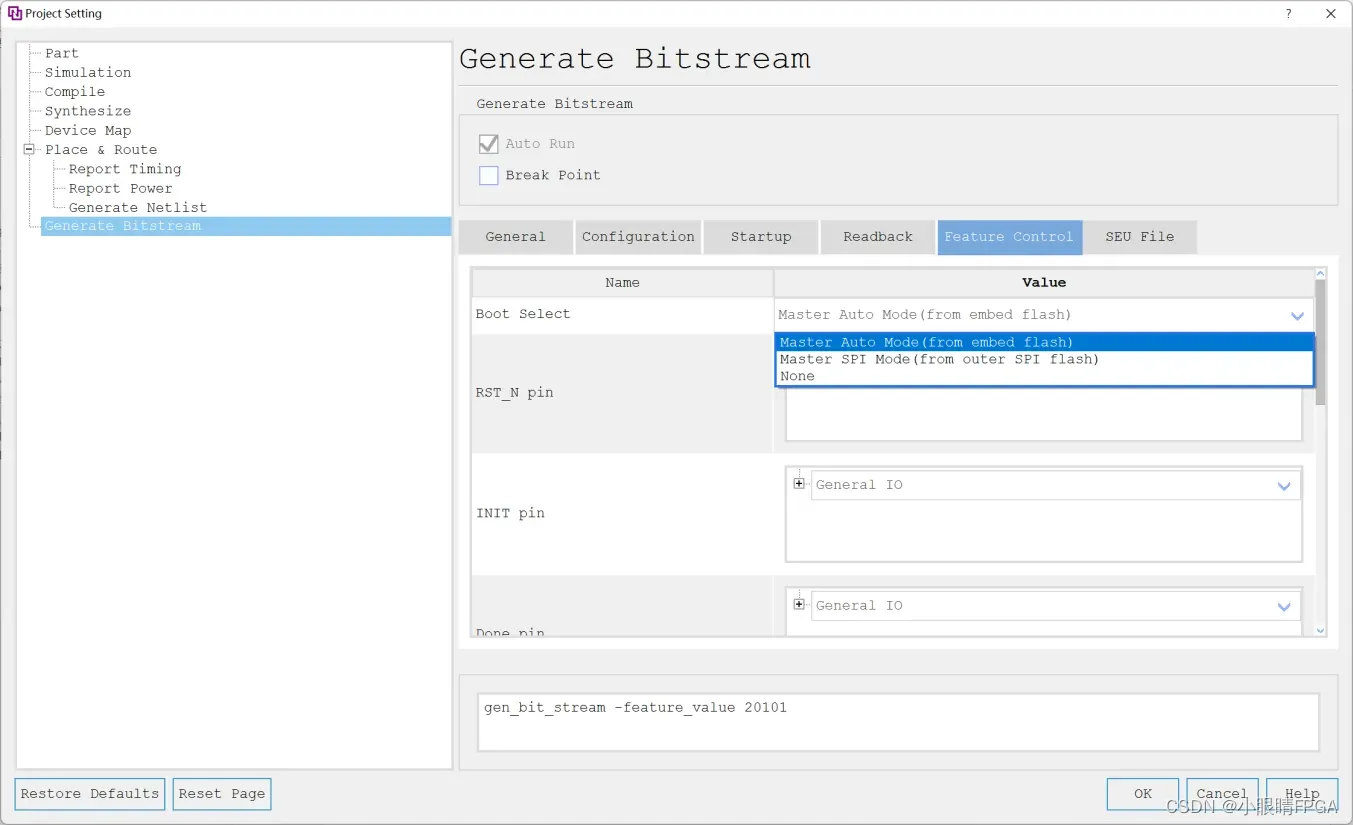

Compa 系列产品有很多复用管脚,用户通过设置特征控制位来控制这些复用管脚用作专 用 IO 还是普通 IO,并且可以在芯片配置过程中和进入用户模式后分别设置。 在菜单中选择 Project seting-Generate Bitstream-Feature Control

复用管脚配置界面

(1)PGC 器件启动方式的选择,默认是 NONE。

【Master Auto Mode】:主自加载,芯片上电完成初始化后,主动从嵌入式 Flash 获取位 流下载 CRAM;

【Master SPIMode】:主 SPI 配置,芯片上电完成初始化后,主动从外部 SPI Flash 获取 位流下载 CRAM;

【None】:芯片上电完成初始化后,没有任何操作。

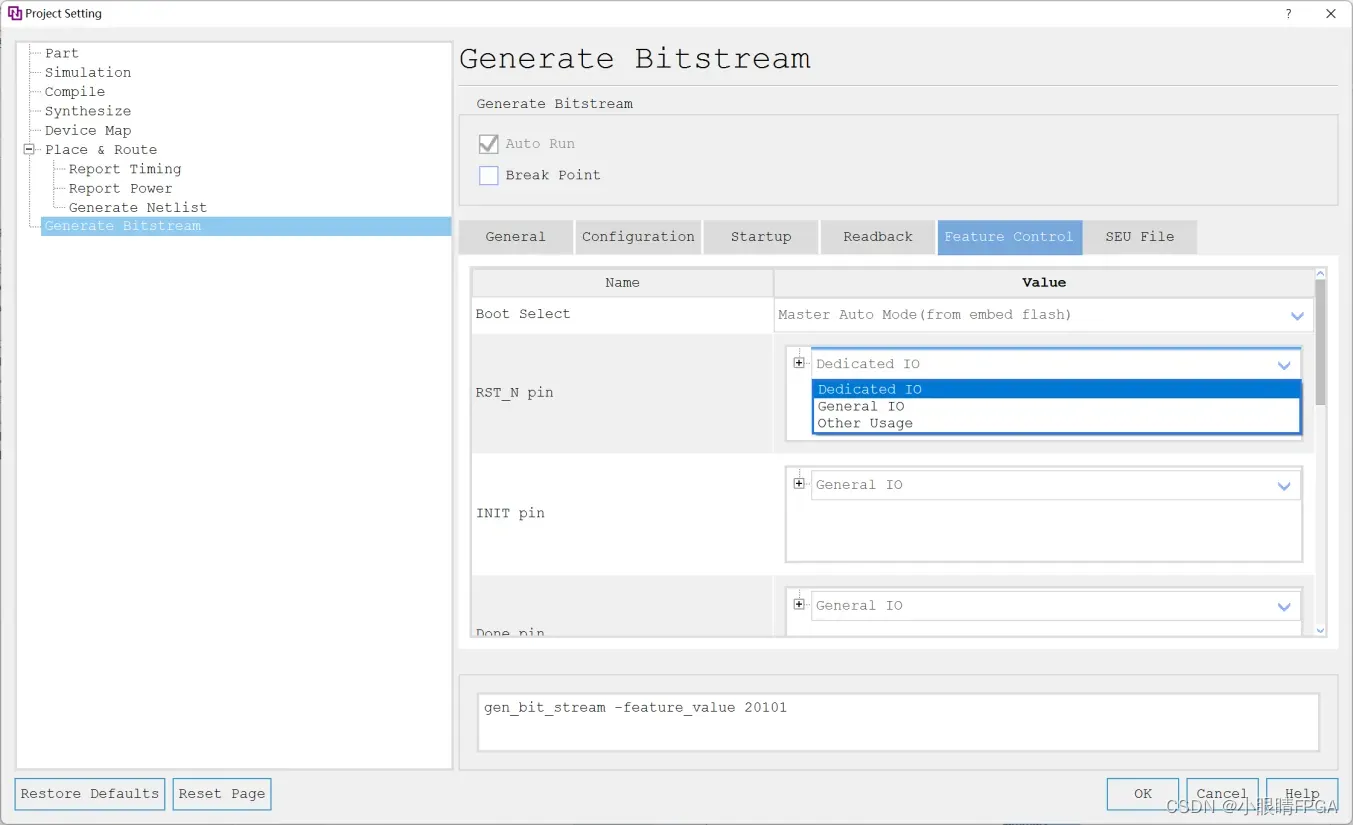

(2)RST_N(RSTN)用作专用 IO 时是复位管脚,默认是普通 IO。

【Dedicated IO】:在配置过程中和用户模式下都作为专用 IO,用来复位芯片;

【General IO】:在配置过程中和用户模式下都作为普通 IO;

【Other Usage】:点击“+”,在配置过程中和用户模式下混合设置,勾选表示作为普通 IO。

十、 Modelsim与PDS联合仿真

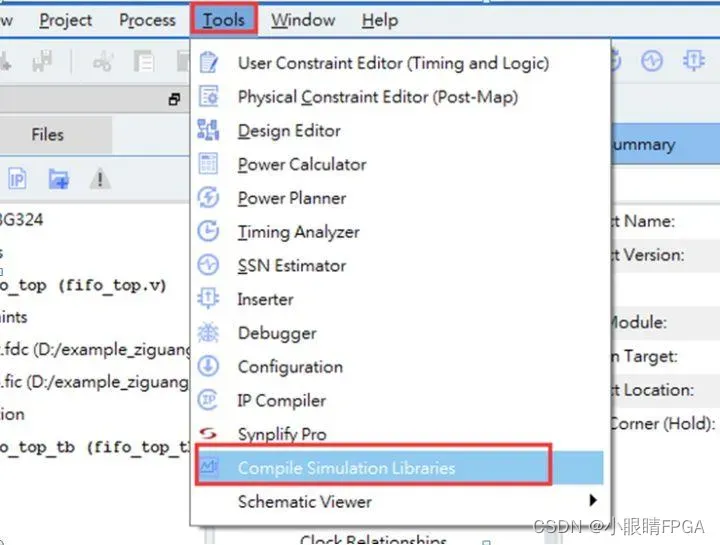

仿真库编译: 用户点击 PDS 的【tools】 菜单下的【Compile Simulation Libraries】。

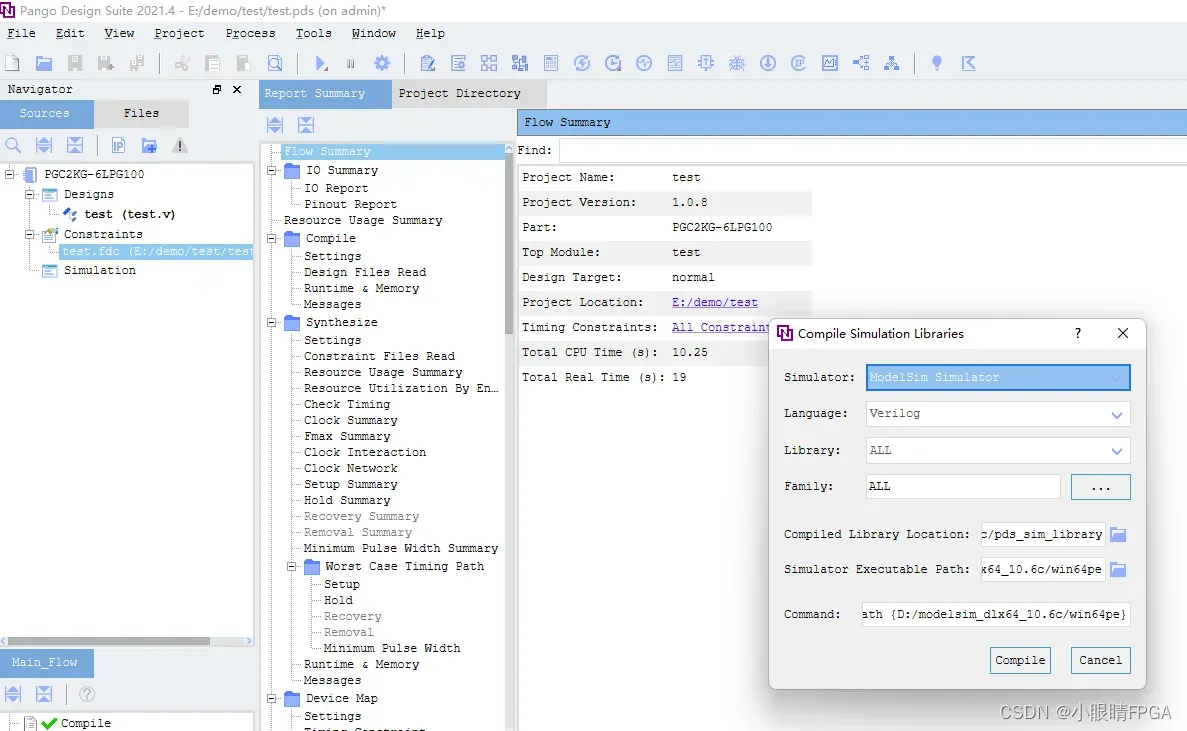

在弹出的界面中,按红色框中路径设置,把编译库 pango_sim_libraries 放在 C:\modeltech64_10.1c 仿真软件文件夹下,点击【compile】 即开始编译。

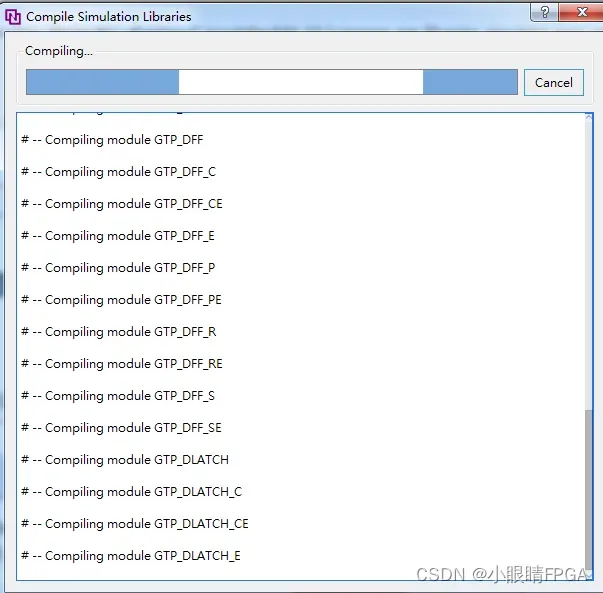

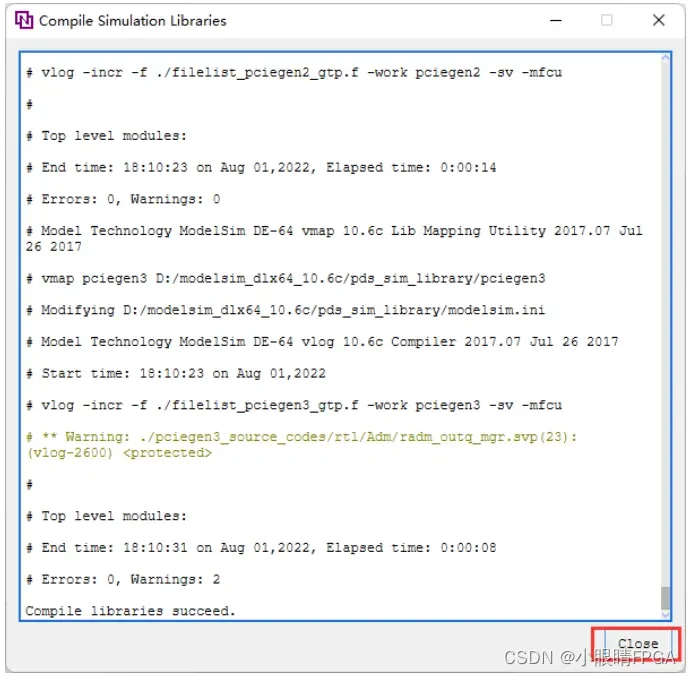

下面界面是开始进行编译,编译成功后点击 Close 完成编译;

开始进行编译

编译完成

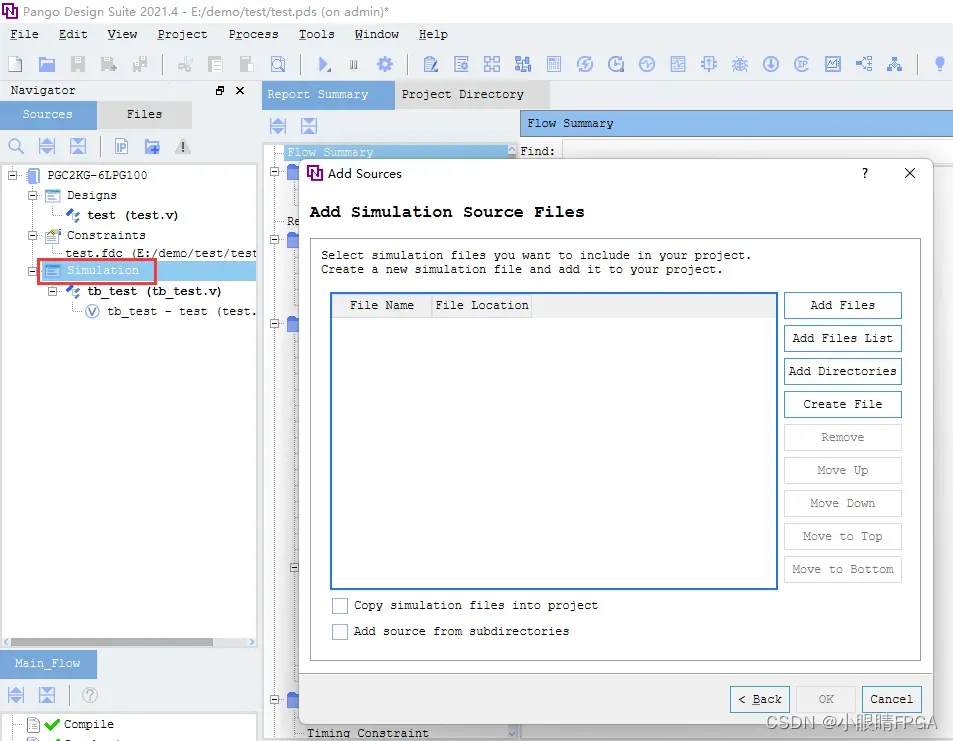

双击 Simulation,添加或新建激励文件。

添加或新建激励文件

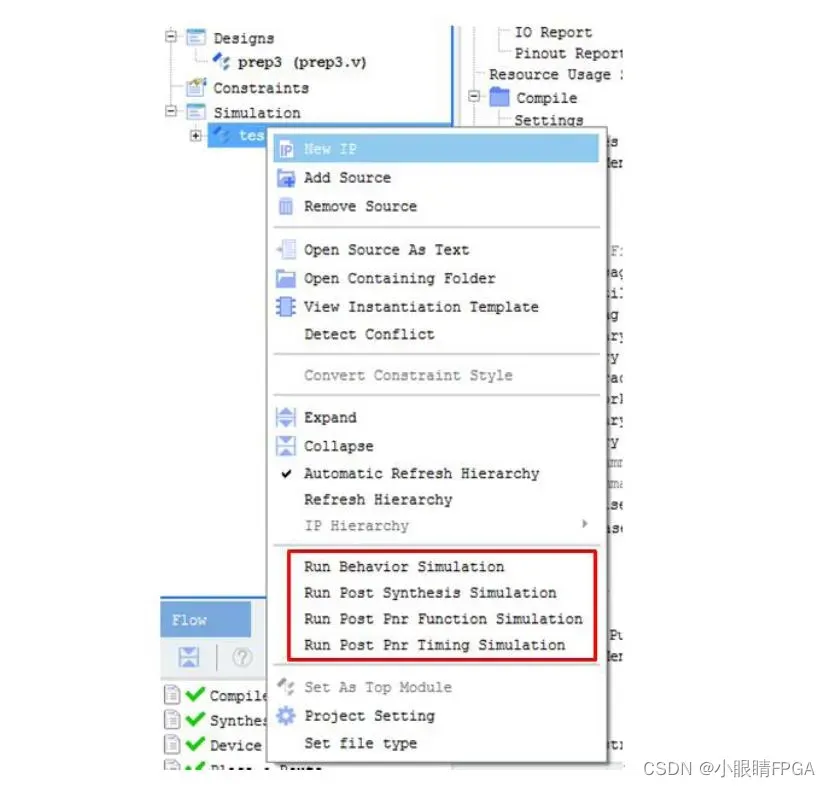

在完成上述所有步骤后,右击激励文件,就可以进行联合仿真了。

右击激励文件进行联合仿真

十一、ebugger

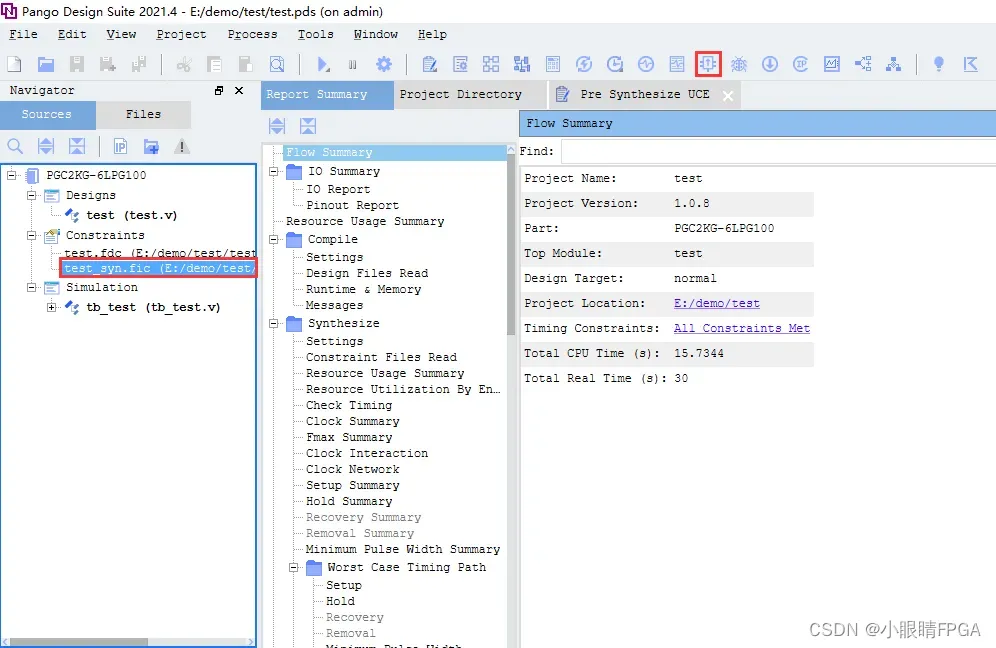

Fabric Inserter 软件主要功能是把 DebugCore 自动插入用户的设计网表中生成新的设 计网表,可以通过单击菜单栏或工具栏中的 Inserter 图标启动 Inserter 软件,或通过双击 Constraints 列表中的.fic 文件启动 Inserter,需要注意的是只有在 PDS 中添加了资源文 件(.v 或.vm)后才能启动 Inserter。

启动 Inserter

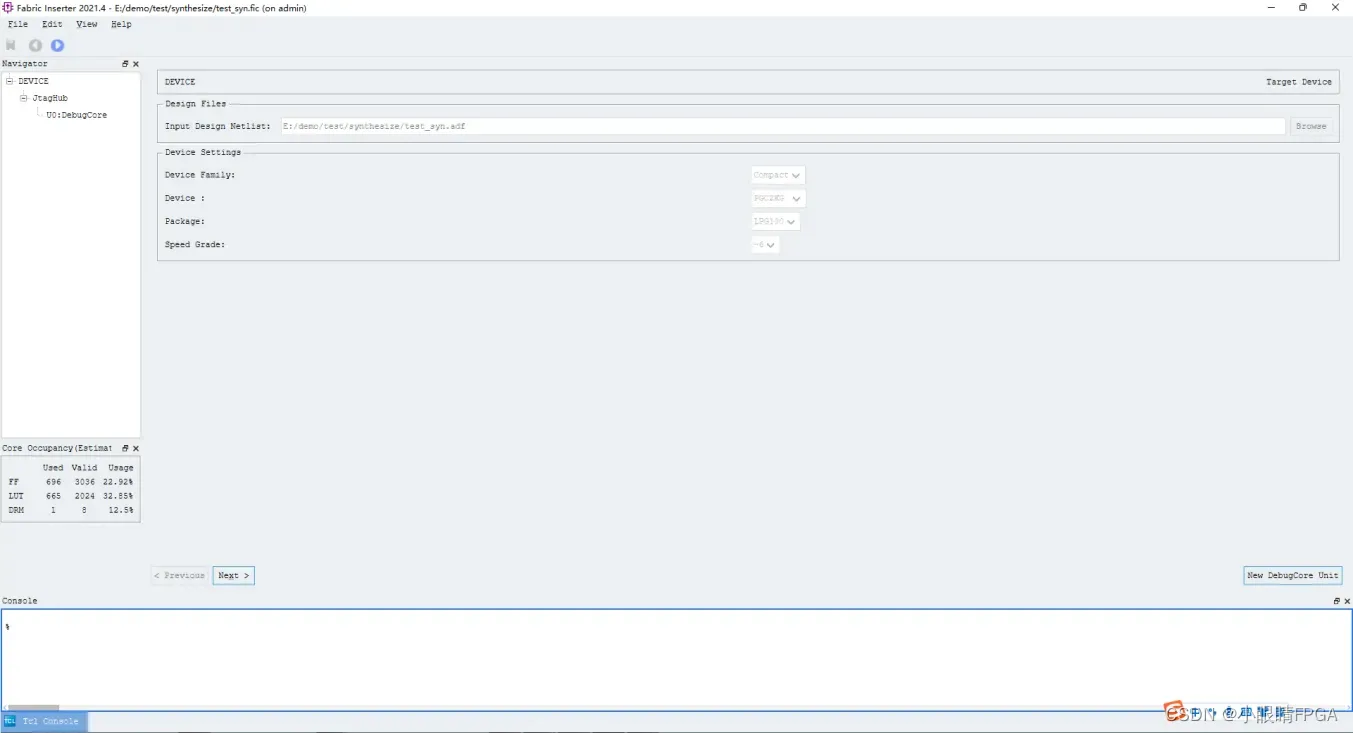

打开 Inserter 主界面后,Inserter 会自动加载并解析用户添加至 PDS 中的设计文件, 并自动生成输出文件路径。

Inserter 软件主界面

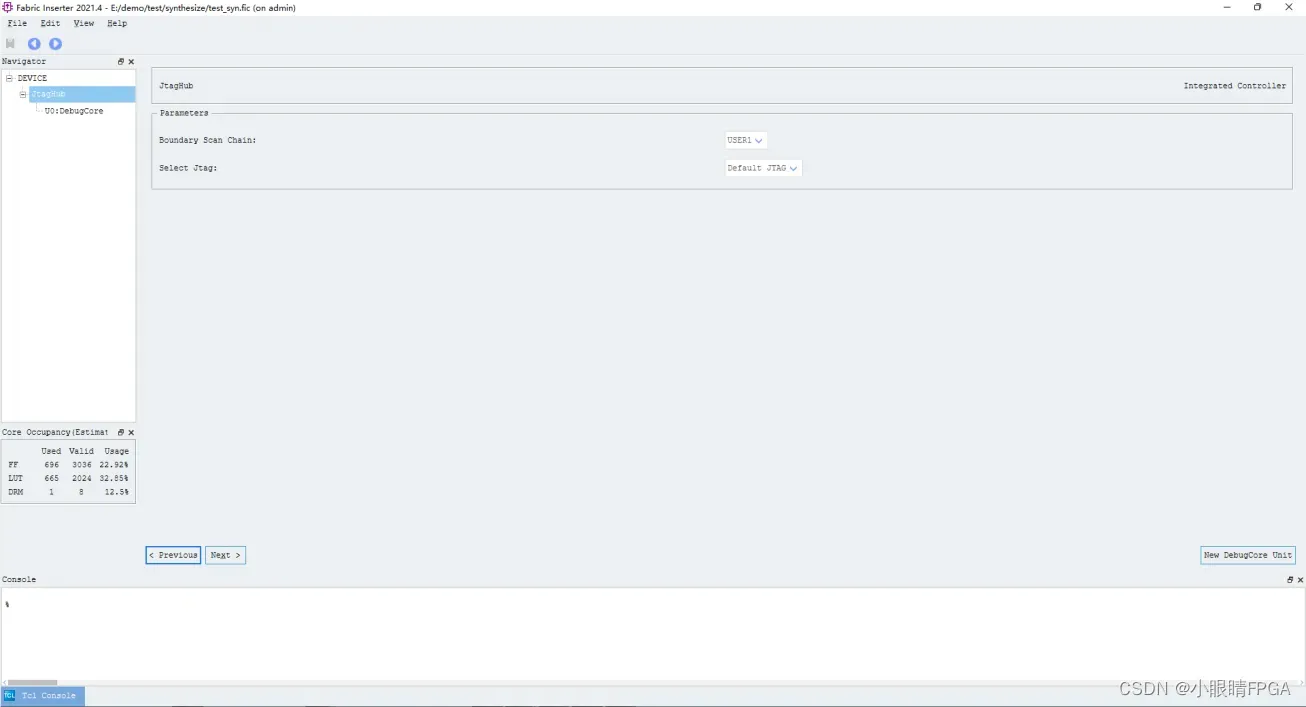

点击 Next 进入 JtagHub 配置界面,在这个界面中用户可做的选择为点击右下角 New DebugCore Unit 按钮添加 DebugCore,最多可添加 15 个。如不添加 DebugCore,再点击 Next 软件会默认添加一个 DebugCore。同时,用户可在该界面中指定要使用的边界扫描链,也可 以指定要使用的 JTAG。

JtagHub 配置界面

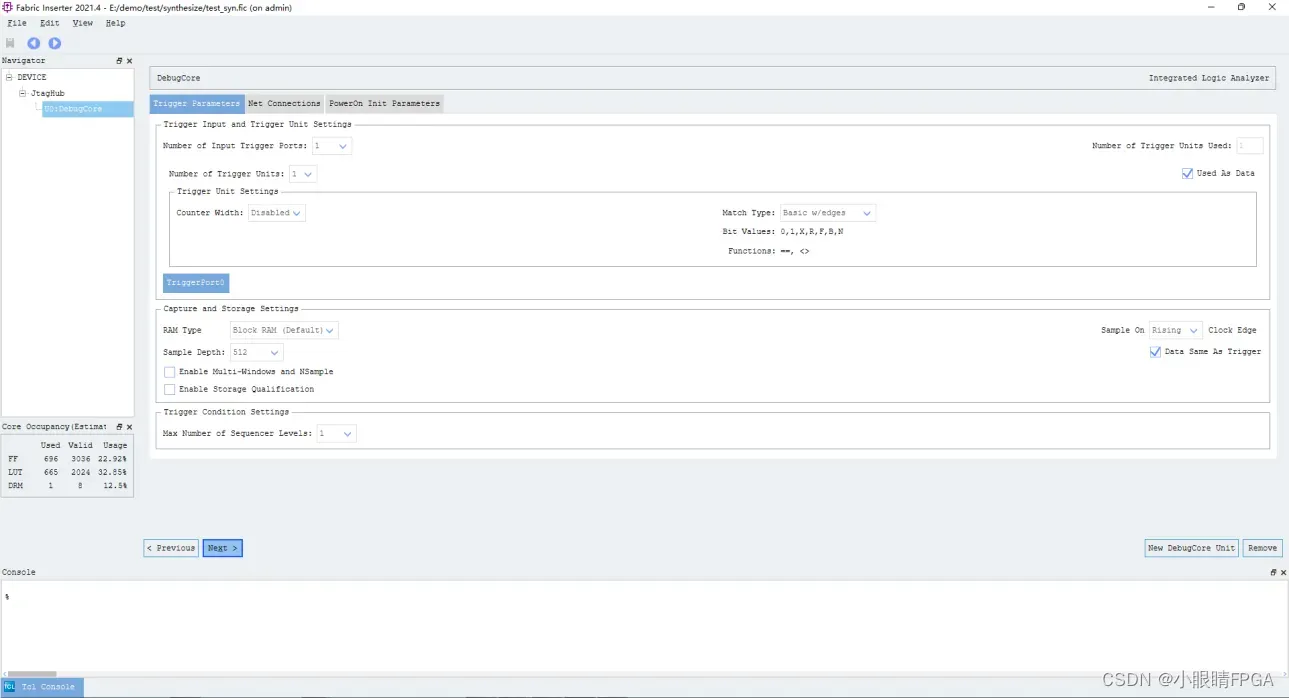

配置完 JtagHub 后点击 Next 按钮进入 DebugCore 配置界面:一个 DebugCore 对应界面 中包含以 Trigger Parameters、Net Connections 和 PowerOn Init Parameters 为标题的标 签页面,分别对应 DebugCore 不同参数的配置。可以点击 Next 和 Previous 或者直接点击标 签页标题进行标签页的切换。

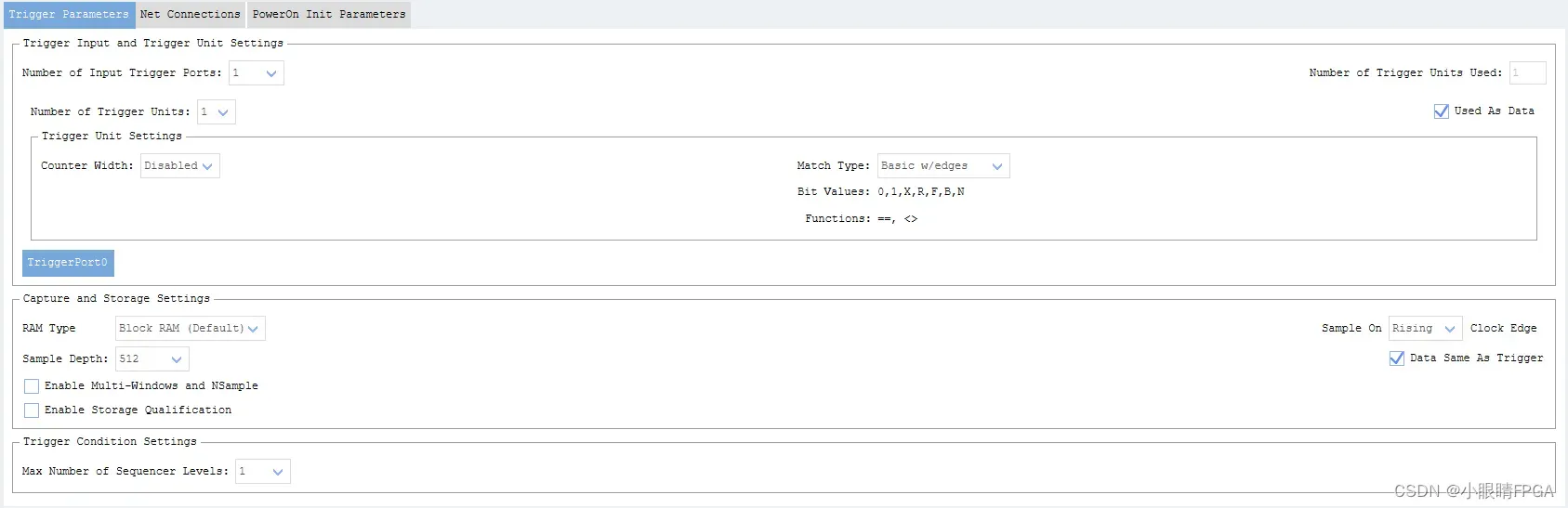

Trigger Parameters 选项卡中的配置选项分为三组,分别用于对触发端口(Trigger Port),捕获存储(Capture & Storage)和触发条件(Trigger Condition)进行相关参数配置。

触发端口相关设置:包括触发端口的数量,每个触发端口下挂接的匹配单元的数量及其 类型等。

捕获存储相关配置:包括数据的采样深度,采样时钟沿等。

触发条件相关配置:主要是对顺序触发的最大等级进行配置。

Trigger Parameters 界面

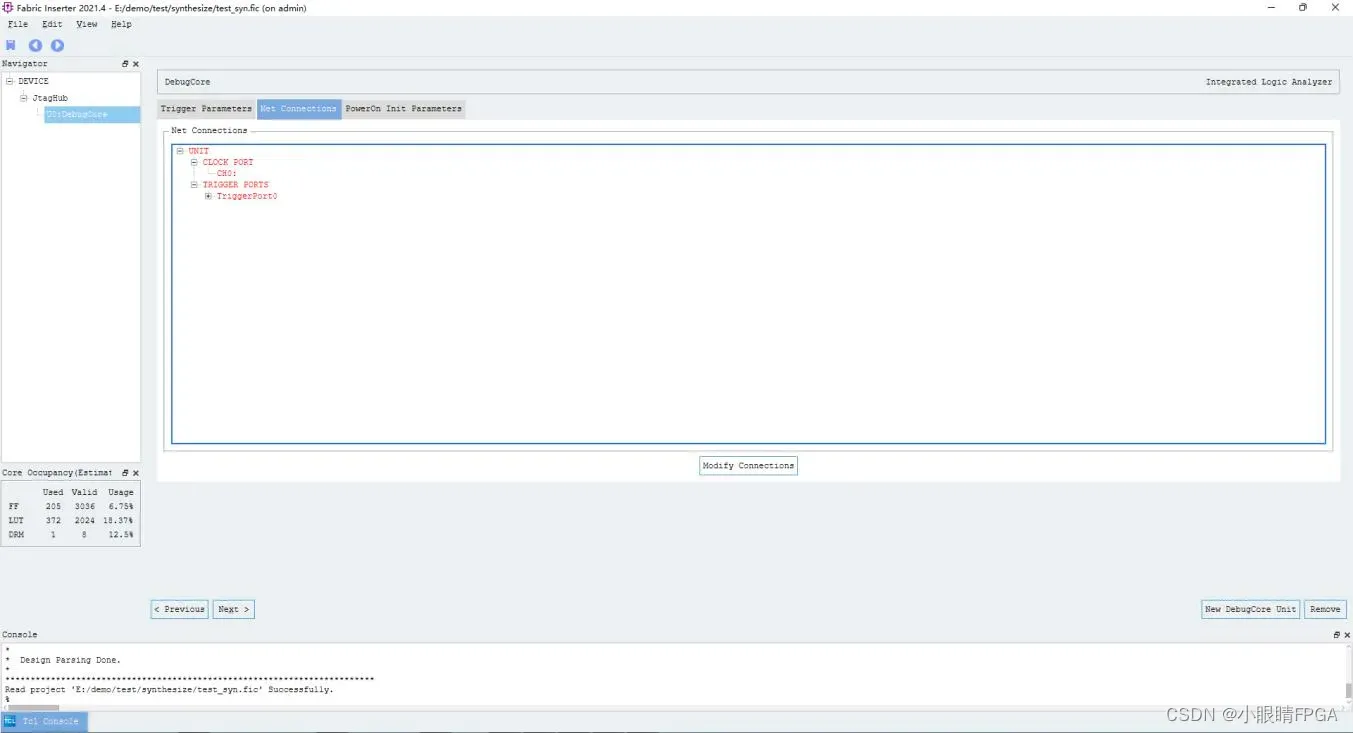

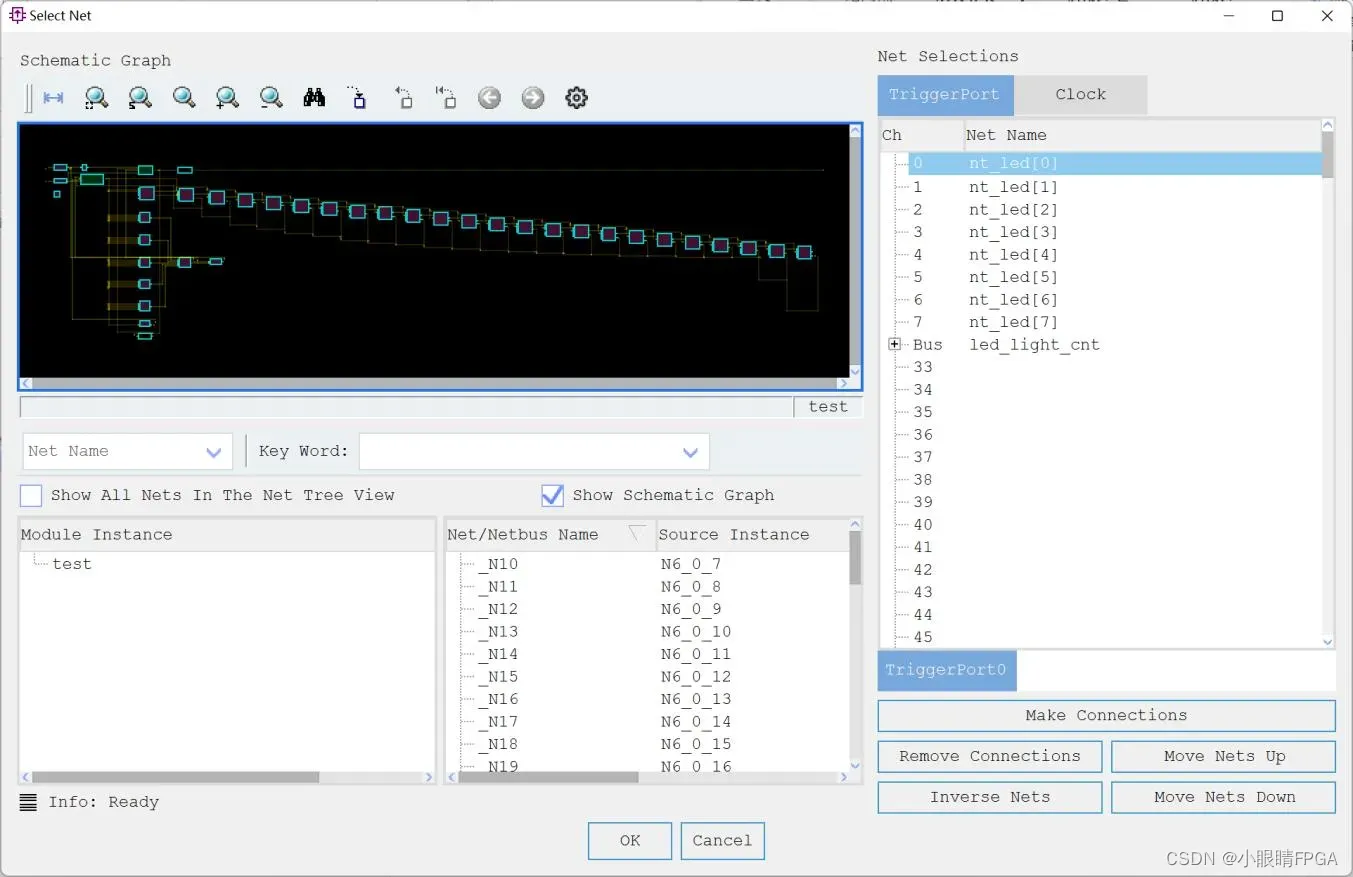

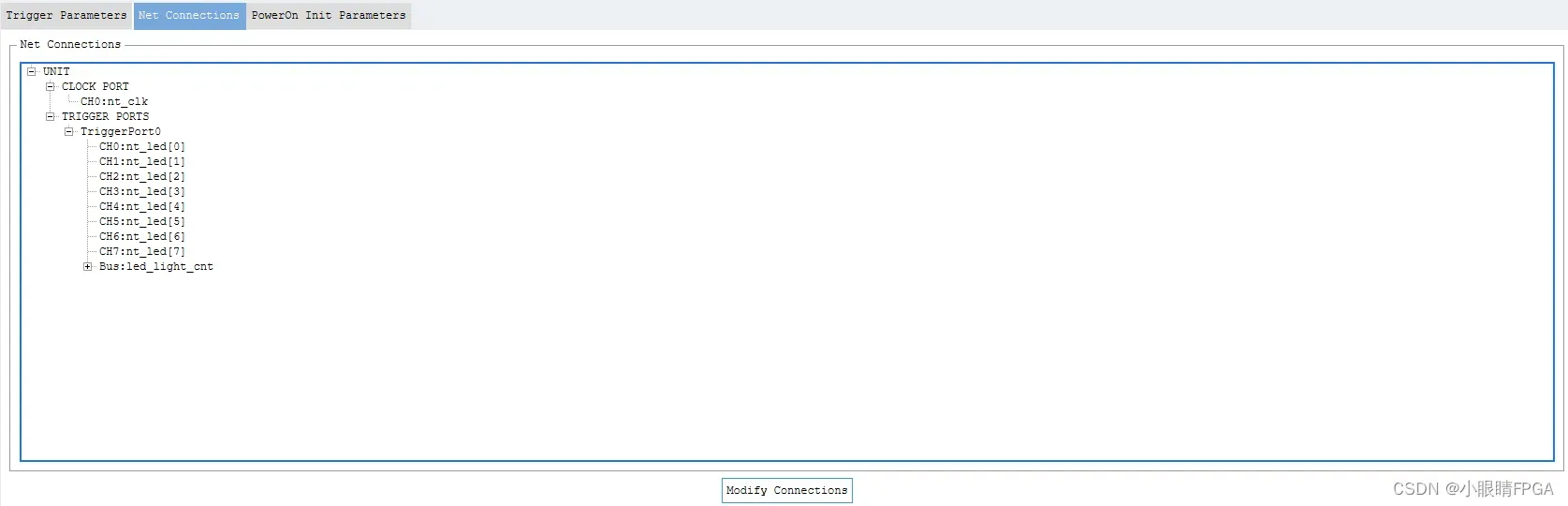

Net Connections 选项卡用于将 DebugCore 的输入信号和用户 design 中的网线连接起 来,尚未连接时,Net Connections 中的所有信号都为红色显示。点击 Modify Connection, 会弹出 Select Net 配置界面。利用 Select Net 对话框,可以把 Debug Core 的工作时钟、 触发信号、数据信号与设计中的网线连接起来,方法是右侧选中 Debug Core 的信号,在左侧下方选中需要连接的网线,单击 Make Connections 按钮,即可以完成一条或者多条信号的连 接,所有信号都连接好之后,单击 OK 按钮。

Net Connections 配置界面

Select Net 配置界面

Net Connections 配置完成界面

Debugger Core 各项参数配置完成并完成 Net 连接工作后,点击保存后退出 Inserter。 返回 PDS 软件中运行 Flow 中的 Map,PDS 将自动调用插核流程。

点击 Debugger 图标,启动 Fabric Debugger。

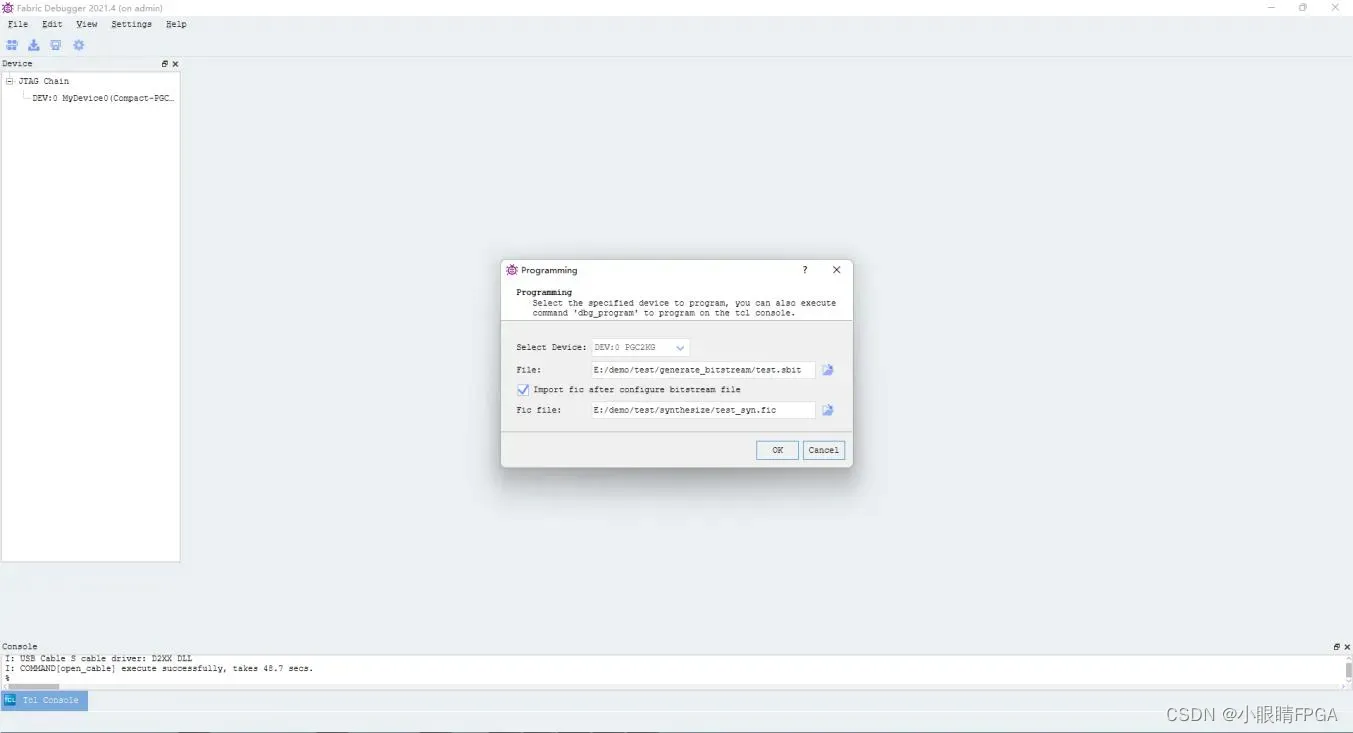

自动扫描 JTAG 链,查询链上的器件,如查询成功后点击 Configure BitStreamFile 按钮 或器件右键菜单打开位流配置界面,选择指定文件,同时可以通过手动或是自动的方式加载 fic 文件,自动加载 fic 方式会搜索位流文件所在目录以及上层目录,当存在与位流文件同 名的 fic 文件或是_trs.fic 文件时,会在下载位流后,自动导入 fic 文件,位流加载操作 界面如下图所示:

查询 JTAG 链上器件

查询 JTAG 链上器件

Debugger 加载文件图

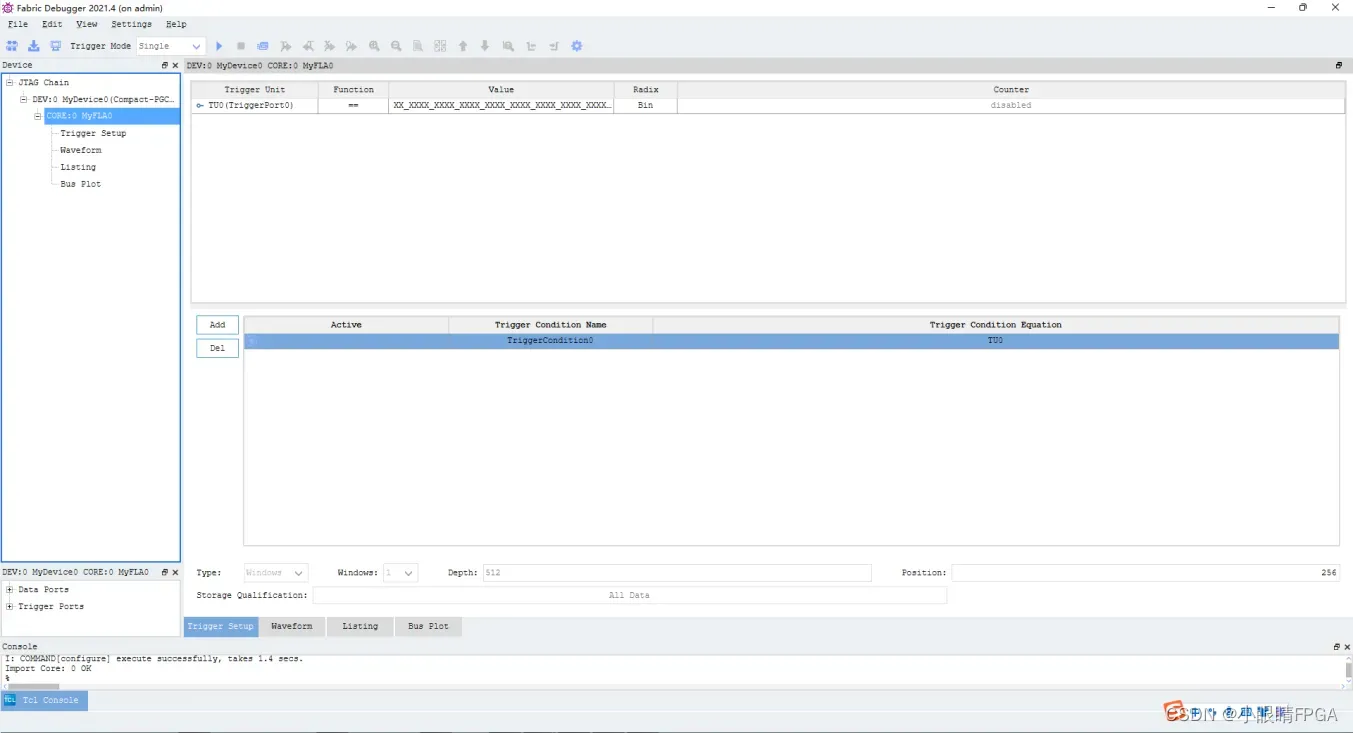

Debugger 主界面

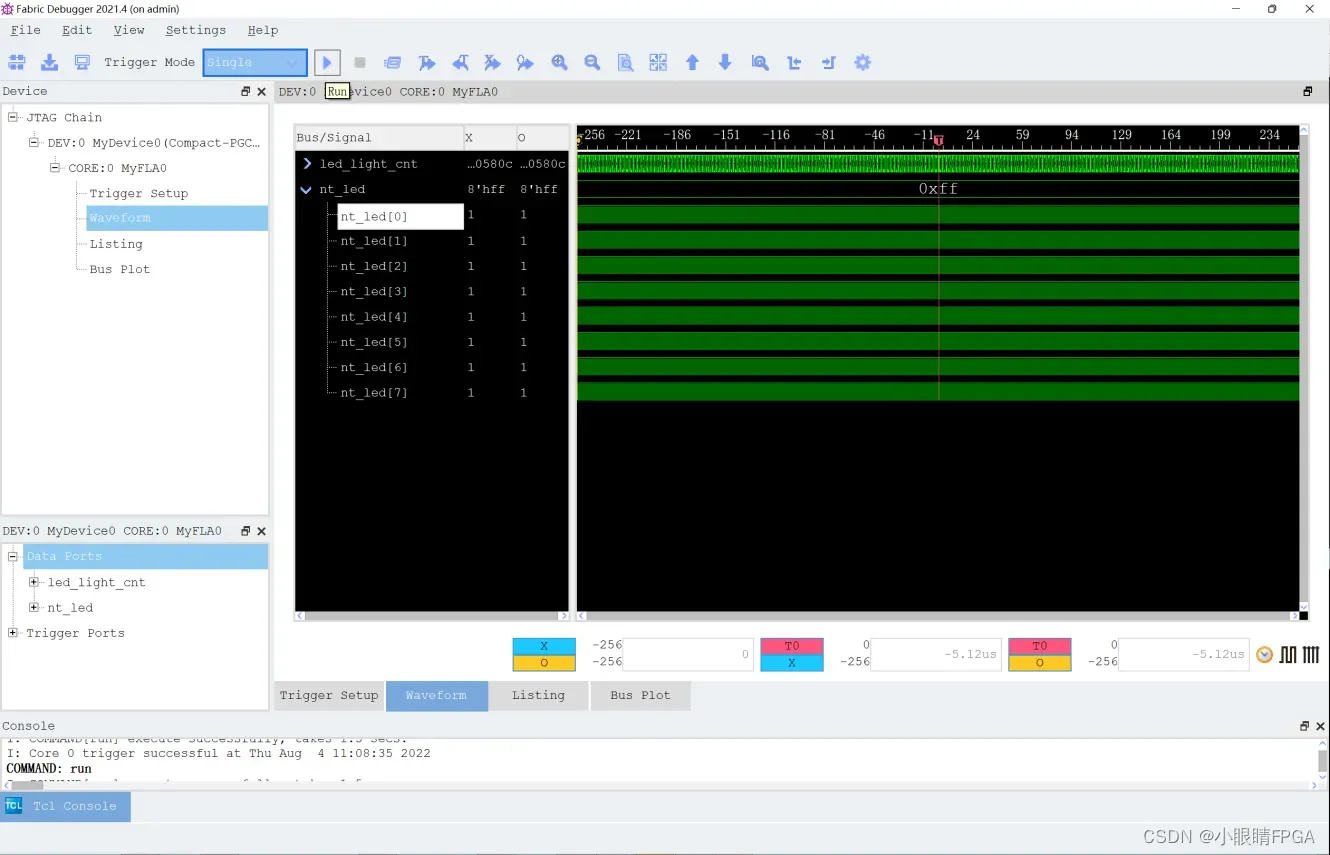

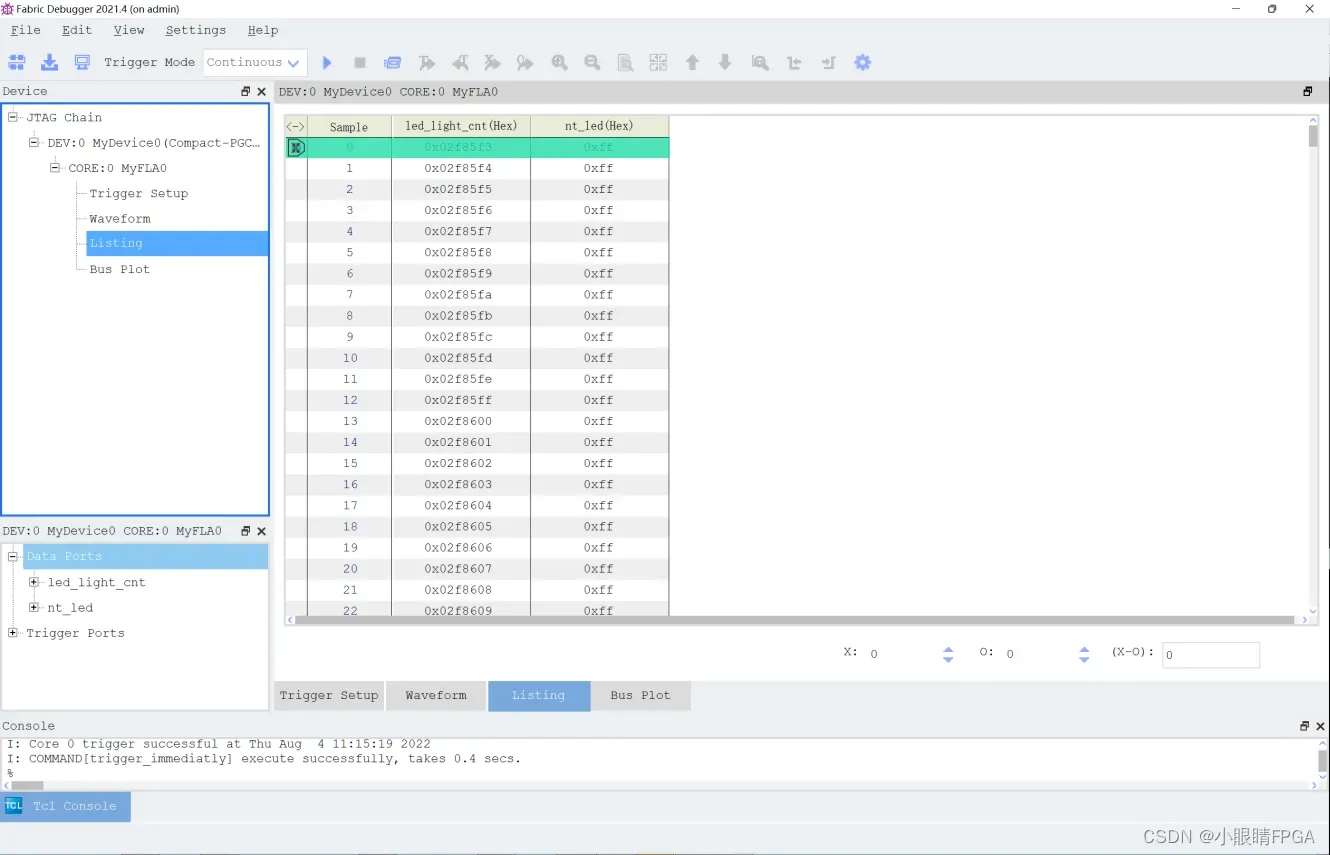

Trigger Mode 设置触发方式(单触发和连续触发),点击 Run 触发条件会被载入到当前 的 DebugCore 中,该触发条件被满足或者用户手动结束前会一直存在于 DebugCore 中。一旦 触发条件被满足,当前的 DebugCore 会根据 Capture Settings 的设置捕捉数据直到 buffer 被填满,接着数据被 Debugger 接受并显示于 Waveform、Listing 对话框中。

Waveform 对话框中

Waveform 对话框中

Listing 对话框中

文章出处登录后可见!