时钟约束是FPGA工程最基础也是最重要的约束。

1.创建时钟约束 create_clock

对于外部晶振输入进FPGA的时钟需要进行时钟声明,周期和相位约束,对于差分时钟来说,只需要约束p端口就可以了。

create_clock

[-name CLOCK_NAME] [-period PERIOD]

[-waveform {UP_EDGE DOWN_EDGE} ] [get_ports PORT_NAME]

//注:该命令的选项和参数顺序任意

//例子

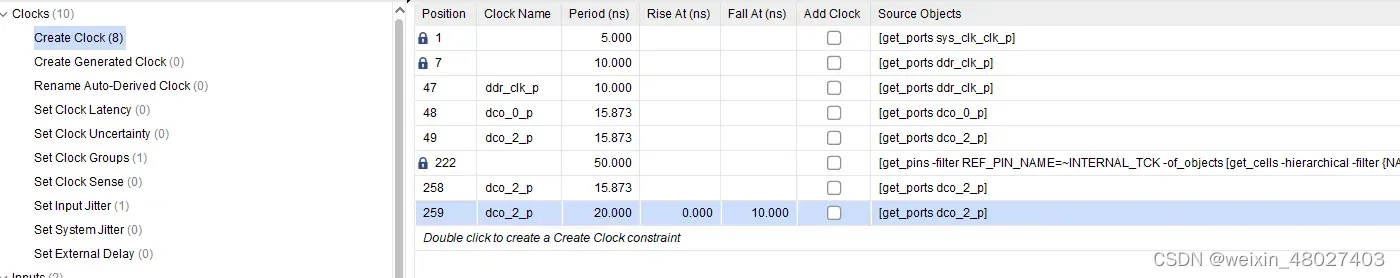

create_clock -period 20 -name dco_2_p -waveform {0 10} [get_ports dco_2_p]打开Timing Constrains窗口可以看到,约束已经添加进设计中

2.UltraScale 器件中的差分信号需要内部匹配电阻

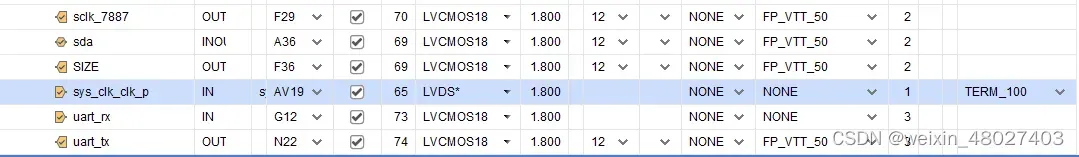

常用的有LVDS和LVDS_25这2种差分信号接口,LVDS标准仅在HPI/O bank中可用,要求输出和输入的Vcco供电电压为1.8V;HR I/O bank中提供了LVDS_25标准,要求输出和输入的Vcco供电电压为2.5V。作为接收时,匹配电阻在FPGA内部是可选项,具体由DIFF_TERM_ADV或DIFF_TERM,若外部开发板没有匹配电阻,需要设置DIFF_TERM_ADV =TERM_100或者DIFF_TERM = TRUE

set_property -dict {PACKAGE_PIN AV19 IOSTANDARD LVDS} [get_ports sys_clk_clk_p]

set_property DIFF_TERM_ADV TERM_100 [get_ports sys_clk_clk_p]

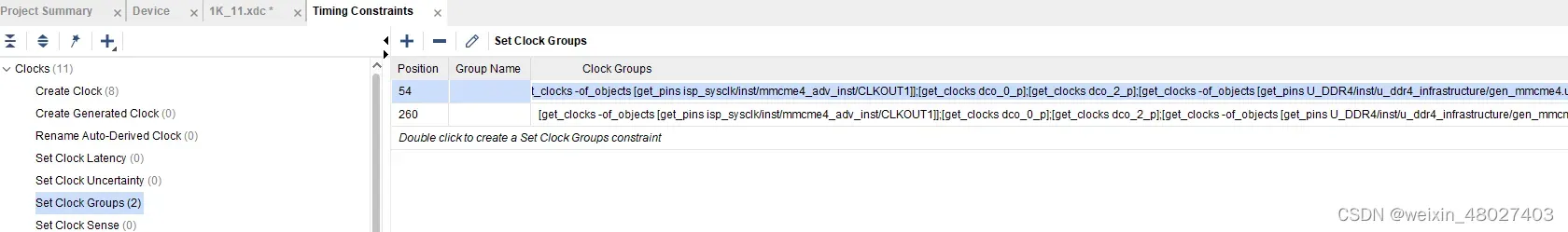

3.时钟异步分组约束

Vivado中时序分析工具默认会分析设计中所有时钟相关的时序路径,除非时序约束中设置了时钟组或false路径。使用set_clock_groups命令可以使时序分析工具不分析时钟组中时钟的时序路径。异步时钟和非扩展时钟是没法正确地进行时序分析, 在它们之间的时序路径在分析时应该使用set_clock_groups进行忽略。相比于其他时序例外的命令,set_clock_groups的优先级最高,如果需要对异步时钟进行分析,则不能对该时钟使用set_clock_groups命令。

例如:当工程中需要添加高速时钟驱动ila调试时,需要将给ila的时钟与数据时钟做异步分组,否则时序分析工具会优先保障高频时钟的时序状况。

set_clock_groups -asynchronous -group [get_clocks CLKOUT1] -group [get_clocks dco_0_p] -group [get_clocks dco_2_p]

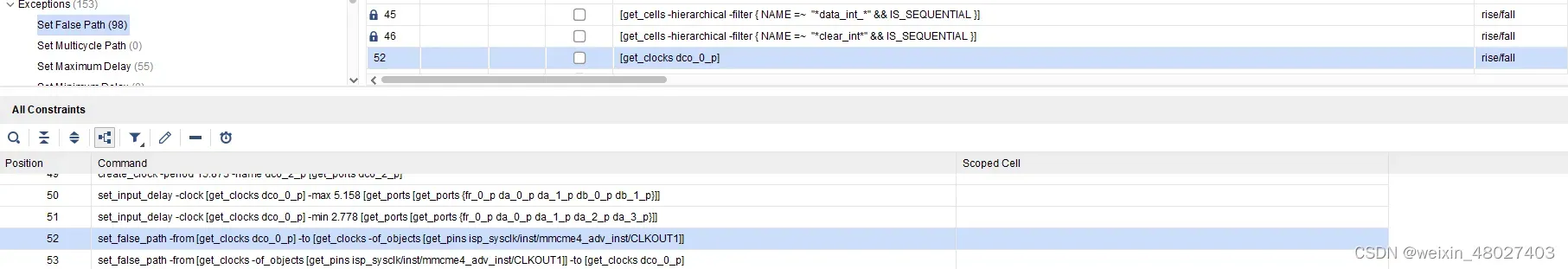

4.伪路径约束 set_false_path

vivado时序分析工具默认会分析设计中所有时钟相关的时序路径,但是对于一些时序上不需要关注的路径如跨时钟域中添加的进行两次同步的逻辑单元,只在FPGA通电启动时的寄存器,复位或测试的逻辑模块,异步的分布式RAM中读时钟和写时钟之间的路径等进行静态时序分析,减少编译时间,改善需要关注路径的时序状态。

因为如果非功能模块的路径存在时序违例时,工具可能尝试去修复这些违例,这不仅会导致设计因为逻辑复制而变大,也可能因为非功能模块有更大的违例而忽略了实际功能模块的违例问题。只有正确的设置约束才能获取最好的结果。

设置伪路径约束可以是CLKA和CLKB之间的所有路径为伪路径,也可以是为Cell pins,cells,I/O ports之间设置为伪路径。

set_false_path -from [get_clocks dco_0_p] -to [get_clocks -of_objects [get_pins isp_sysclk/inst/mmcme4_adv_inst/CLKOUT1]]

set_false_path -from [get_pins cool_driver1280_top_i/u_spi_7887/light_reg/C] -to [get_pins cool_driver1280_top_i/rst_clk_core_clk_controller/rst_n_d_reg/CLR]

5.位置约束LOC

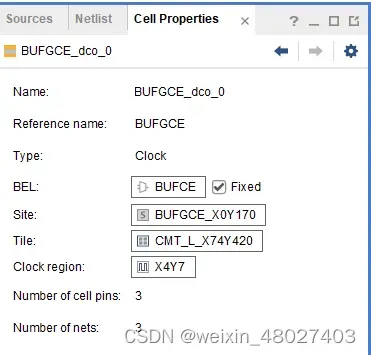

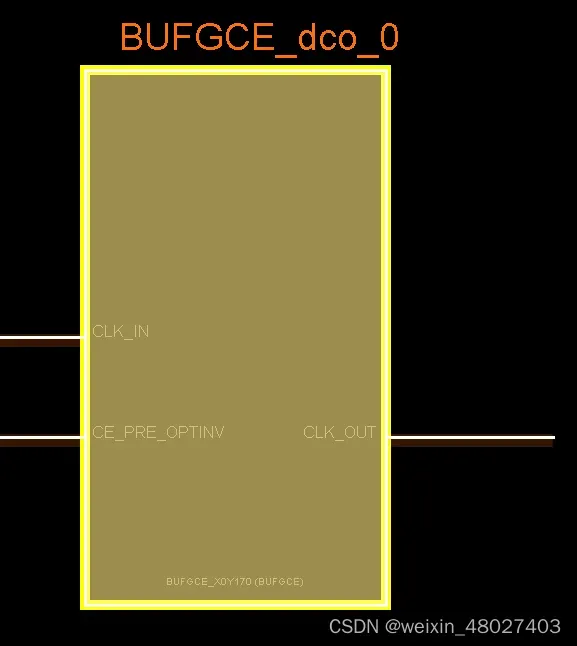

vivado完成布局布线后,每个cells都会在device中固化下来,但有些情况下时序分析工具对外部输入信号的实际状态不明确,分析出的路径在实际上版中并不适用,譬如实际工程中遇到ADC随路时钟进FPGA电路设计中未走FMC专用时钟口(走的是数据口)进入FPGA,该口附近没有全局BUFG资源,随路时钟进FPGA上树要斜跨整个FPGA到BUFG(vivado编译后的结果),输出时钟再斜挎整个FPGA返回来采集端口附近的数据,整个过程中路径延时太长,导致实际并不能采集到正确数据。最终通过手动进行LOC约束,给BUFGCE_dco_0选择一个相对近的路径,最终解决了时序问题。

set_property LOC BUFGCE_X0Y170 [get_cells BUFGCE_dco_0]

set_property LOC BUFGCE_X0Y210 [get_cells BUFGCE_dco_2]

#PLL 位置约束

set_property LOC PLLE2_ADV_X*Y* [get_cells cells路径及例化名]

#MMCM 位置约束

set_property LOC MMCME2_ADV_X*Y* [get_cells cells路径及例化名]

#BUFG 位置约束

set_property LOC BUFGCTRL_X*Y* [get_cells cells路径及例化名]

#BUFH 位置约束

set_property LOC BUFHCE_X*Y* [get_cells cells路径及例化名]

#FIFO 位置约束

set_property LOC OUT_FIFO_X*Y* [get_cells cells路径及例化名]

set_property LOC IN_FIFO_X*Y* [get_cells cells路径及例化名]6.信号输入输出延时约束set_input_delay

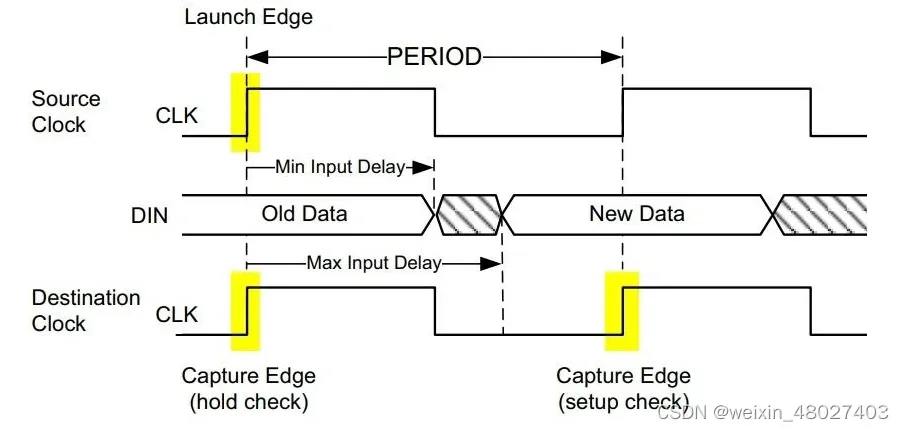

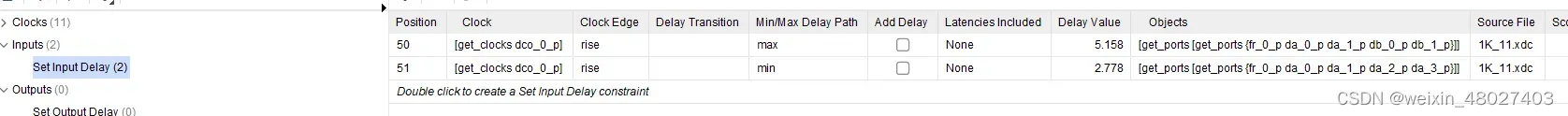

这个约束没有延迟的作用,如果需要对输入信号做延迟,就要使用IODELAY这种原语,本质上EDA工具会根据约束调整设计内部的器件类型,摆放的位置以及优化内部组合逻辑保证满足约束要求。

下面根据具体的芯片手册要求经行约束

set_input_delay -clock [get_clocks dco_0_p] -max 5.158 [get_ports [get_ports {fr_0_p da_0_p da_1_p db_0_p db_1_p}]]

set_input_delay -clock [get_clocks dco_0_p] -min 2.778 [get_ports [get_ports {fr_0_p da_0_p da_1_p da_2_p da_3_p}]]

版权声明:本文为博主作者:玲玲一原创文章,版权归属原作者,如果侵权,请联系我们删除!

原文链接:https://blog.csdn.net/weixin_48027403/article/details/136679481