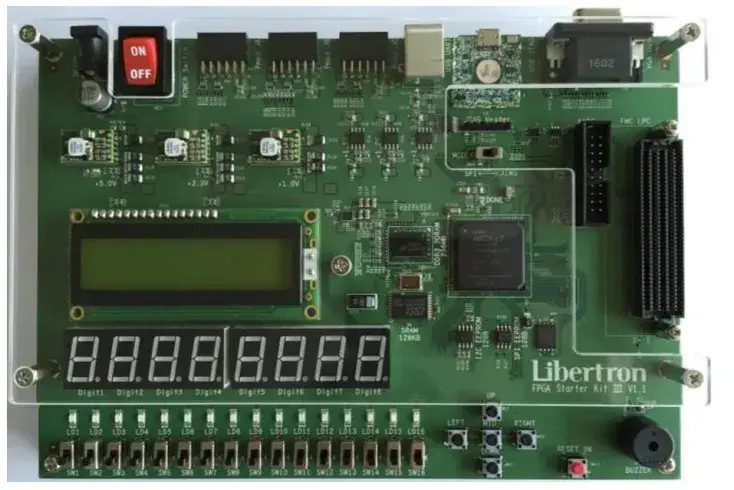

写在前面:本章主要内容为理解七点数码管显示的概念,并使用 Verilog 实现。生成输入信号后通过仿真确认各门的动作,通过 FPGA 检查在 Verilog 中实现的电路的操作。

Ⅰ. 前置知识

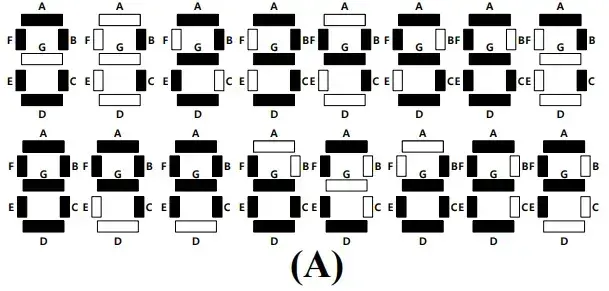

七段数码管是利用多重输出功能的非常有用的元件。该元件用于字符化,如十进制、十六进制数等。适当配置 7 个 元件,如图(a)所示,在每个端子上施加电压(logic “1”),使其发光,从而呈现字形(图b)。

数码管的一种是半导体发光器件,数码管可分为七段数码管和八段数码管,区别在于八段数码管比七段数码管多一个用于显示小数点的发光二极管单元 (decimal point)。

七段数码管的工作原理

多个发光二极管封装在一起的七段数码显示器按其连接形式可分为共正极显示器和共负极显示器。图7-1所示的共阳极和共阴极七段数码管,除显示数字必须是七笔外,还提供小数点。共阳极显示器的阳极连接在一起,向阳极提供正电压,阴极由限流电阻控制为高电平或低电平,以确定其是暗还是亮。共阴极显示器的阴极连接在一起,阴极可以接地,阴极可以由限流电阻控制为高电平或低电平,以确定它是亮还是暗。

Ⅱ. 练习(Assignment)

通过 (A) 完成真值表,通过真值表绘制出卡诺图,通过 Verilog 实现 0~F 并确认 Simulation 结果。

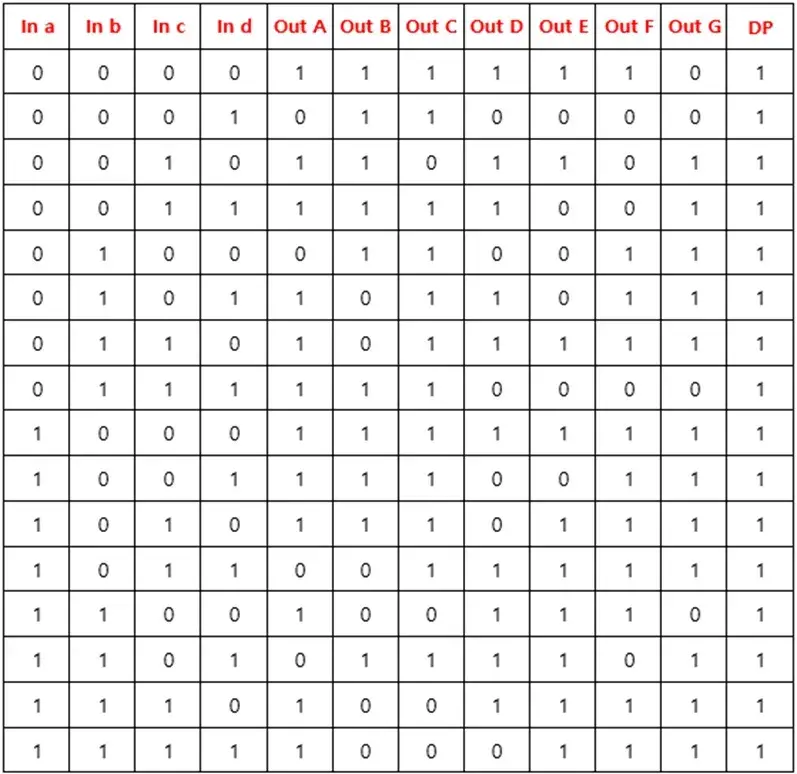

真值表:

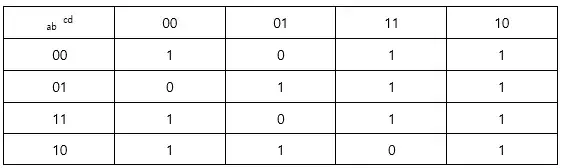

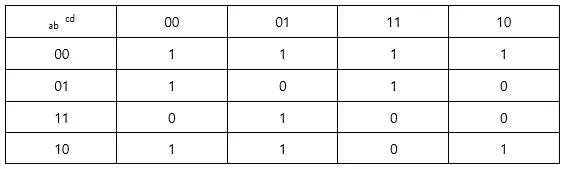

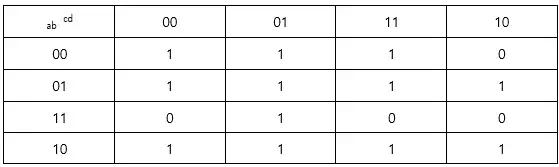

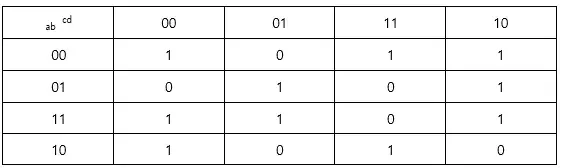

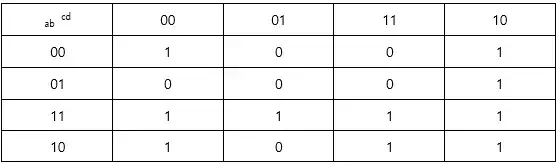

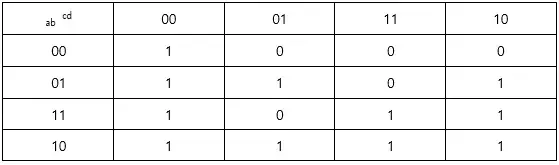

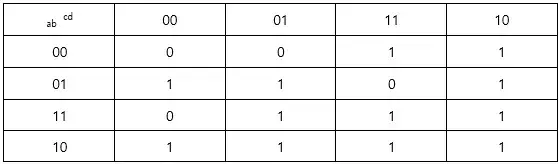

卡诺图:

a_out = b’d’+ad’+ab’c’+a’bd+a’c+bc

b_out = b’c’+b’d’+a’c’d’+a’cd+ac’d

c_out = a’b+ab’+c’d+a’c’+a’d

d_out = b’c’d’+b’cd+a’cd’+bc’d+abd’

e_out = b’d’+cd’+ab+ac

f_out = c’d’+bd’+a’bc’+ac+ab’

g_out = a’b’c+cd’+a’bc’+ab’+ad

💬 Design source:

`timescale 1ns / 1ps

module seven_segment(

input a, b, c, d,

output A, B, C, D, E, F, G, DP, digit

);

assign A = (b & c) | (~a & c) | (a & ~d) | (~b & ~d) | (~a & b & d) | (a & ~b & ~c);

assign B = (~b & ~d) | (~b & ~c) | (~a & c & d) | (a & ~c & d) | (~a & ~c & ~d);

assign C = (~c & d) | (~a & d) | (a & ~b) | (~a & b) | (~b & ~c);

assign D = (~a &c & ~d) | (~b & c & d) | (b & ~c & d) | (a & b & ~d) | (~b & ~c & ~d);

assign E = (c & ~d) | (a & c) | (a & b) | (~b & ~d);

assign F = (a & c) | (a & ~b) | (b & ~d) | (~c & ~d) + (~a & b & ~c);

assign G = (a & c) | (~b & c) | (a & ~b) | (b & ~c & d) | (~a & b & ~d);

assign digit =A|B|C|D|E|F|G;

assign DP = 1;

endmodule

💬 Testbench:

`timescale 1ns / 1ps

module seven_segment_tb;

reg aa, bb, cc, dd;

wire A, B, C, D, E, F, G, DP, digit;

seven_segment u_seven_segment(

.a(aa),

.b(bb),

.c(cc),

.d(dd),

.A(A),

.B(B),

.C(C),

.D(D),

.E(E),

.F(F),

.G(G),

.DP(DP),

.digit(digit)

);

initial aa = 1'b0;

initial bb = 1'b0;

initial cc = 1'b0;

initial dd = 1'b0;

always aa = #100 ~aa;

always bb = #200 ~bb;

always cc = #400 ~cc;

always dd = #800 ~dd;

initial begin

#1000

$finish;

end

endmodule

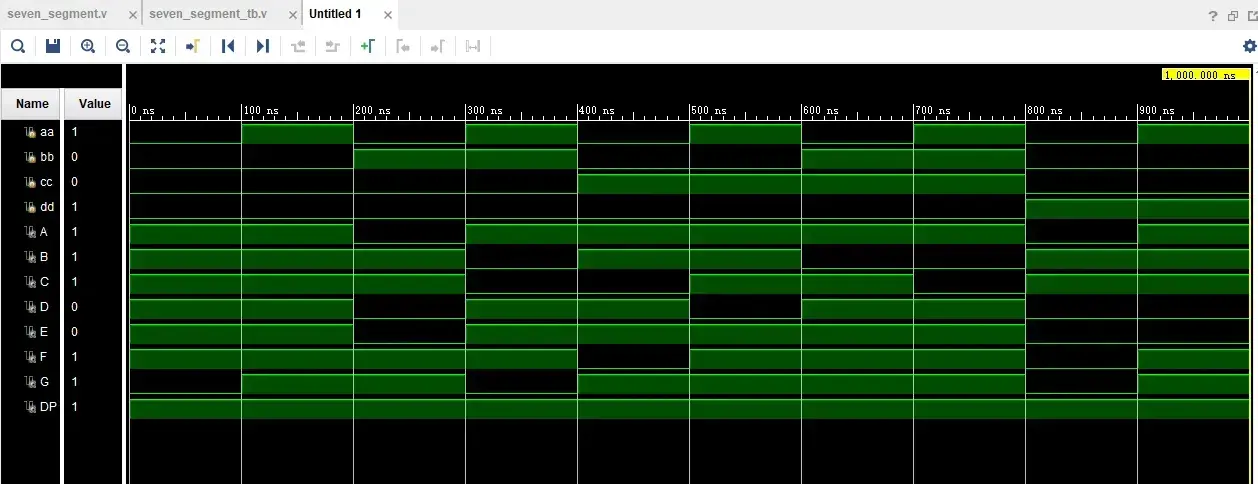

🚩 运行结果如下:

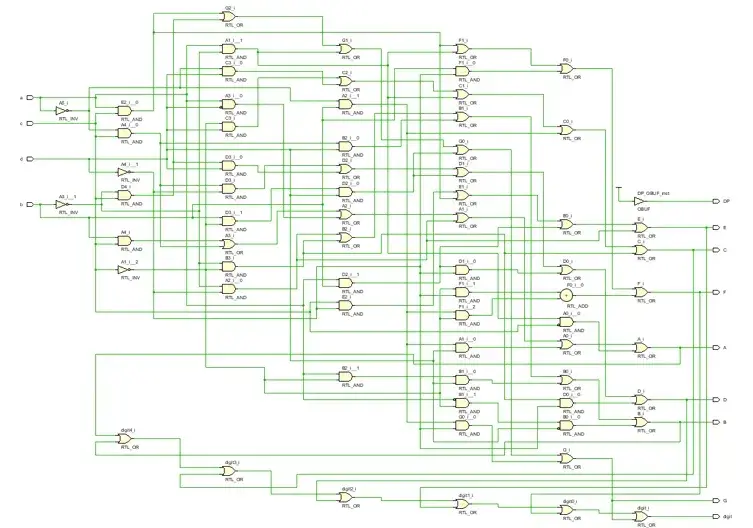

Schematic:

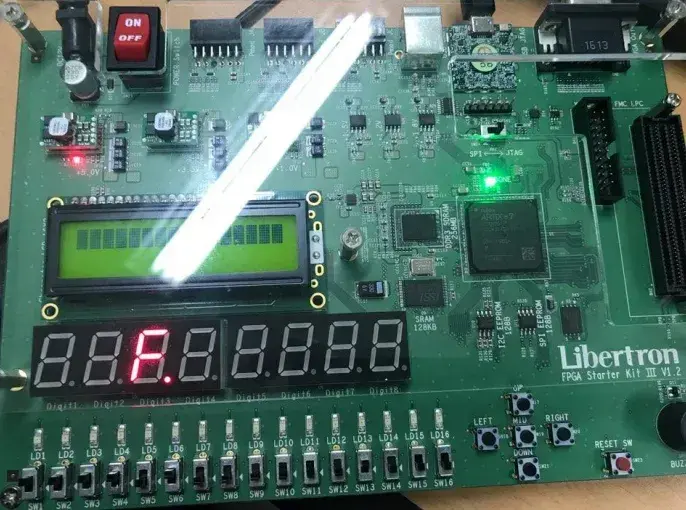

结果如下:

📌 [ 笔者 ] 王亦优

📃 [ 更新 ] 2023.2.19

❌ [ 勘误 ] /* 暂无 */

📜 [ 声明 ] 由于作者水平有限,本文有错误和不准确之处在所难免,

本人也很想知道这些错误,恳望读者批评指正!| 📜 参考资料 Introduction to Logic and Computer Design, Alan Marcovitz, McGrawHill, 2008 Microsoft. MSDN(Microsoft Developer Network)[EB/OL]. []. . 百度百科[EB/OL]. []. https://baike.baidu.com/. |

文章出处登录后可见!