最近,博主在学习FPGA,用的开发软件是ISE14.7,开发板是Spartan-3E starter board。本文主要记录下ISE14.7软件的使用,怎样从头开始建立工程,写代码,仿真,到下载bit流到板子上,还有程序的固化,用示波器看波形。最后还会记录下中间遇到的一些坑。

本文目录

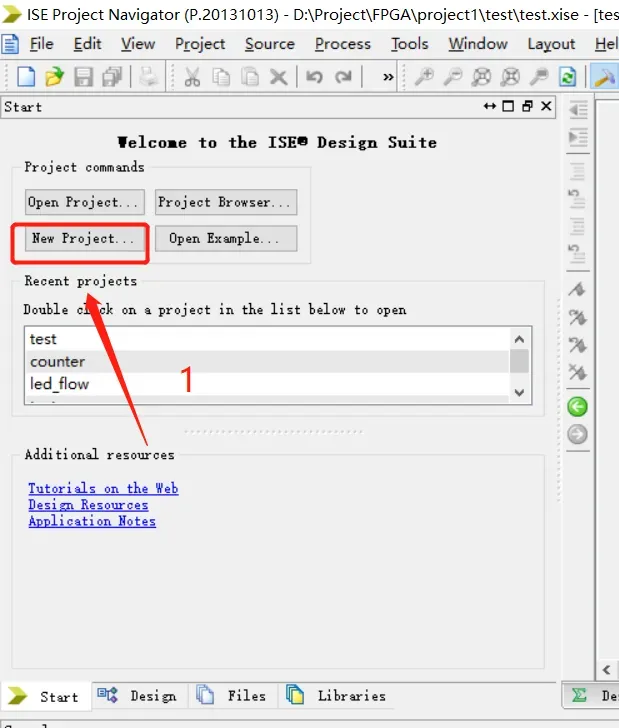

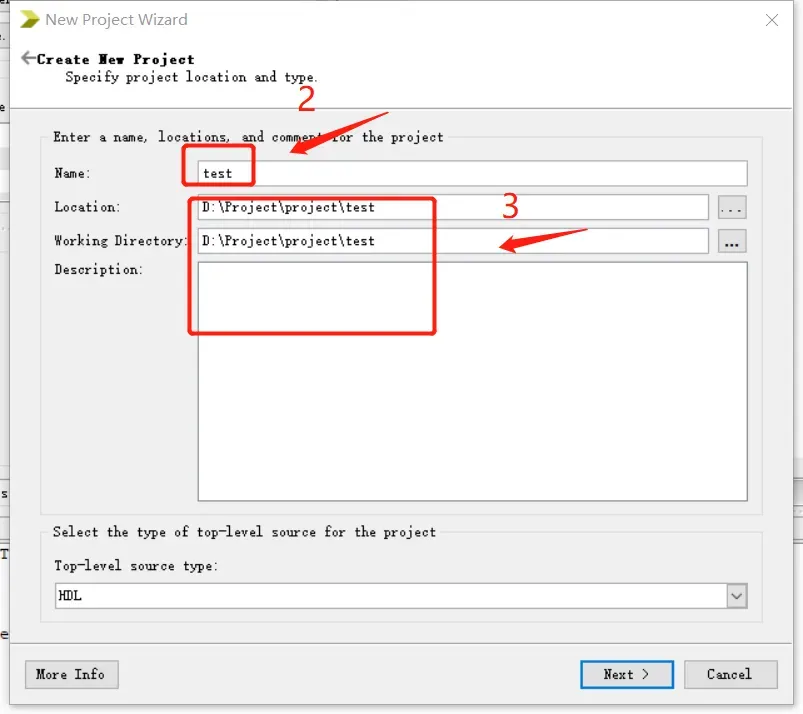

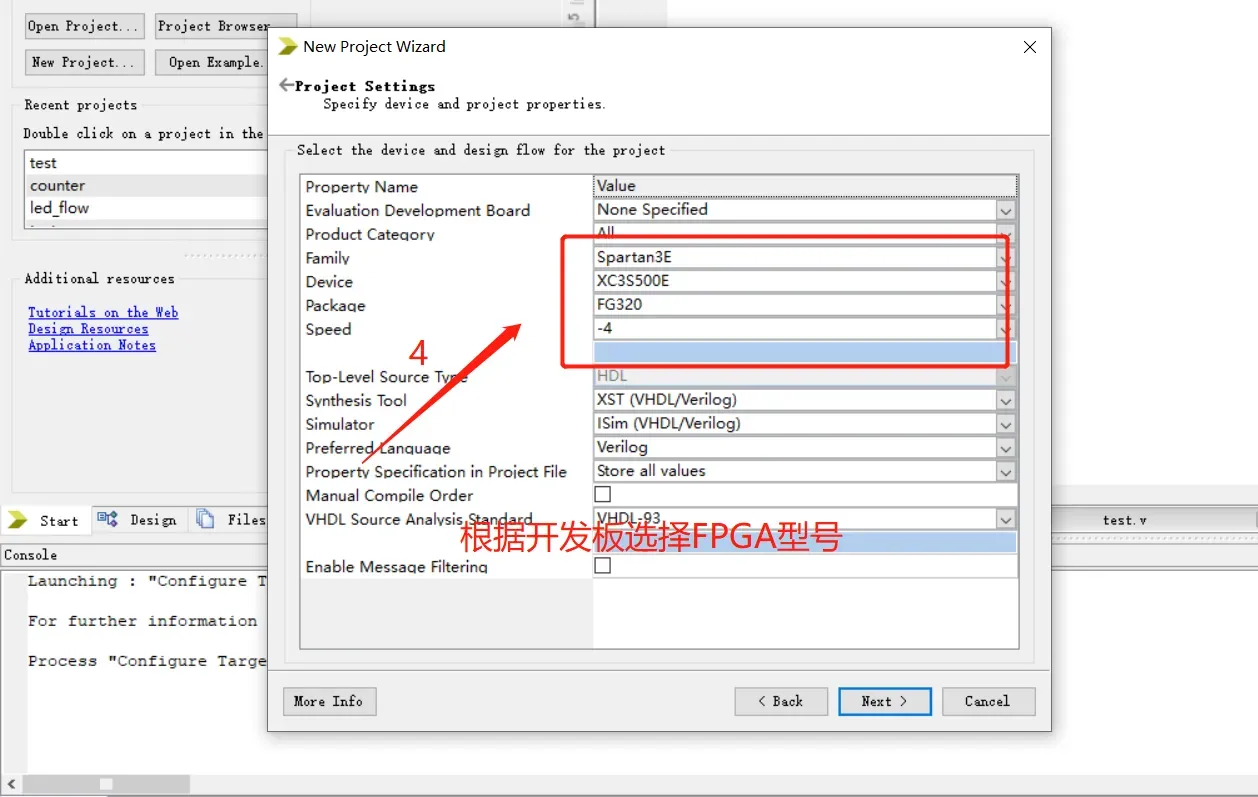

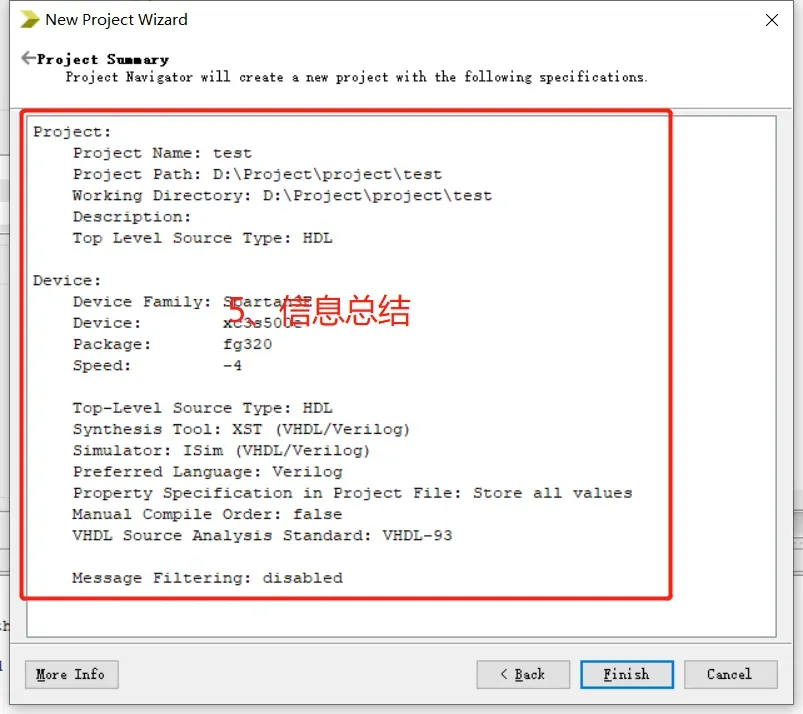

一、建立工程

1、新建工程

到这里,工程就新建完成了,接下来需要添加各种文件。下边是我的一段代码。

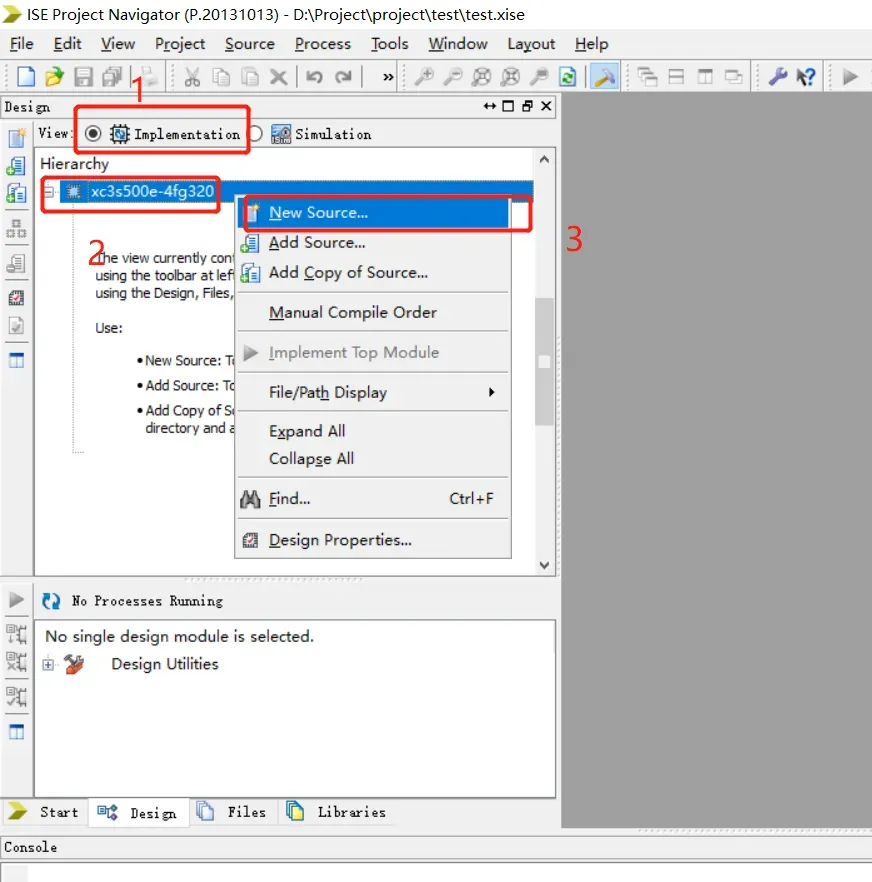

2、添加代码

在这里,我们可以创建新的代码文件(或者可以选择Add Sourse添加已有的代码)。

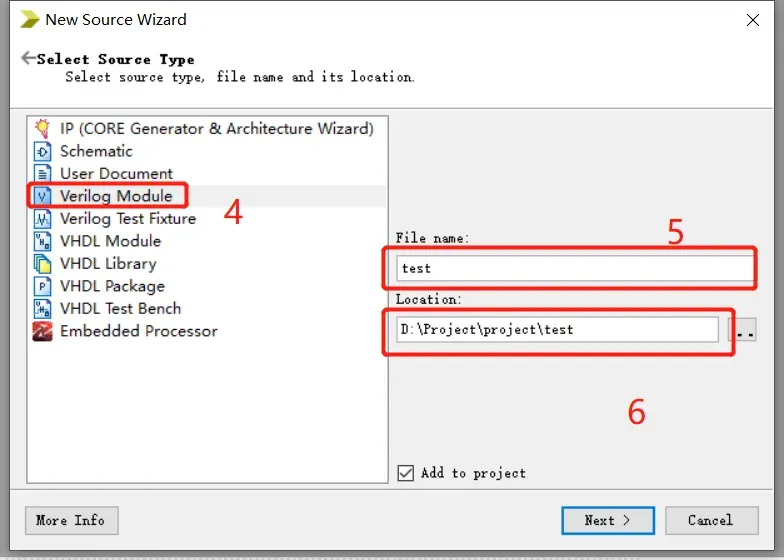

这里我用的是Verilog语言,所以选择了Verilog Module,如果你是VHDL语言,可以选择VHDL Module。

`timescale 1ns / 1ps

module led(

input clk,

input reset,

output reg[7:0]led

);

reg [25:0] cnt;

parameter TIME = 26'd50_000_000;

always @(posedge clk) begin

if (reset) begin

cnt <= 26'd0;

end

else if (cnt == TIME - 1'b1) begin

cnt <=26'd0;

end

else begin

cnt <= cnt + 1'd1;

end

end

always @(posedge clk) begin

if (reset) begin

led <= 8'b0000_0001;

end

else if (cnt == TIME - 1'b1) begin

led <= {led[0],led[7:1]};

end

else begin

led <= led;

end

end

endmodule

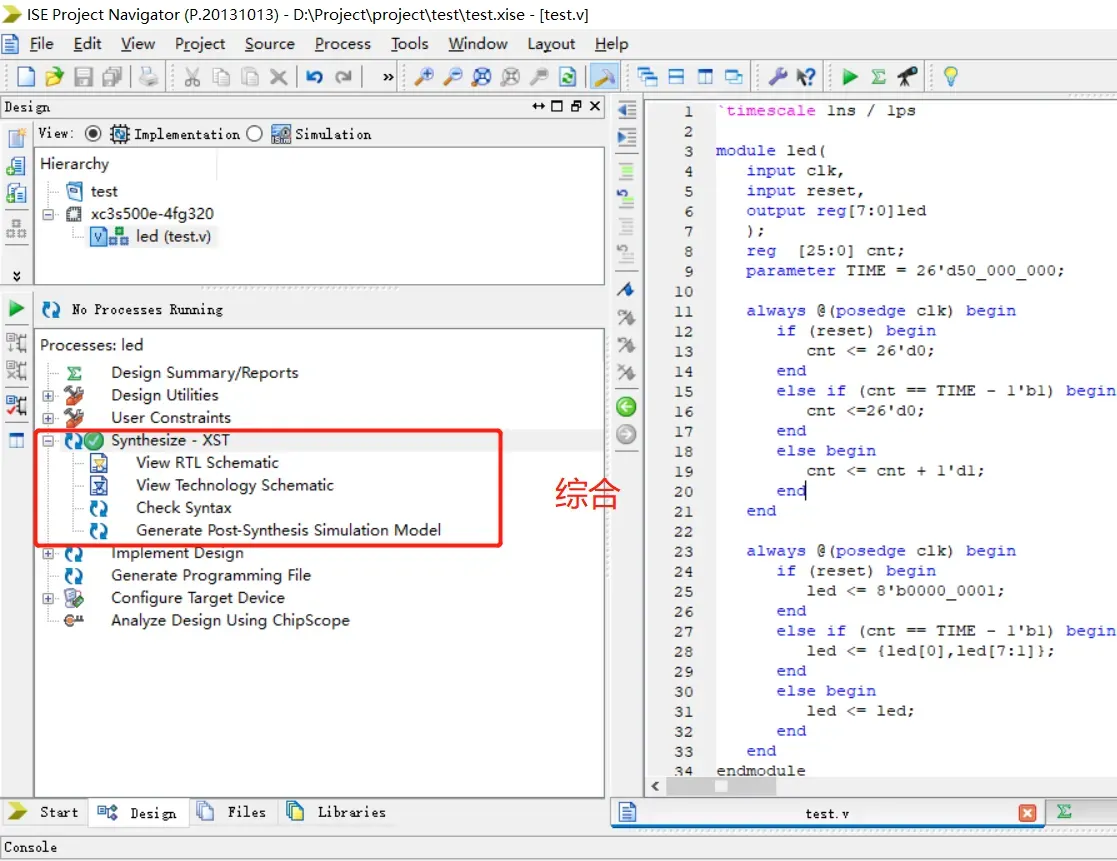

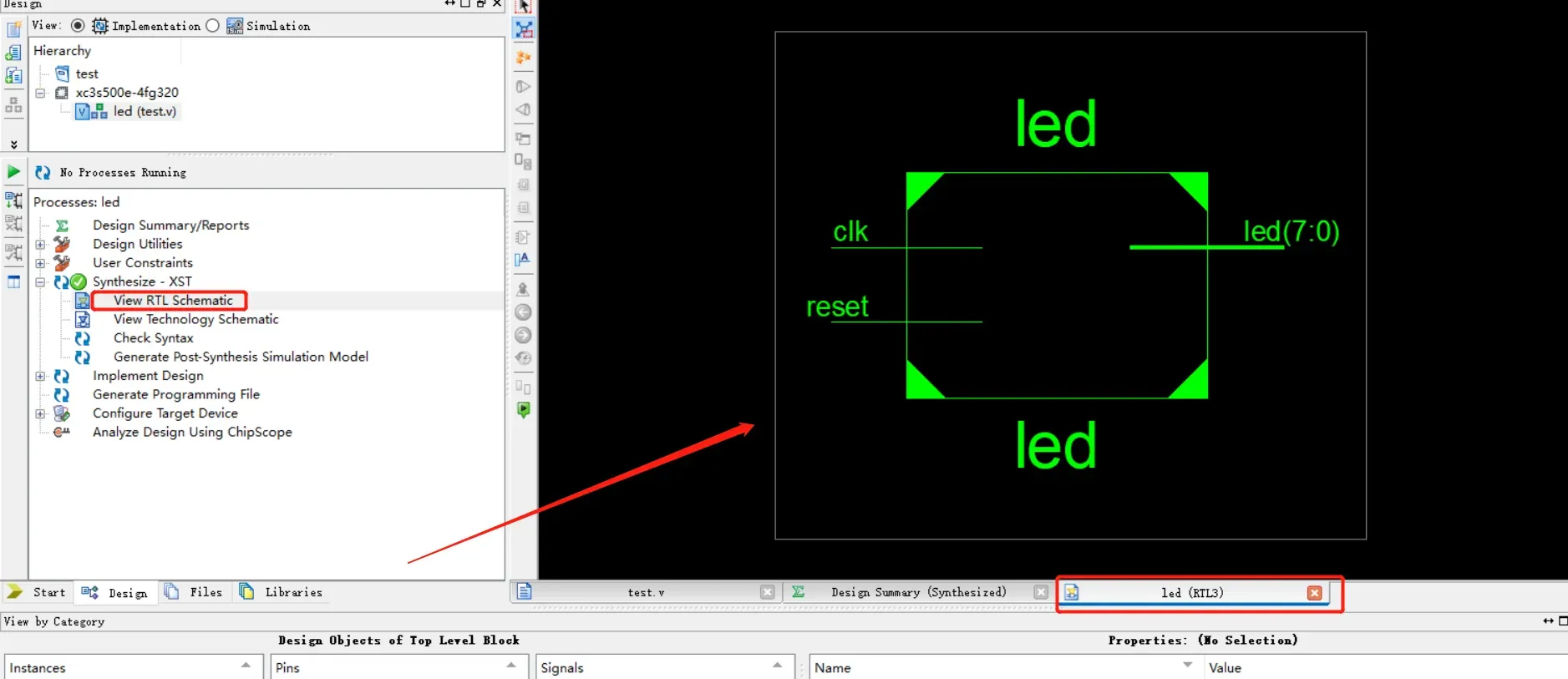

3、综合

这里,我们双击Synthesize -XST进行综合。可以检查代码的语法错误,查看RTL图等。前边出现绿色圈圈里对号,说明综合成功了。

可以双击View RTL Schematic查看RTL图。

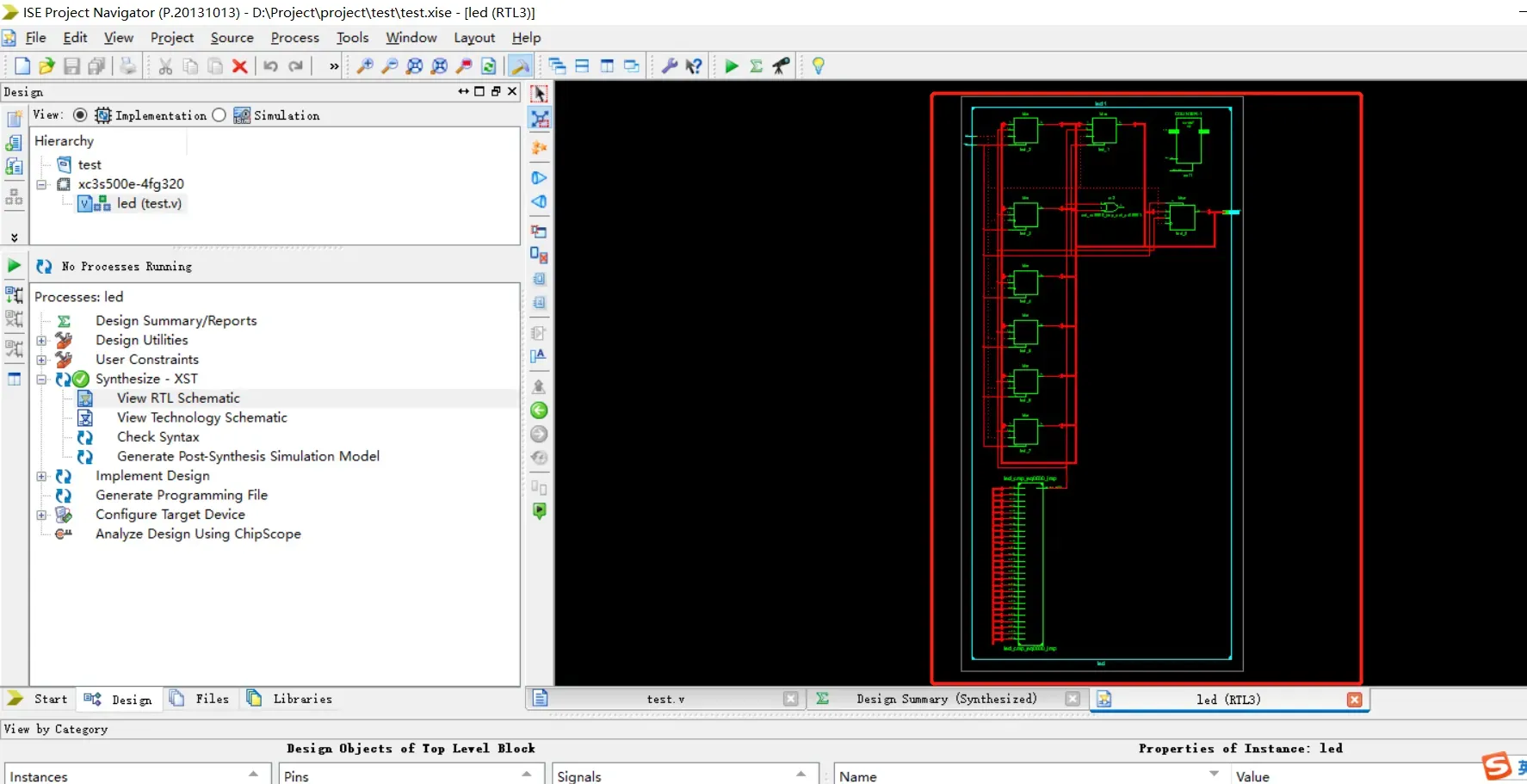

继续双击RTL图可以产看详细的图。

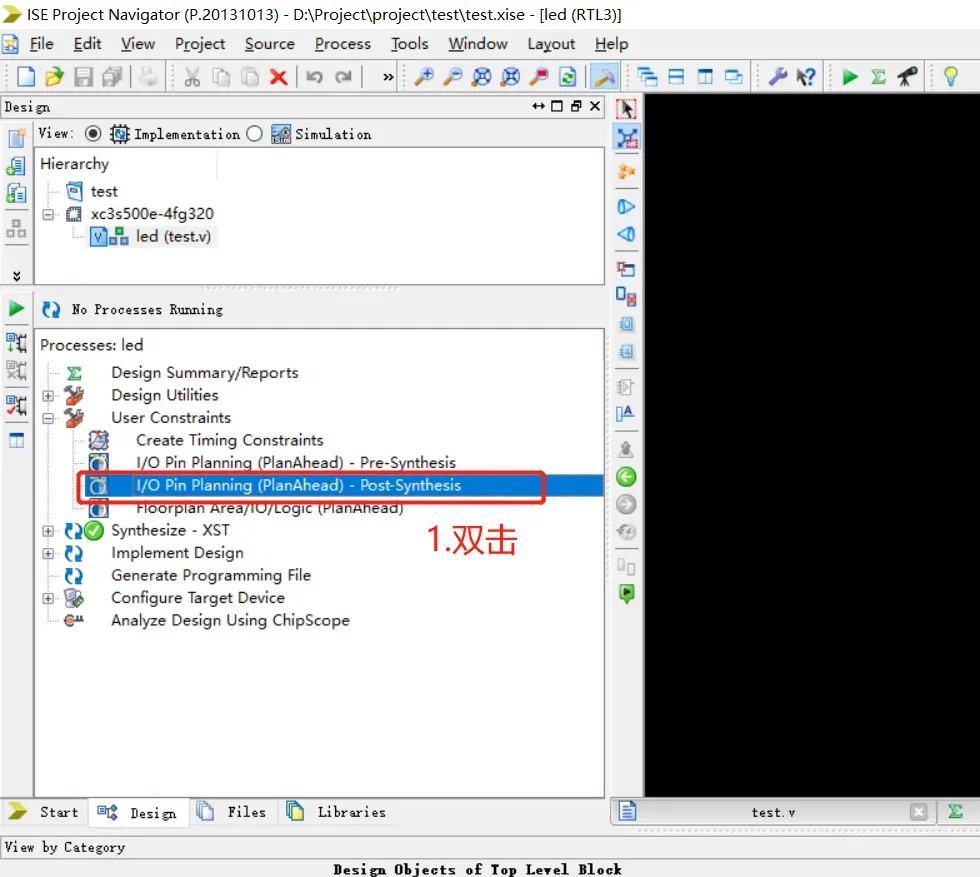

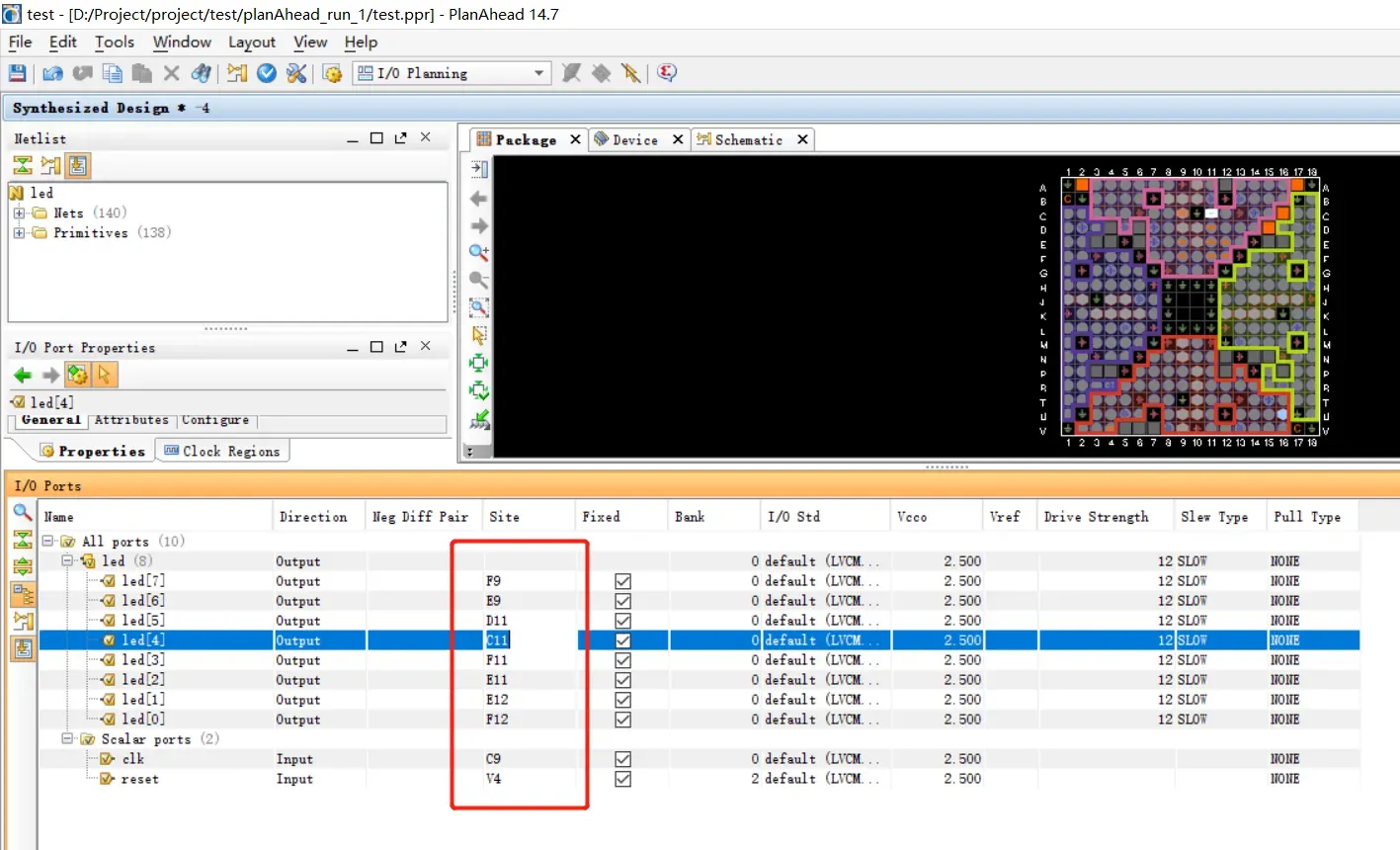

4、管脚约束

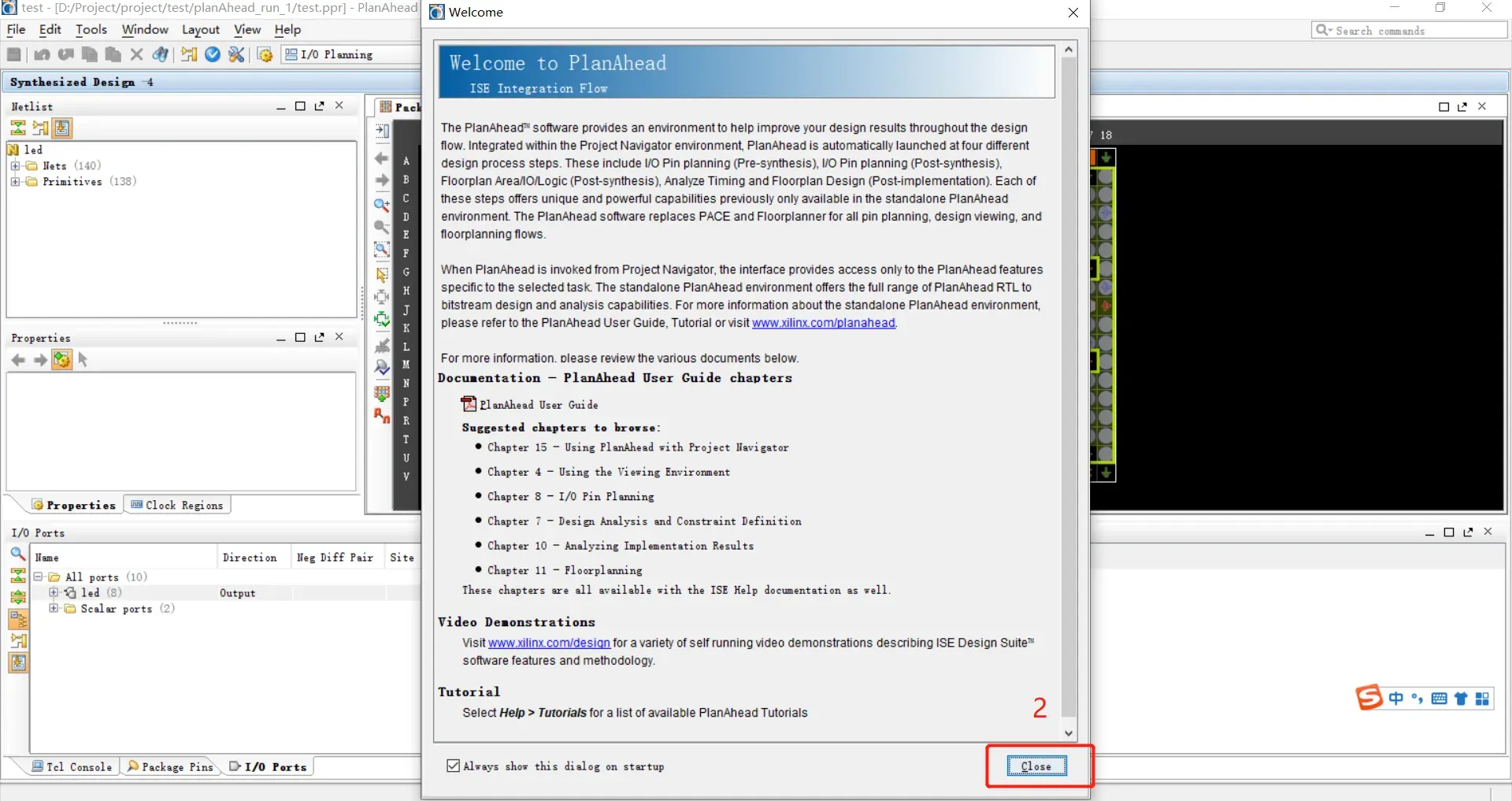

顾名思义,就是将我们设计中的input,output和FPGA对应的管脚相连接。

然后会打开PlanAhead,时间较久,需要稍等一会。

在这里,我们根据FPGA的数据手册分配管脚。

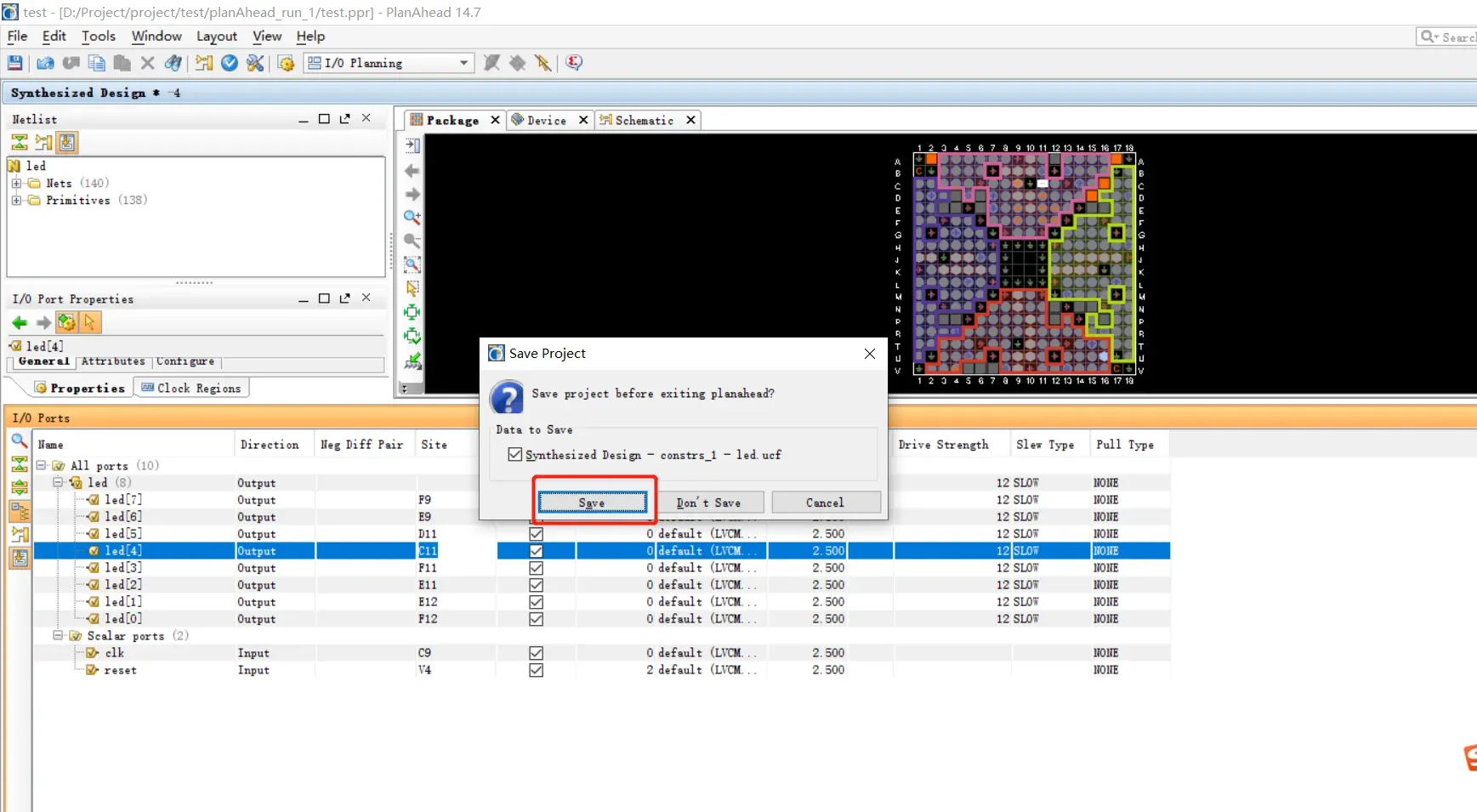

最后,save。

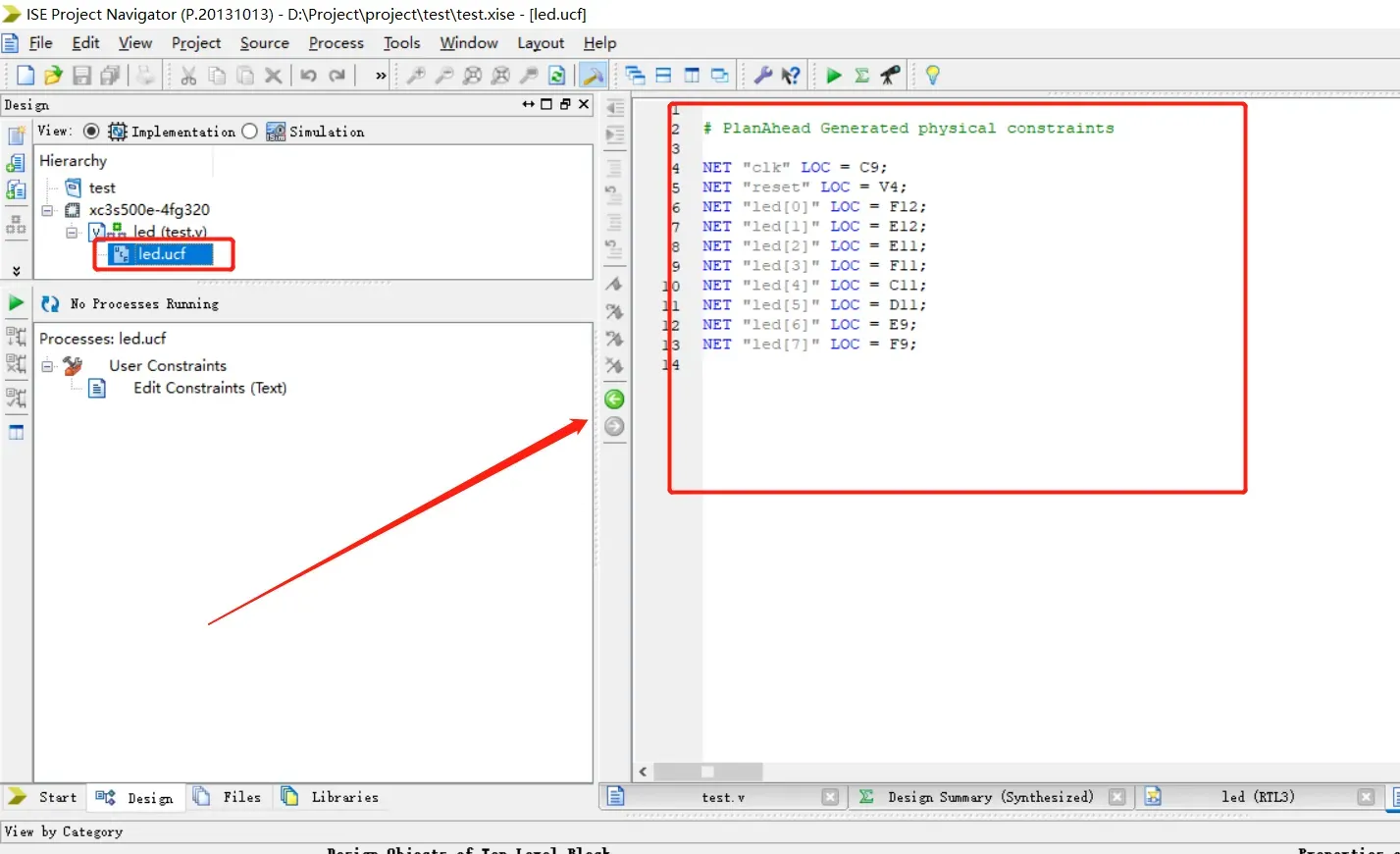

管脚约束完后,我们会看到有一个ucf文件。

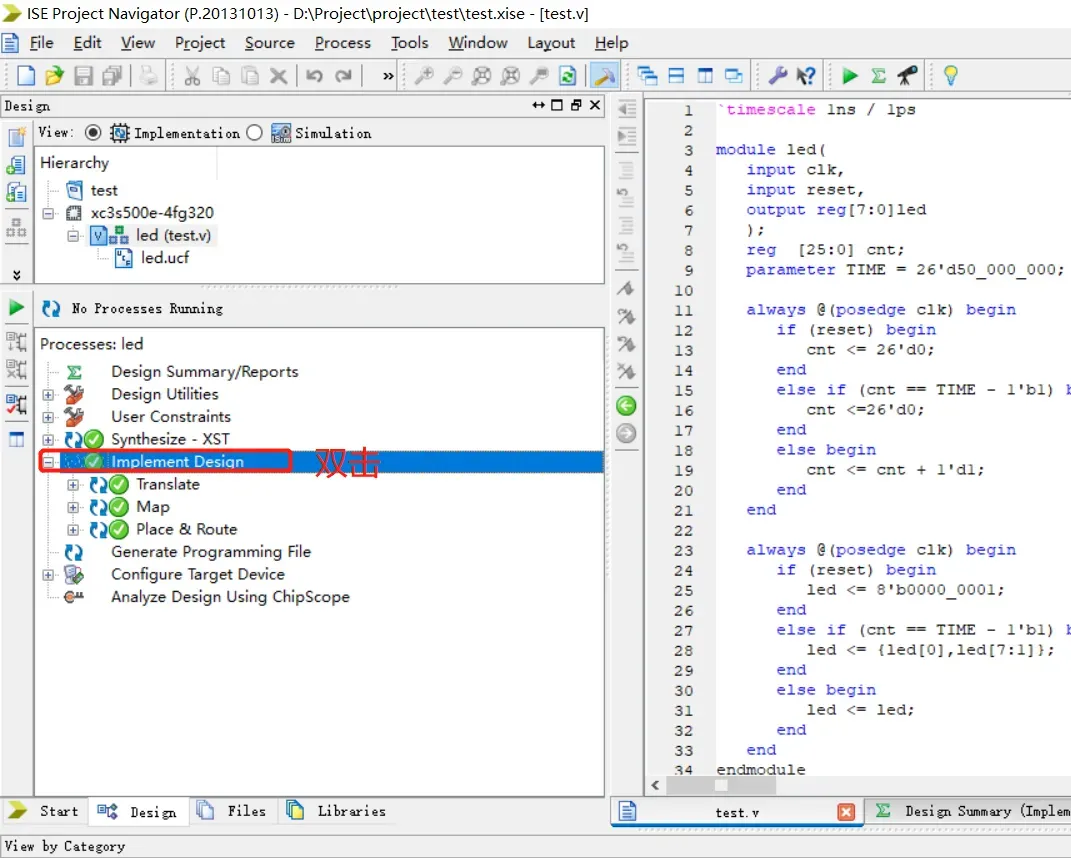

5、实现:转换、映射、布局布线

双击Implement Design,完成后前边会变绿。

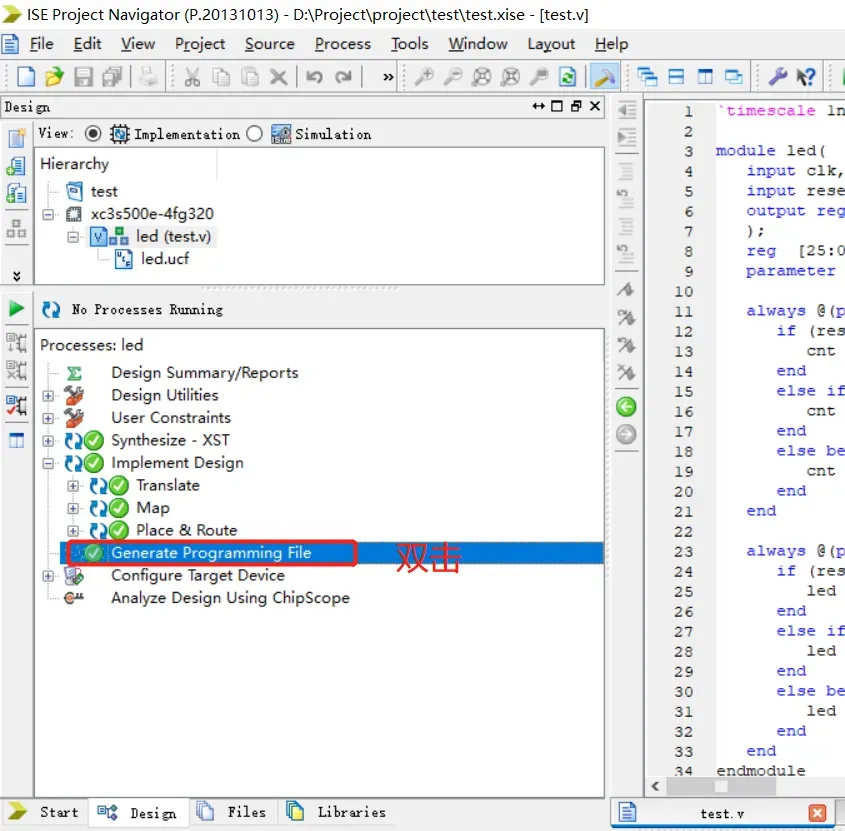

6、生成bit流文件

二、仿真

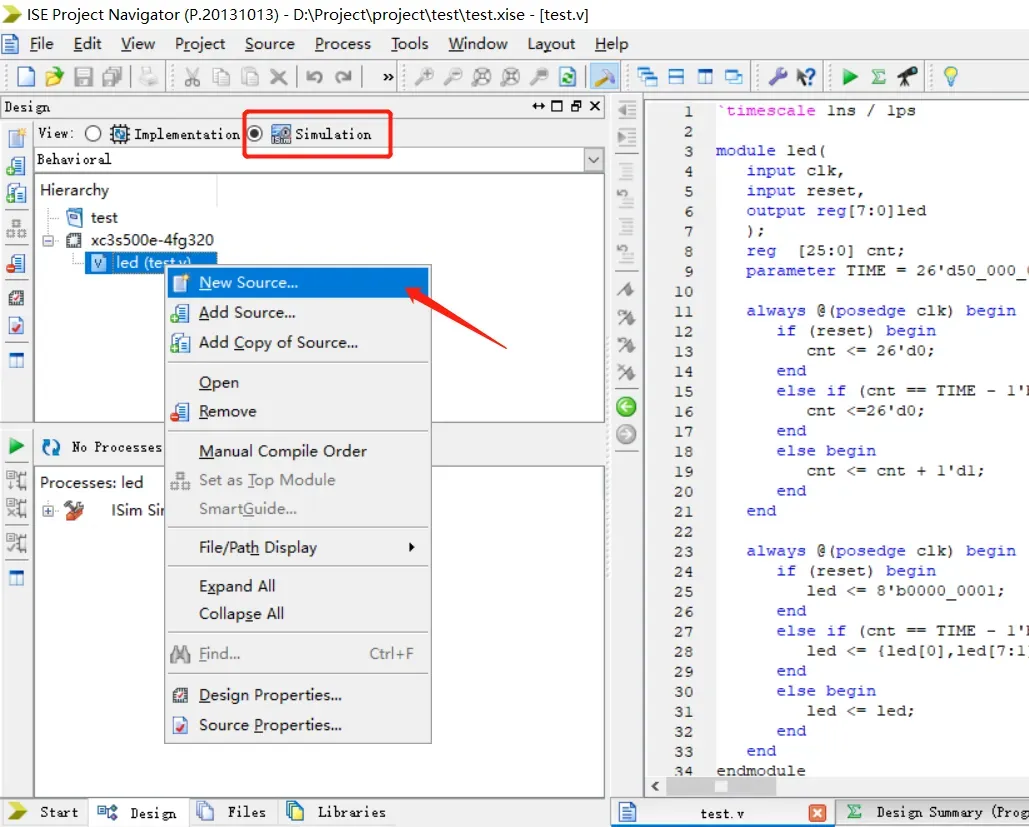

这里说的仿真,是对我们的代码进行功能仿真。可以用modelsim进行仿真,也可以在ISE内进行仿真。

用modelsim进项仿真可以参考文章:modelsim仿真

我们下边介绍的是在ISE14.7内进行仿真:

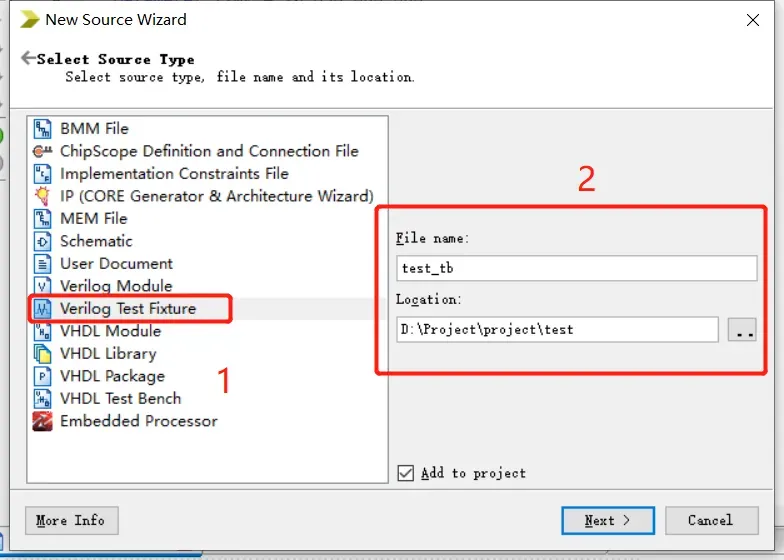

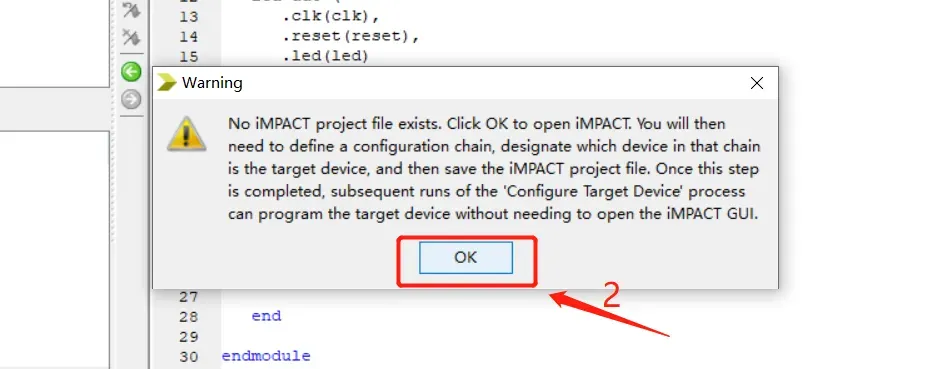

1、创建TestBench

输入testbench代码:

`timescale 1ns / 1ps

module test_tb;

// Inputs

reg clk;

reg reset;

// Outputs

wire [7:0] led;

// Instantiate the Unit Under Test (UUT)

led uut (

.clk(clk),

.reset(reset),

.led(led)

);

always #10 clk =~clk;

initial begin

// Initialize Inputs

clk = 0;

reset = 1;

// Wait 100 ns for global reset to finish

#100;

reset = 0;

// Add stimulus here

end

endmodule

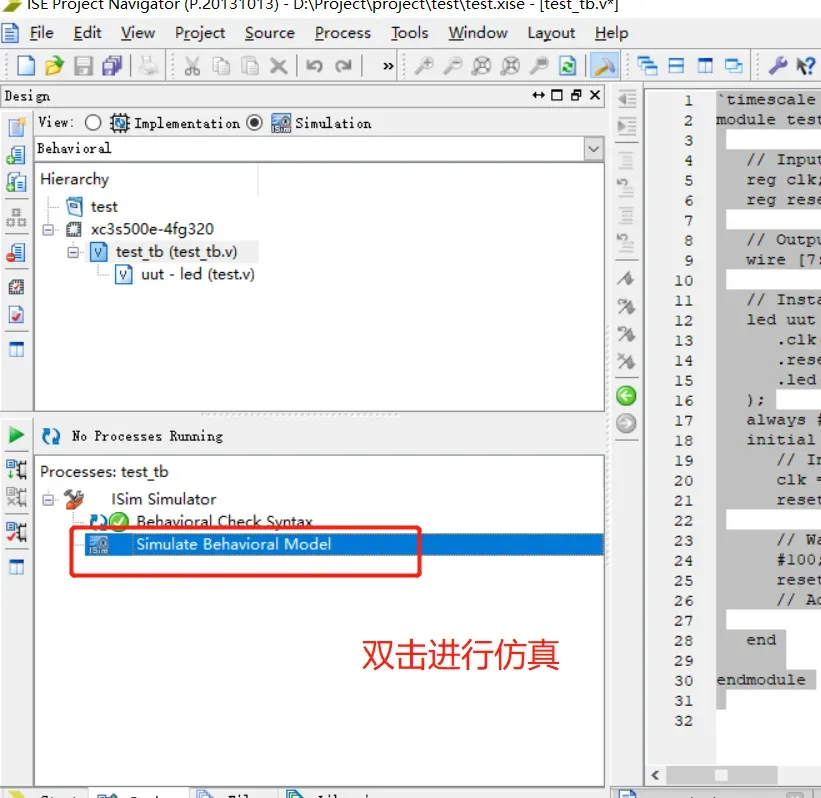

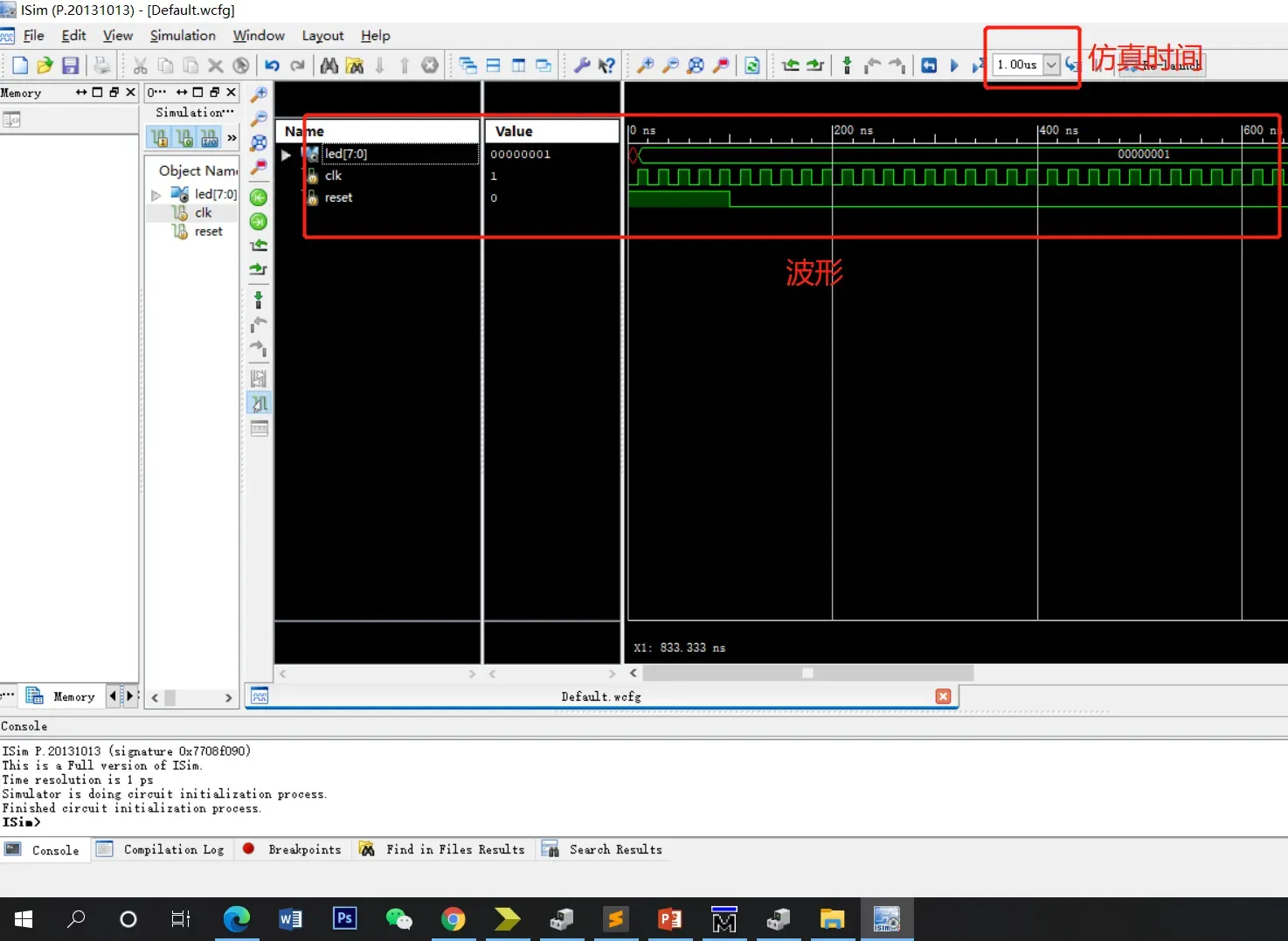

2、仿真

仿真成功后,可以将bit流下载到板子验证。

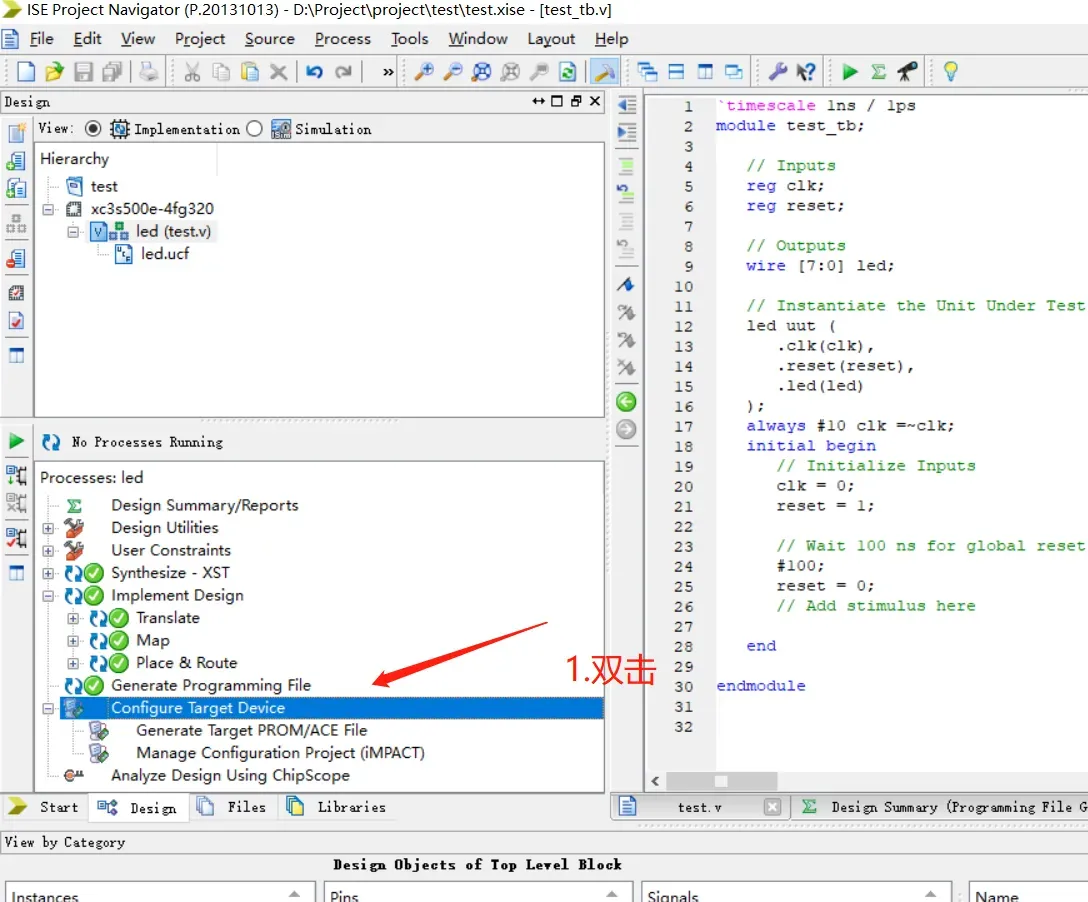

三、下载bit流文件到板子

下载bit文件到FPGA 的方式,掉电后会被擦除。

1、硬件连接

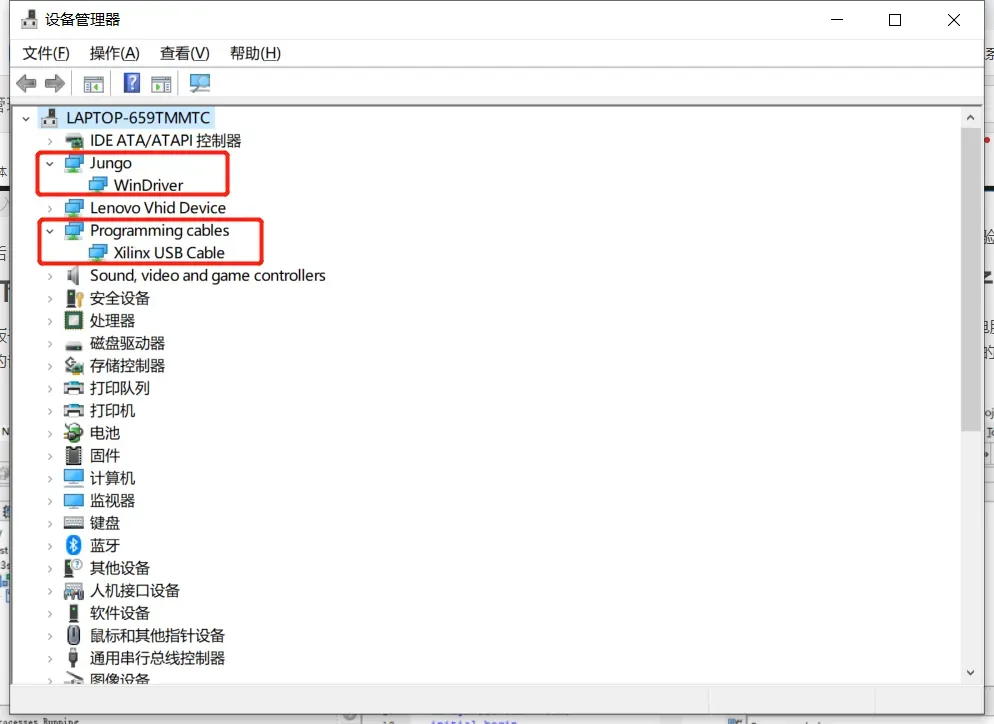

需要先将板子和电脑连接。当usb和电脑连接时,会自动加载驱动。

打开电脑的设备管理器,当出现下图的标志时说明连接成功:

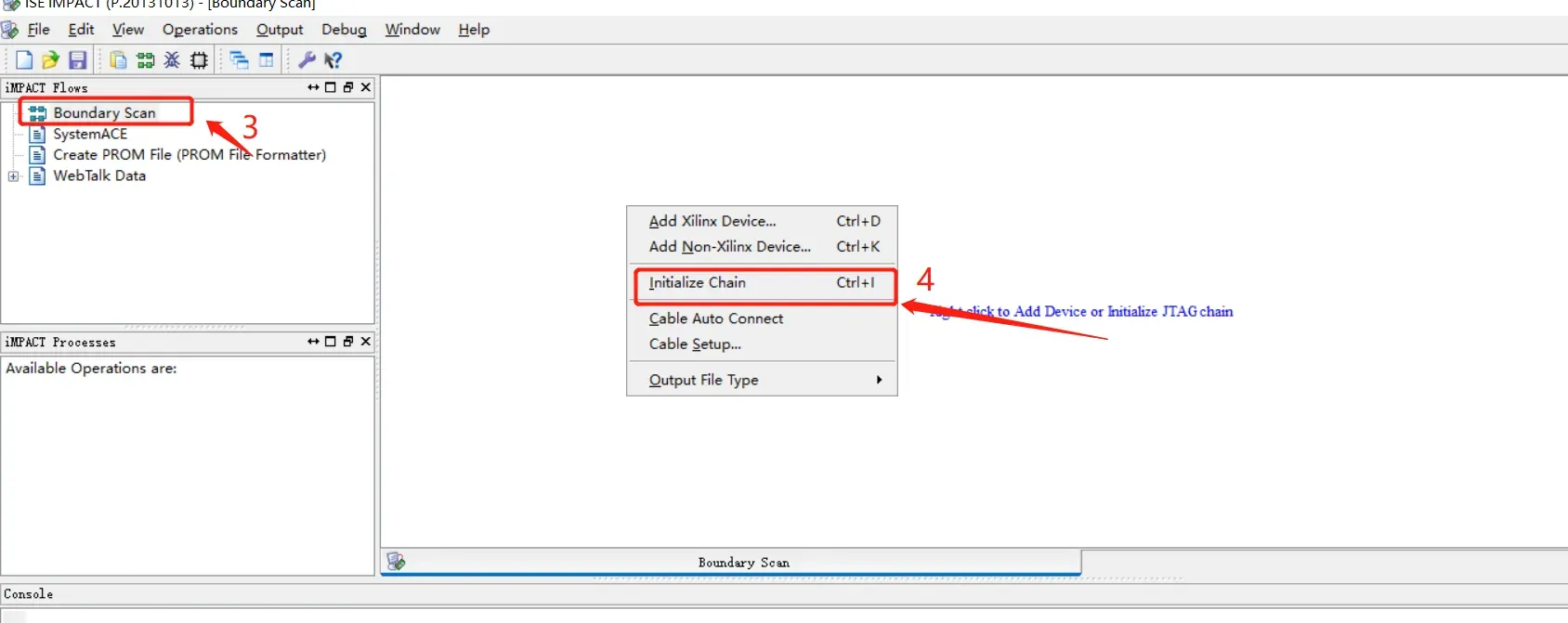

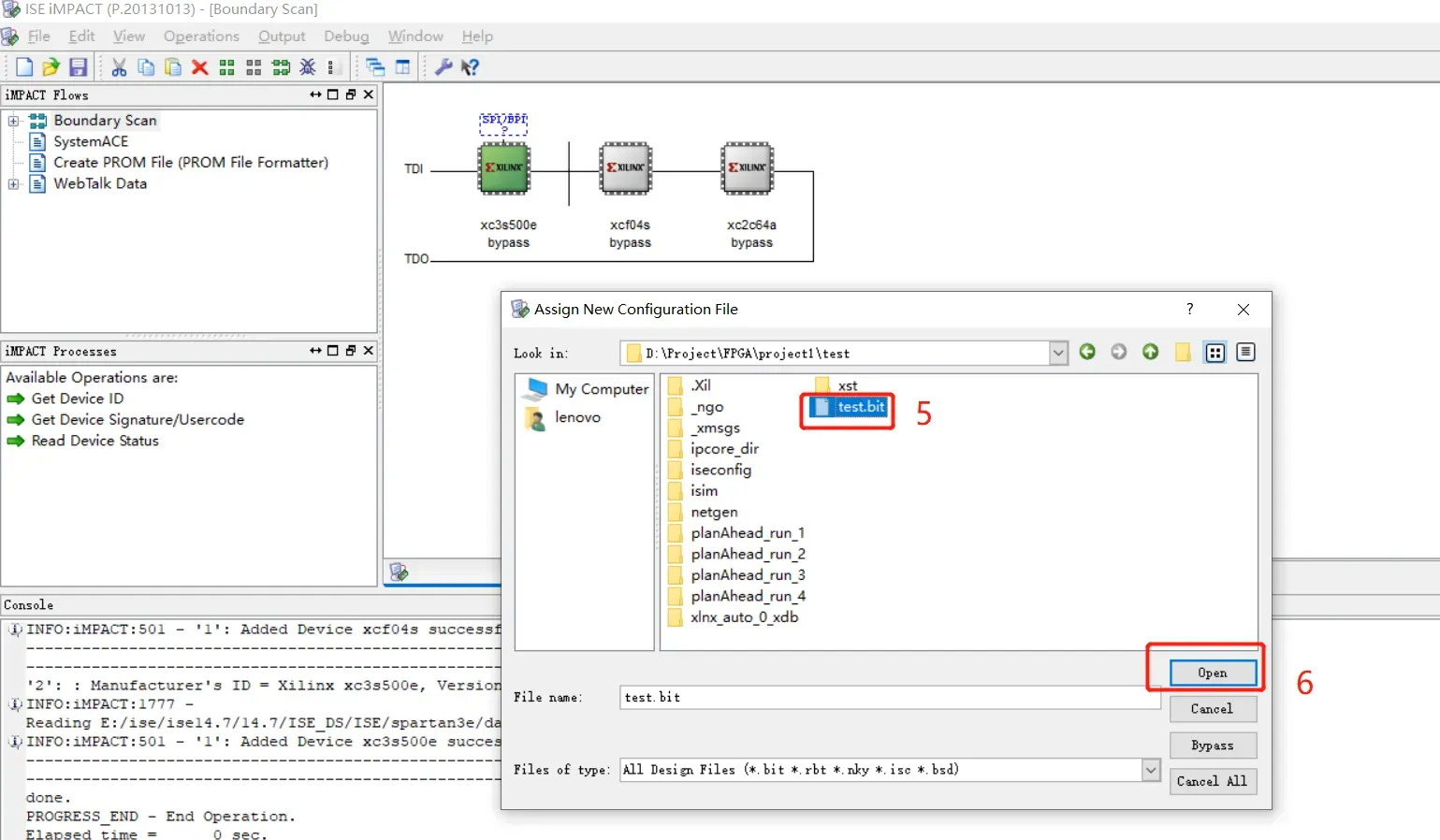

2、软件设置

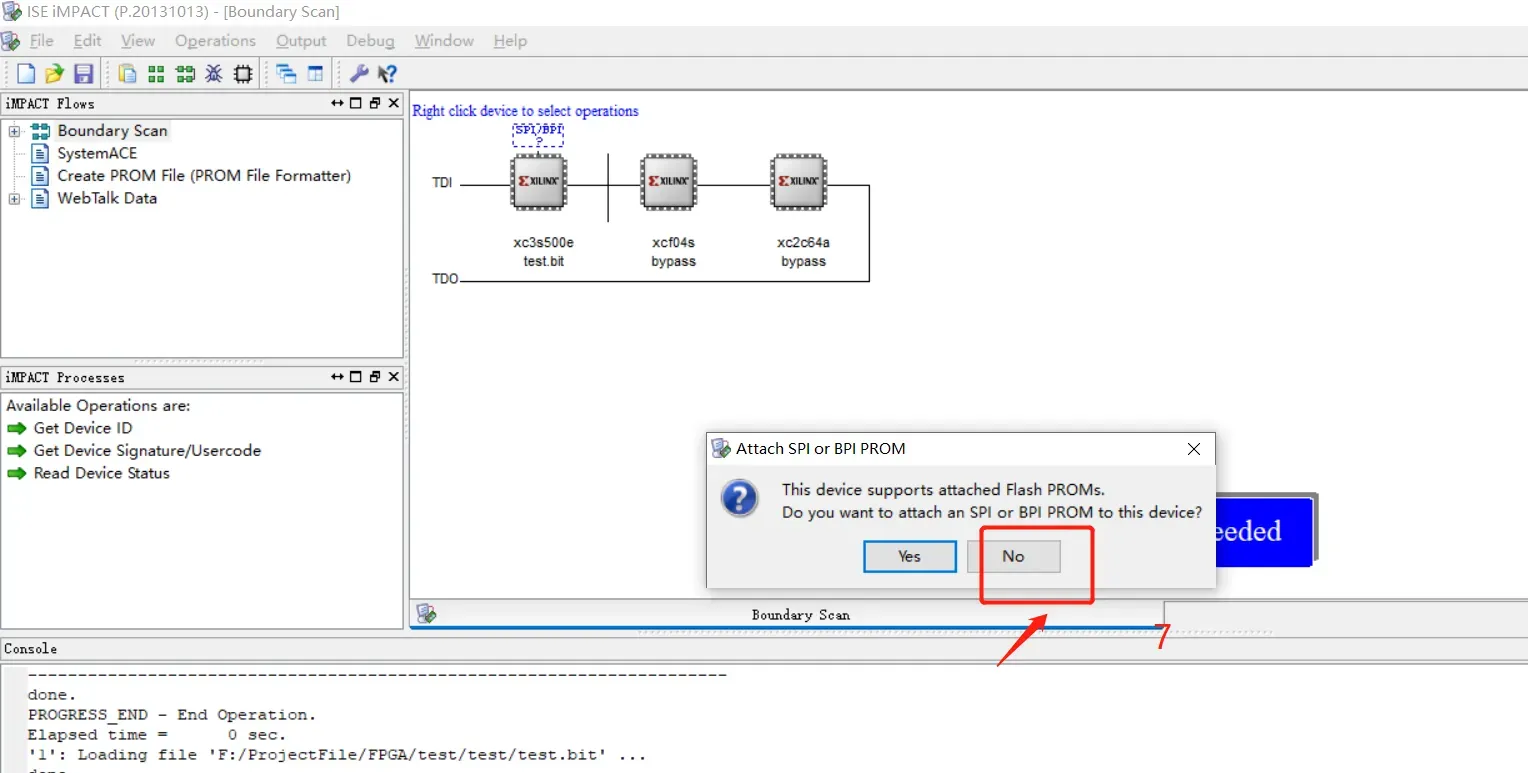

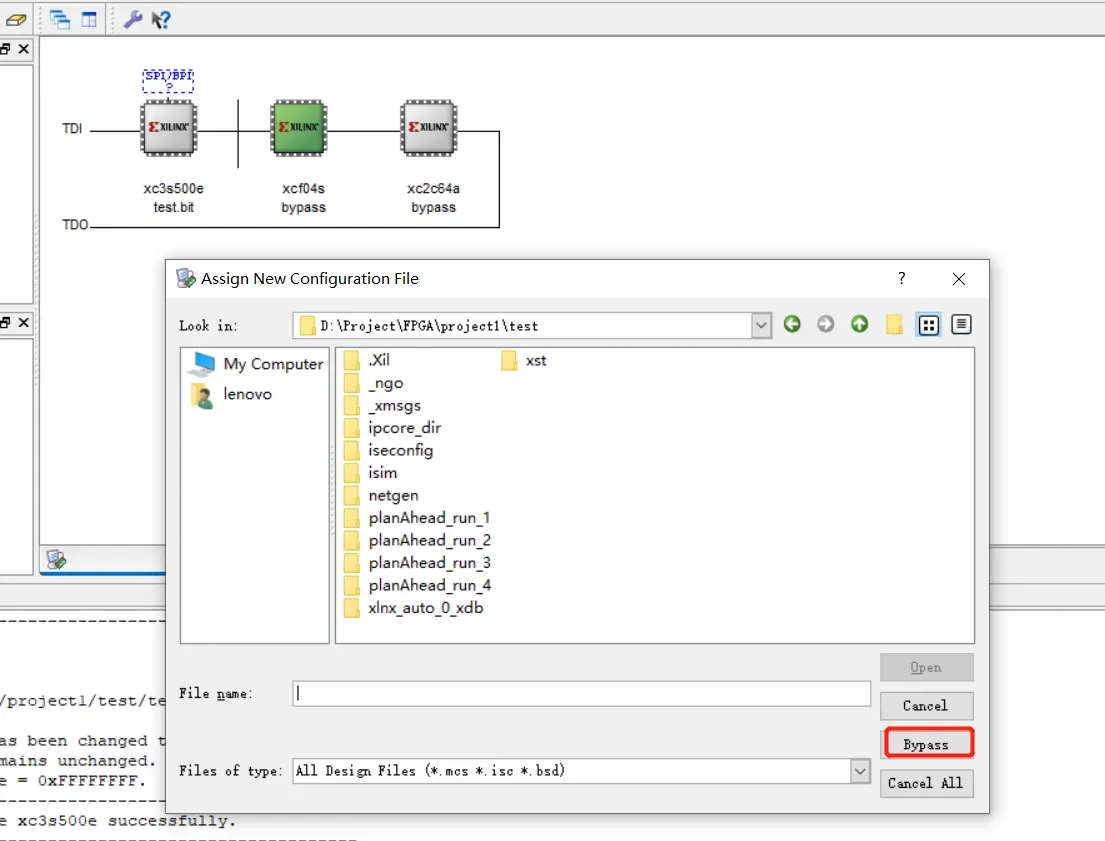

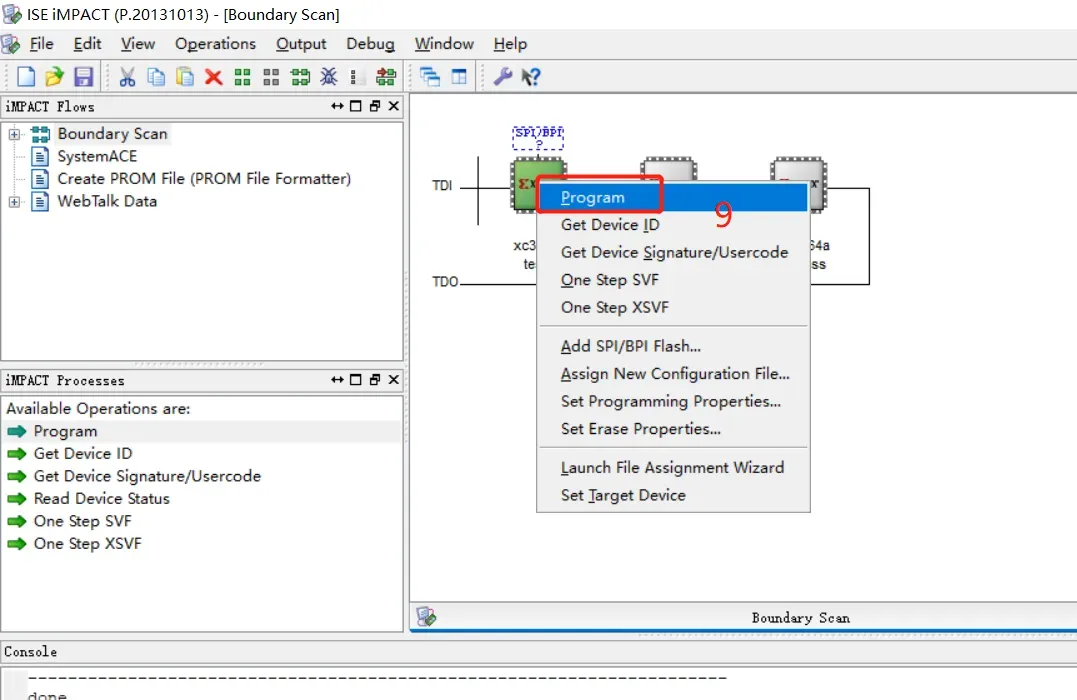

软件会自动检测到板子上的芯片,由于我的板子上有三个芯片,所以检测到三个。在这里,我们只需要将bit加载到FPGA(第一个xc3s500e)。

剩下的两个,都选择bypass.

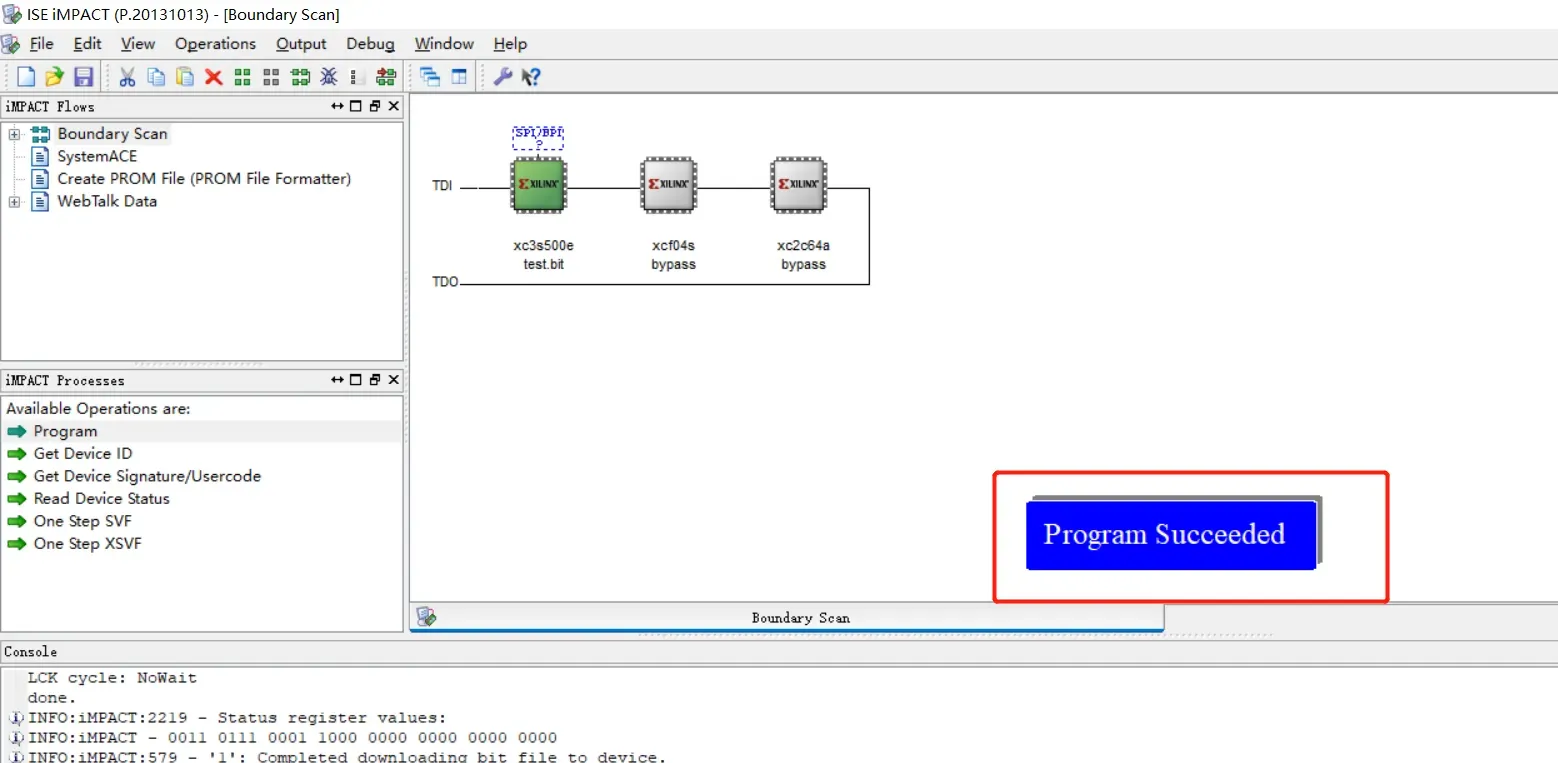

出现Program suceeded,就成功将bit流文件下载到FPGA内了。

可以在板子上看到流水灯的效果。

fpga流水灯演示

四、程序固化

- 在编写FPGA程序时,我们可以在测试程序的功能的时候去带电烧写程序,但是当程序功能满足我们的设计需求的时候,就想要把程序存放在外部的Flash中,这样即便掉电了以后,等到下次重新上电,FPGA就可以直接从Flash中把代码加载到内部运行,达到方便简单的效果。

- 由于bit不能直接下载到QSPI Flash中,所以必须先把bit文件转化为.mcs文件,然后才能下载到QSPI Flash中。

参考方法:ISE14.7程序固化步骤

五、坑

1、ise14.7在win10下闪退解决办法

- 寻找安装Xilinx_ISE的安装目录下的文件夹:D:\Xilinx\14.7\ISE_DS\ISE\lib\nt64

- 对文件夹下的两个文件作如下操作:

将libPortability.dll重名为libPortability.dll.orig

将 libPortabilityNOSH.dll 复制一份,然后将这个复制重命名为libPortability.dll - 寻找安装Xilinx_ISE的安装目录下的文件夹:D:\Xilinx\14.7\ISE_DS\common\lib\nt64

- 在该文件夹下进行如下操作:将libPortability.dll重名为libPortability.dll.orig 。然后将已经复制好的libPortabilityNOSH.dll文件复制到该文件夹下,并重命名为libPortability.dll

2、下载bit流时,电脑和FPGA连接,但是电脑识别不到FPGA

- 正常情况:打开设备管理器,出现下图:

- 有问题的情况:出现黄色感叹号

- 解决办法一:

右键点击更新驱动程序即可,找到安装位置D:\Xilinx\14.7\ISE_DS\ISE\bin\nt64\install_drivers下的这个文件进行更新即可,如果是32位则是nt。 - 解决办法二:

禁用驱动程序强制签名。

六、完整工程

文章出处登录后可见!