目录

这里以组合逻辑“与”门为例来说明在vivado中编写仿真文件(testbench)的流程及注意事项。

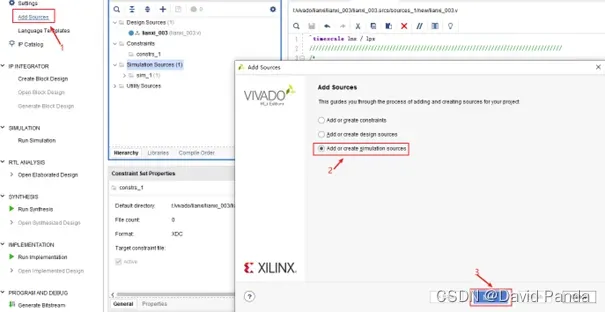

①点击“Add Sources”,在弹出的对话框中勾选“Add or create simulation sources”,点击“Next”继续。

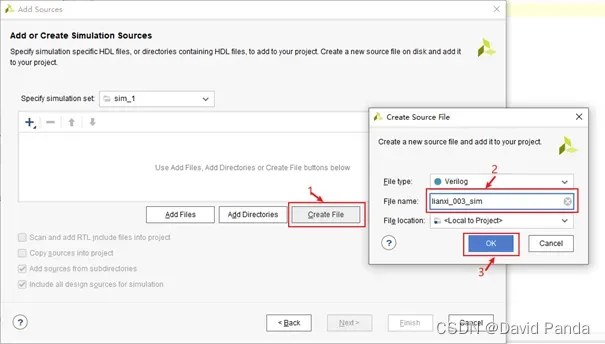

②点击“Create File”,在弹出的对话框中给仿真源文件命名(命名规则与设计源文件一致),点击“OK”继续。

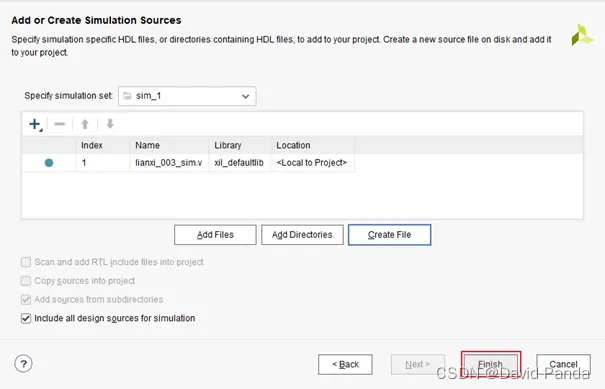

③点击“finish”

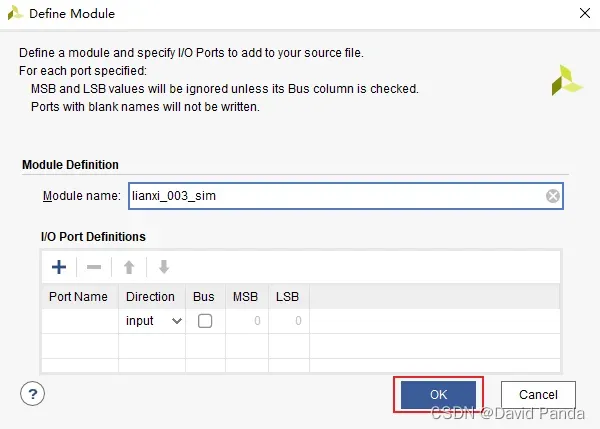

④点击“OK”

⑤点击“Yes”

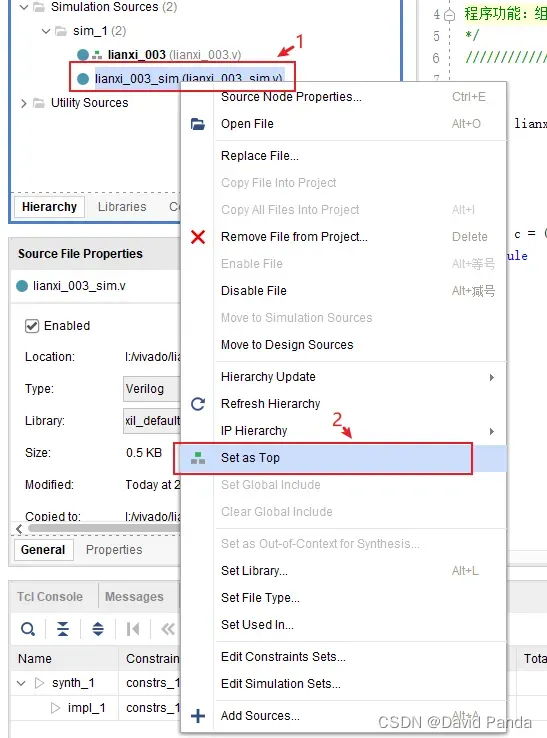

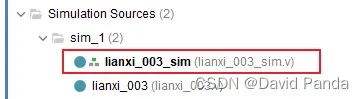

⑥将新建的仿真文件“lianxi_003_sim”设置成顶层。

⑦在新建的“lianxi_003_sim”中根据“与”门的功能要求编写测试源代码

表1 “与”门的真值表

| 输入 | 输出 | |

| a | b | c |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

“与”门的设计源文件:

`timescale 1ns / 1ps

//

/*

程序功能:组合逻辑“与”门

*/

//

module lianxi_003(

input a ,

input b ,

output c

);

assign c = (a & b);

endmodule

具体测试文件的编写规则、含义在“lianxi_003_sim”的注释中已经说明。

///

/*

程序功能:给设计源文件及功能编写仿真文件,验证设计是否满足要求。

*/

///

//1、设置仿真时间单位

//格式“`timescale 1ns / 1ps”,其中时间单位“1ps”

`timescale 1ns / 1ps

module lianxi_003_sim();

//2、定义信号类似

//与设计源文件对应,对应规则:一般输入信号定义为reg,输出信号定义为wire

reg a;

reg b;

wire c;

//3、例化设计源文件

//注意第一个名字为设计源文件名,第二个满足源文件命名规则即可,这里为了方便起,和设计源文件同名。

lianxi_003 lianxi_003 (

.a(a),

.b(b),

.c(c)

);

//4、添加激励(测试条件)

initial

begin

a = 0;

b = 0;

#500;

a = 0;

b = 1;

#500;

a = 1;

b = 0;

#500;

a = 1;

b = 1;

#500;

end

endmodule

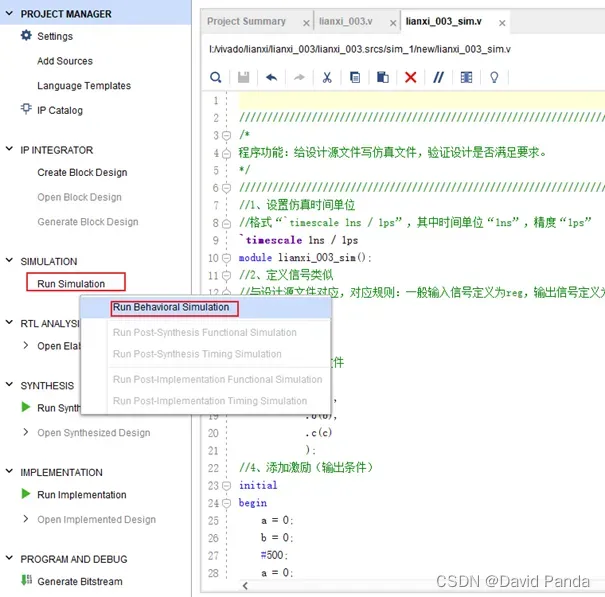

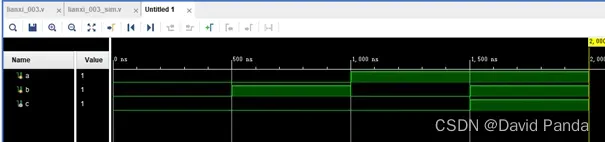

⑧project manager→run simulation→run behavioral simulation

⑨仿真结果

同“与”门的真值表对比,验证了所设计的“与”门的正确性。

参考资料:

使用VIVADO编写简单的Verilog程序和Testbench_xidian_hxc的博客-CSDN博客

文章出处登录后可见!

已经登录?立即刷新