简介

用verilog实现彩色图像的灰度化算法,并进行Modelsim仿真

RGB转GRAY公式:

GRAY= 0.299R + 0.587G + 0.114B

由于FPGA不方便小数运算,所以放大256倍进行运算,然后右移8位:

GRAY= (77R + 150G + 29B) >> 8

模块说明

module rgb2gray(

input clk,

input rst_n,

// input data & valid

input iValid,

input [7:0] red,

input [7:0] green,

input [7:0] blue,

// output data & valid

output oValid,

output [7:0] gray

);

为了简单起见,输入输出都是valid+data的形式

第一级流水线:乘法

// 第一级乘法寄存器

reg [15:0] red_r;

reg [15:0] green_r;

reg [15:0] blue_r;

always @(posedge clk, negedge rst_n) begin

if(!rst_n) begin

red_r <= 0;

green_r <= 0;

blue_r <= 0;

end else begin

red_r <= red * 8'd77;

green_r <= green * 8'd150;

blue_r <= blue * 8'd29;

end

end

第二级流水线:加法

// 第二级加法寄存器

reg [15:0] gray_r1;

always @(posedge clk, negedge rst_n) begin

if(!rst_n)

gray_r1 <= 0;

else

gray_r1 <= red_r + green_r + blue_r;

end

第三级流水线:移位

// 第三级移位寄存器

reg [7:0] gray_r2;

always @(posedge clk, negedge rst_n) begin

if(!rst_n)

gray_r2 <= 0;

else

gray_r2 <= gray_r1[15:8];

end

valid延迟输出

因为流水线消耗了3个时钟周期,所以输出valid相较于输入valid要延迟3拍

// valid打三拍

reg [2:0] valid_shift;

always @(posedge clk, negedge rst_n) begin

if(!rst_n)

valid_shift <= 0;

else

valid_shift <= {valid_shift[1:0], iValid};

end

assign oValid = valid_shift[2];

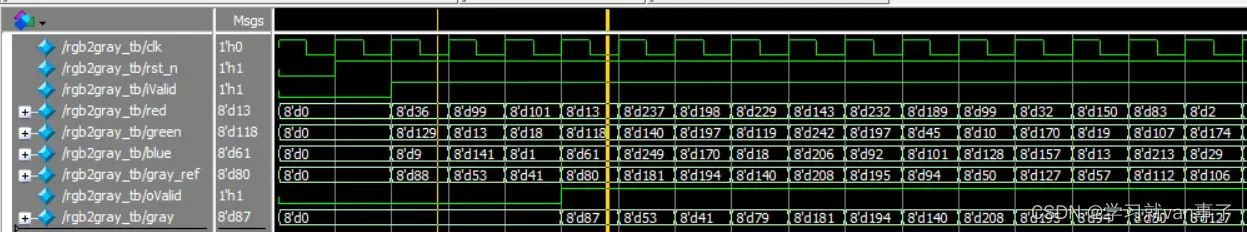

Modelsim仿真

写个testbench模拟50个像素输入:

`timescale 1ns/1ns

module rgb2gray_tb;

reg clk = 1'b1;

always #10 clk = ~clk;

reg rst_n = 1'b0;

reg iValid = 1'b0;

reg [7:0] red = 8'd0;

reg [7:0] green = 8'd0;

reg [7:0] blue = 8'd0;

// 用于对比

wire [7:0] gray_ref = red * 0.299 + green * 0.587 + blue * 0.114;

wire oValid;

wire [7:0] gray;

initial begin

#20 rst_n <= 1'b1;

// 仿真50个像素

repeat(50) begin

#20;

iValid <= 1'b1;

red <= $random;

green <= $random;

blue <= $random;

end

#100 $stop;

end

rgb2gray inst_rgb2gray(

.clk (clk),

.rst_n (rst_n),

.iValid (iValid),

.red (red),

.green (green),

.blue (blue),

.oValid (oValid),

.gray (gray)

);

endmodule

波形图如下:

文章出处登录后可见!

已经登录?立即刷新