一、编写设计程序

1、新建工程:

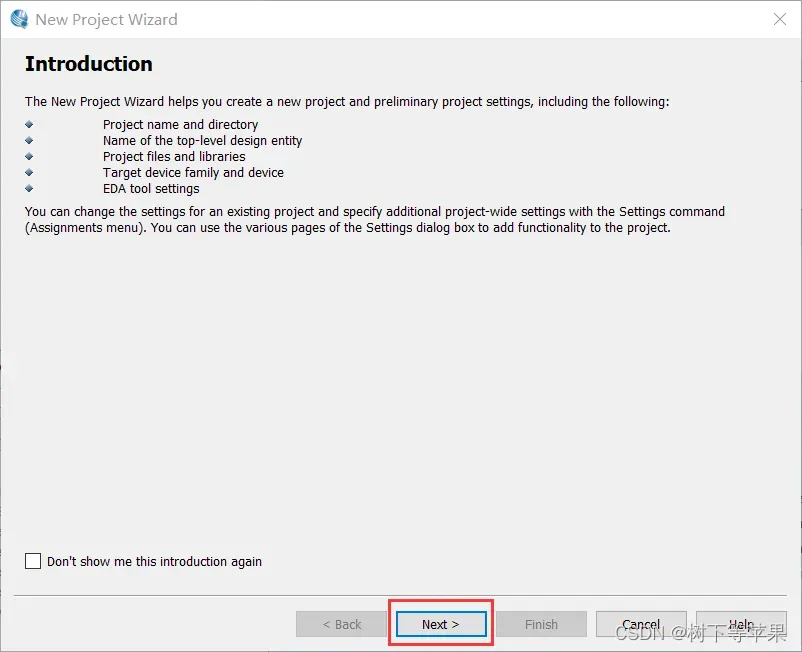

打开quartus软件,菜单栏:File->New Project Wizard,然后得到下图界面:点击next。

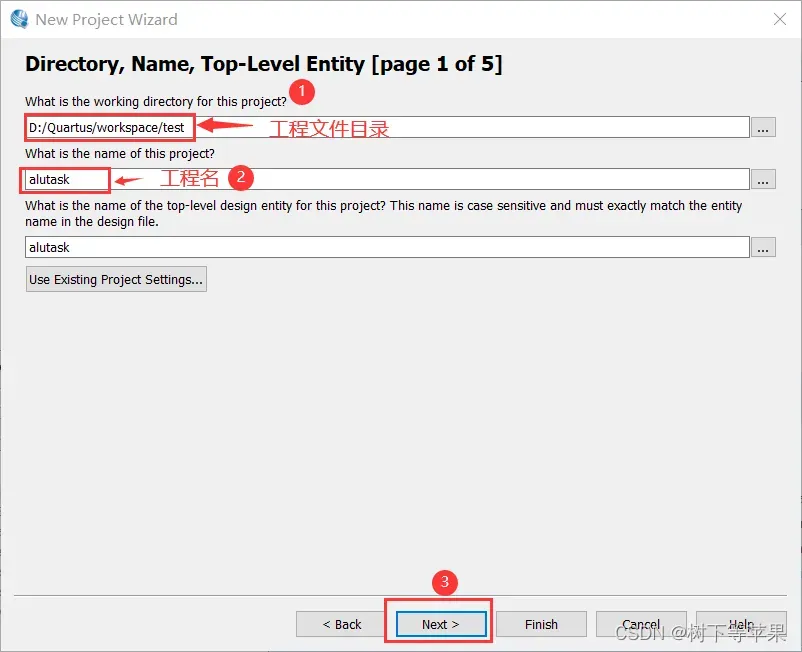

在该界面中需设置工程目录以及工程名。

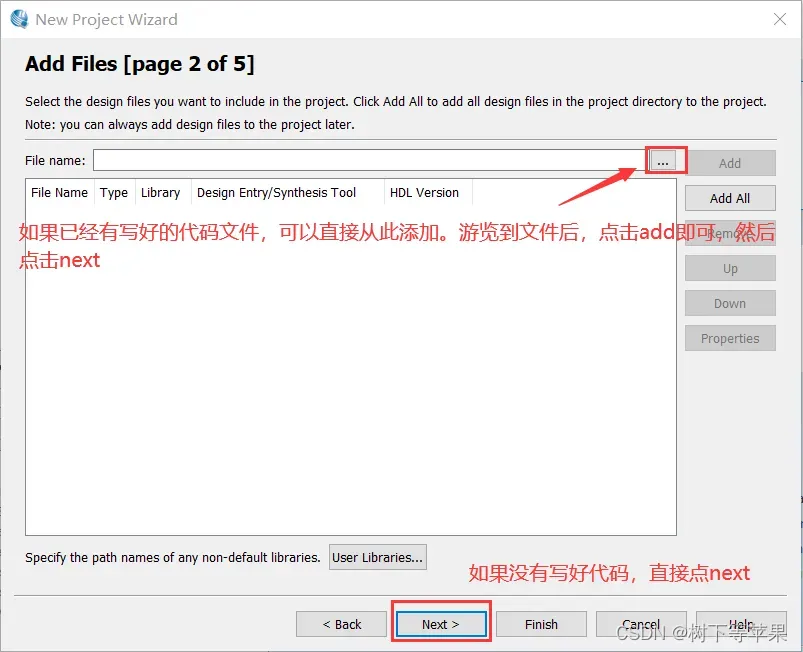

本项目没有写好的代码,直接点击next进入下一步。

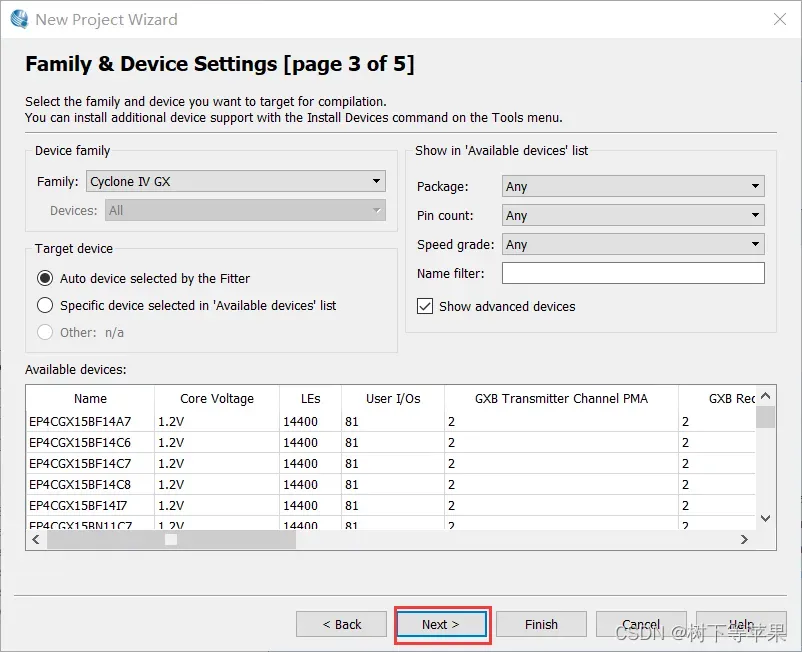

在以下界面选择相应的设备,这需要根据你手上设备的型号选择。本项目不需要再实物开发板上验证,所以不进行选择或者随意选择一款均可。

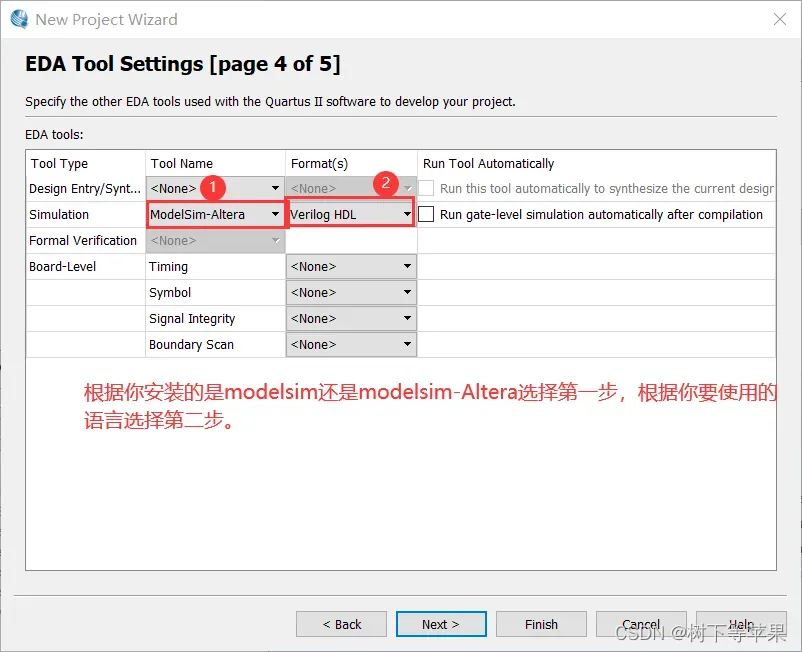

接下来是EDA工具选择,选择好后点击next。

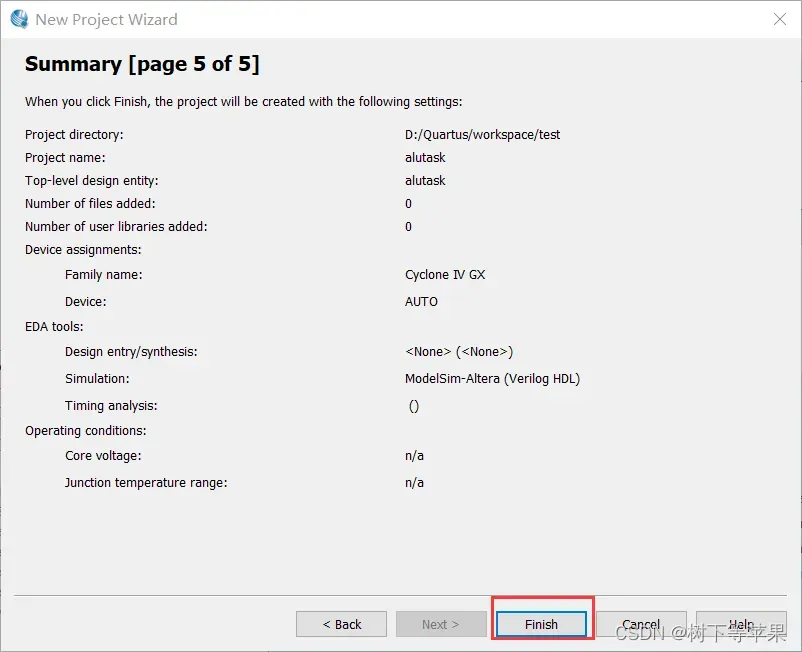

最后一步是之前的一个总结报告,直接finish就好。至此,成功新建一个项目。

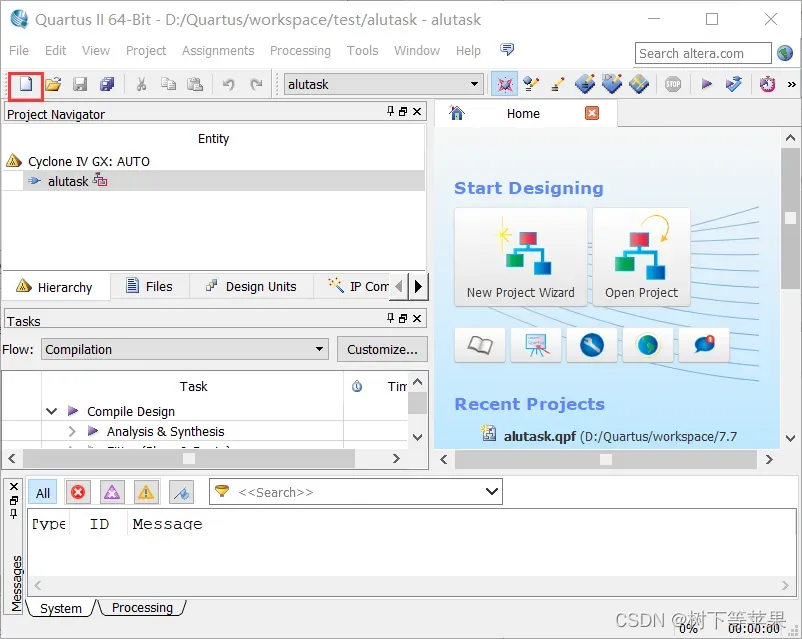

2、编写程序

(1)点击红框,新建程序源文件。

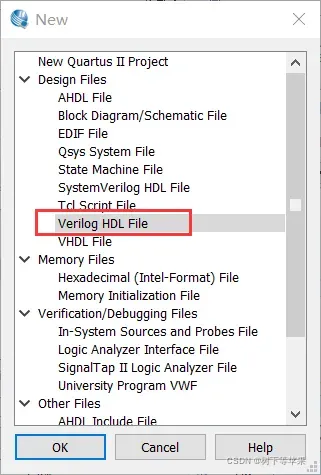

(2)选择文件类型,因为使用Verilog写,所以选择以下文件类型。选择好后点击OK。

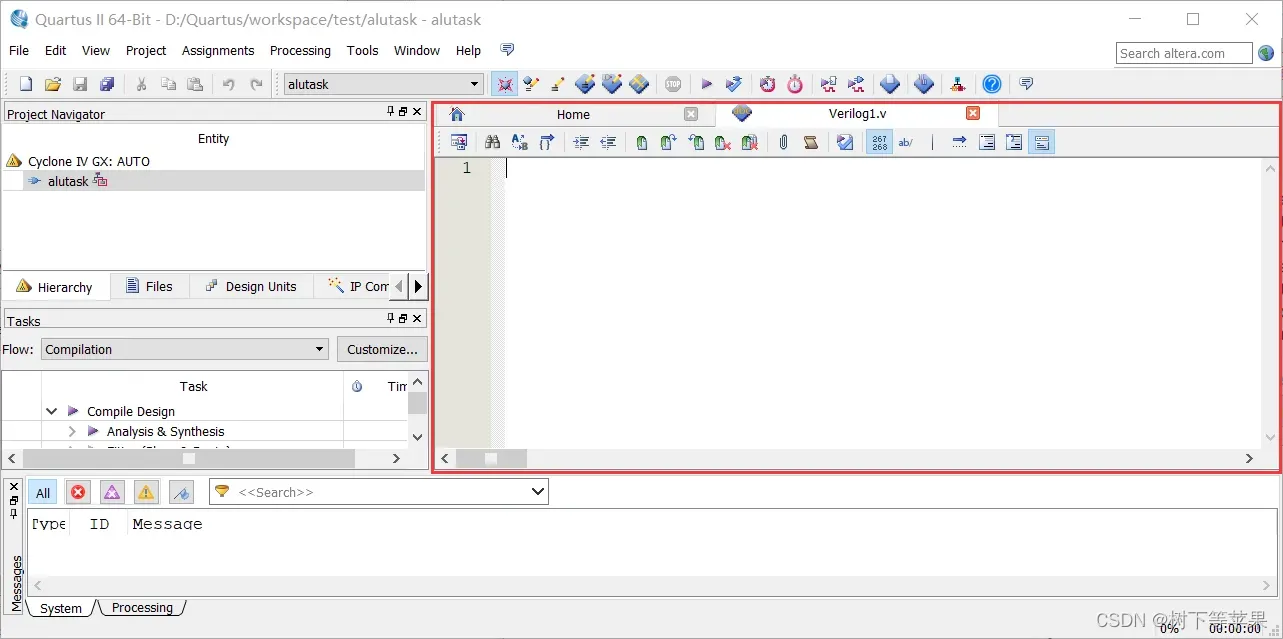

(3)完成以上步骤,在左侧会弹出一个新的文件编写界面。如下,文件名为Verilog1.v。

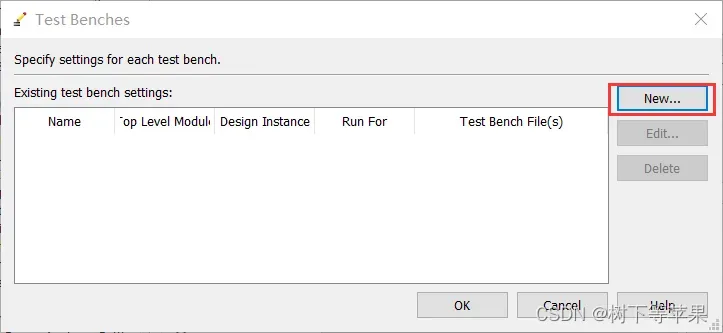

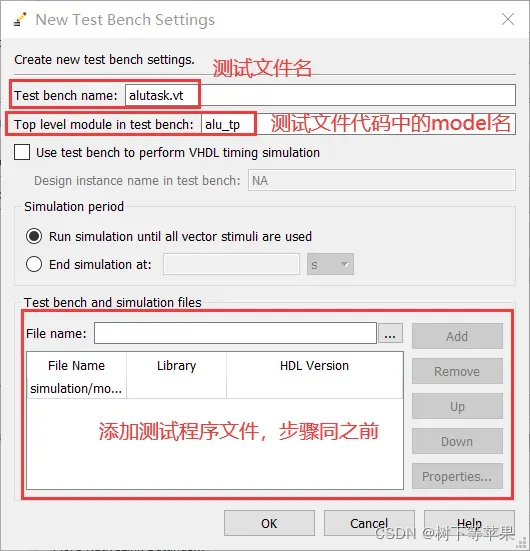

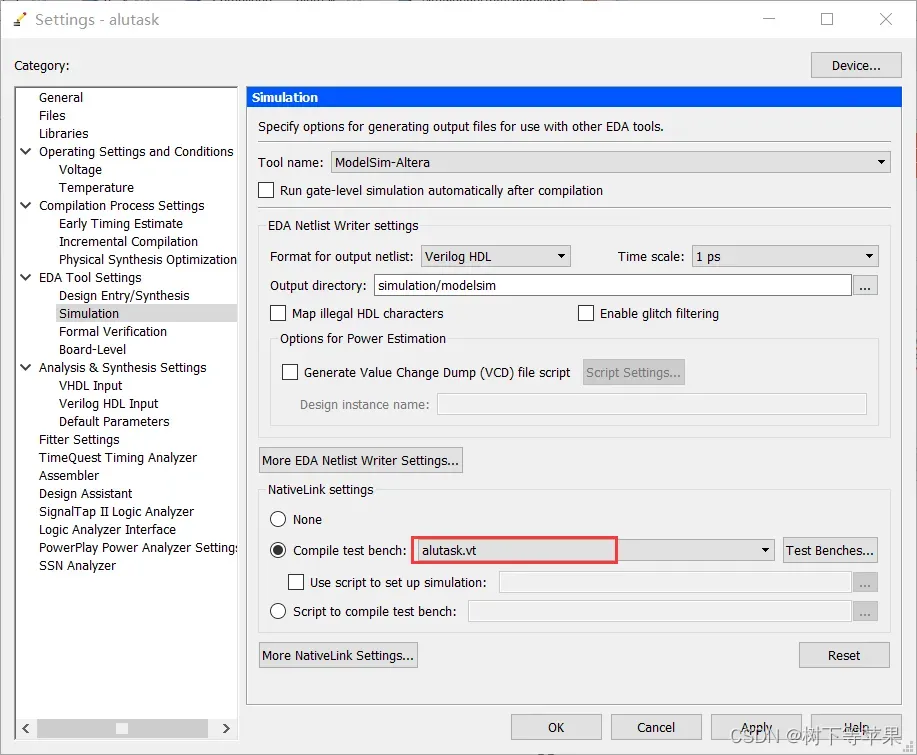

(2)添加测试程序

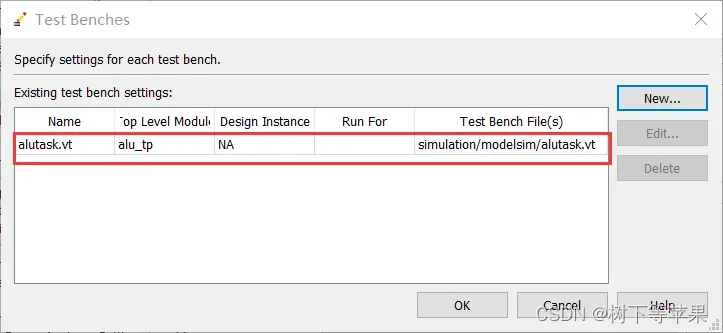

可以看到已成功添加该文件。

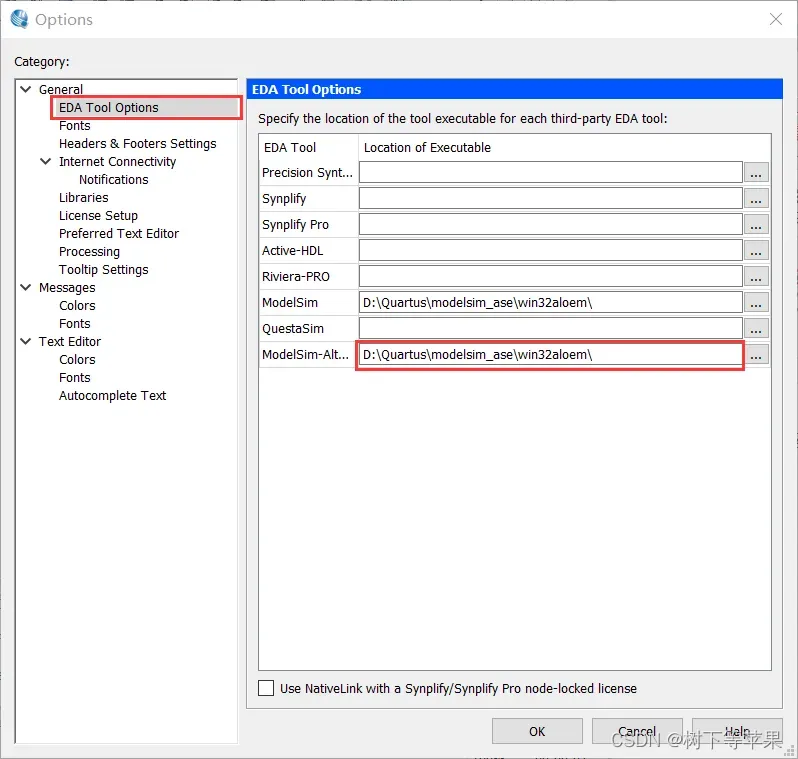

(3)查看modelsim软件安装路径

菜单栏:tools->options。

如果路径为空白的话,手动游览到modelsim安装的路径下。

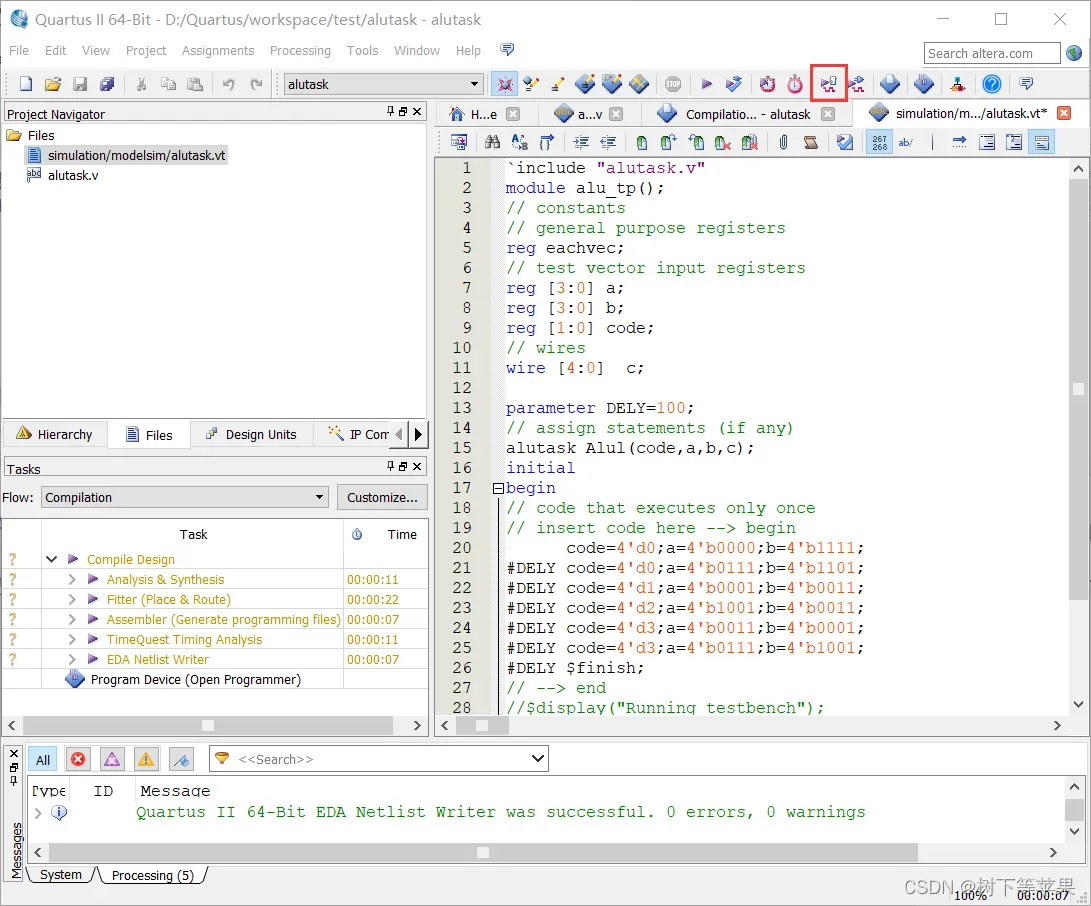

四、modelsim仿真

1、调用modelsim软件:点击图中标志或者tools->run simulation tools->RTL simulation

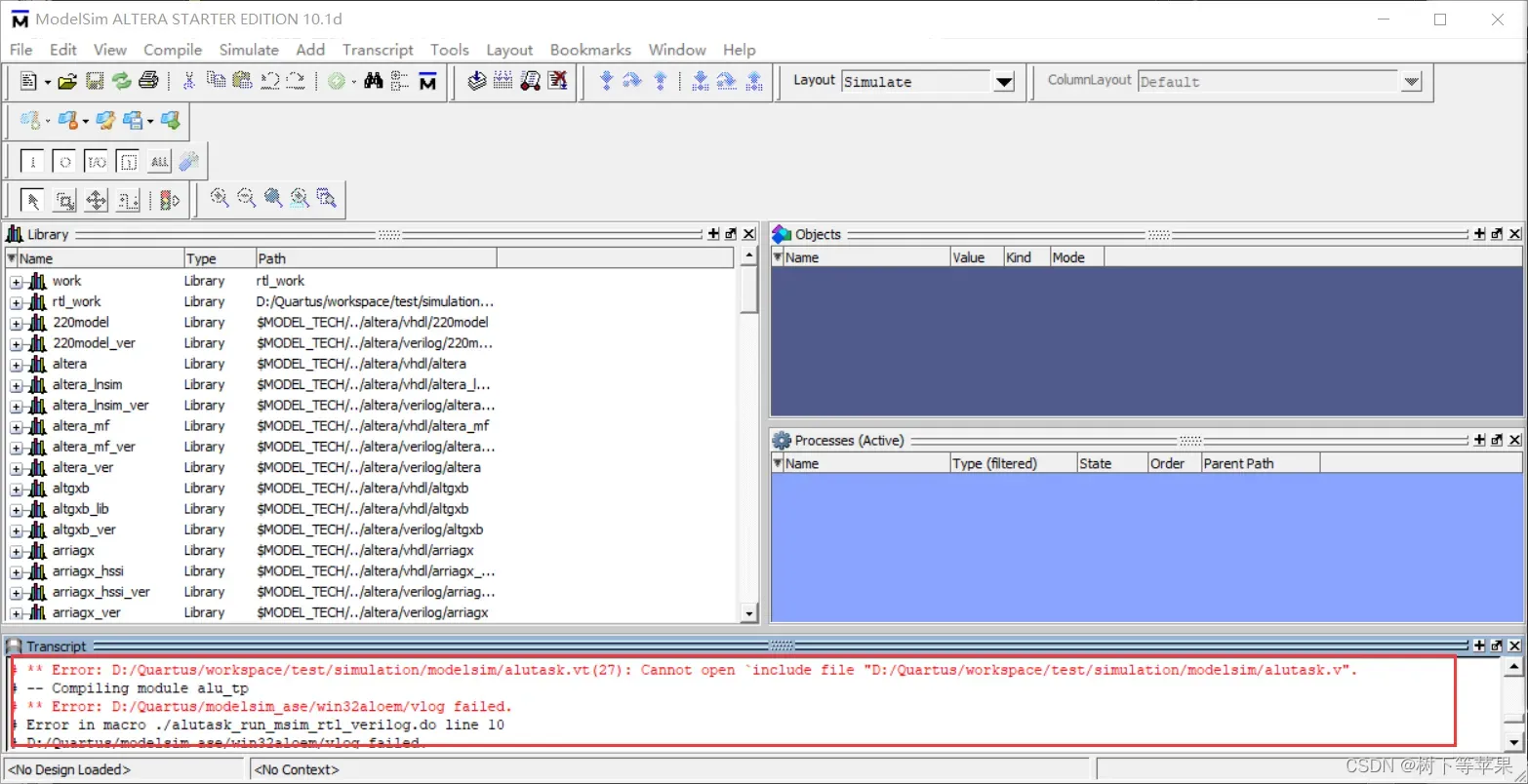

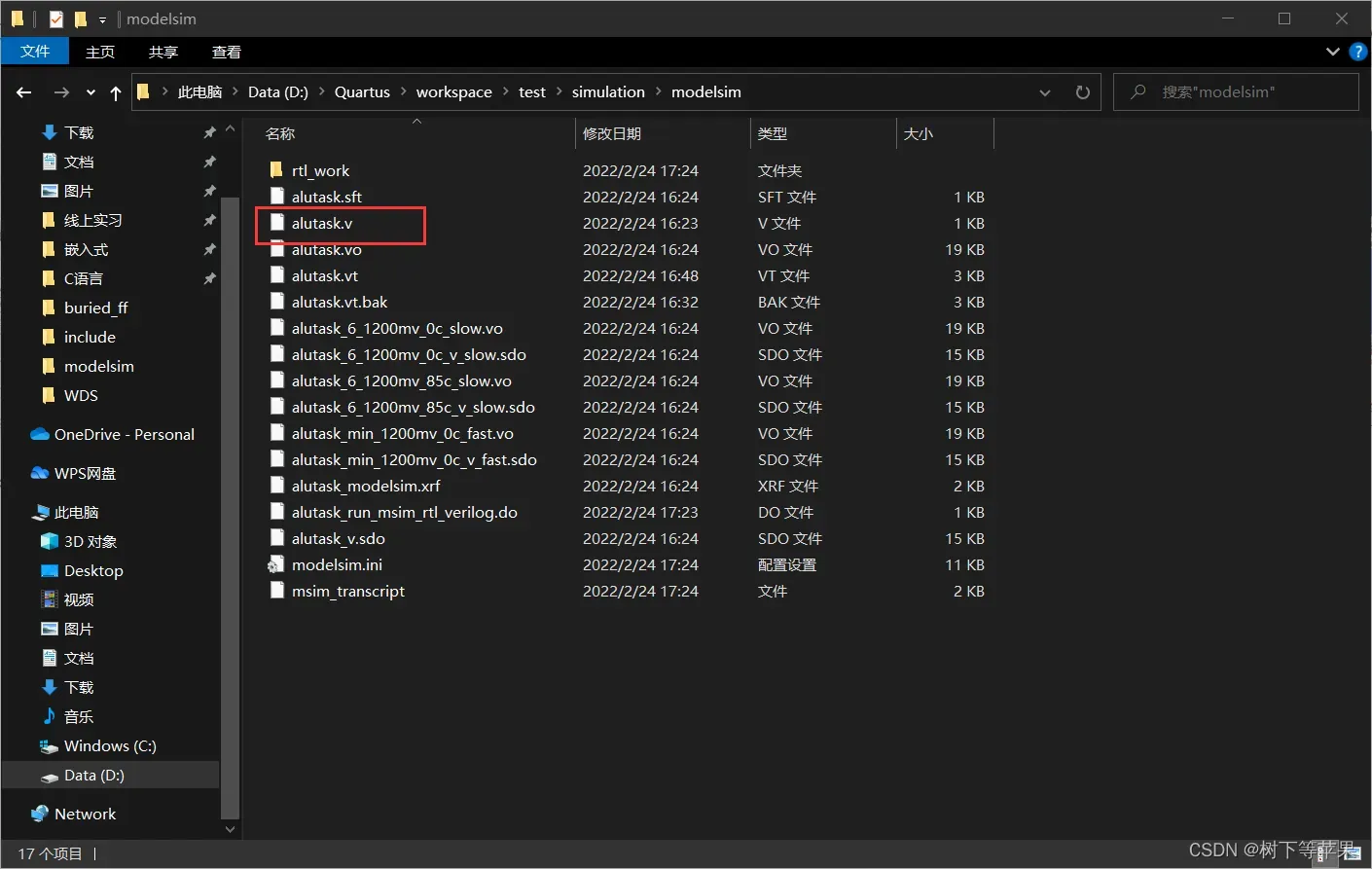

2、出错:可以看出错误是在modelsim目录下(即测试程序文件所在目录)找不到xxx.v文件。

3、将xxx.v文件复制到测试程序文件所在目录

4、重新进行RTL simulation(需关闭modelsim)

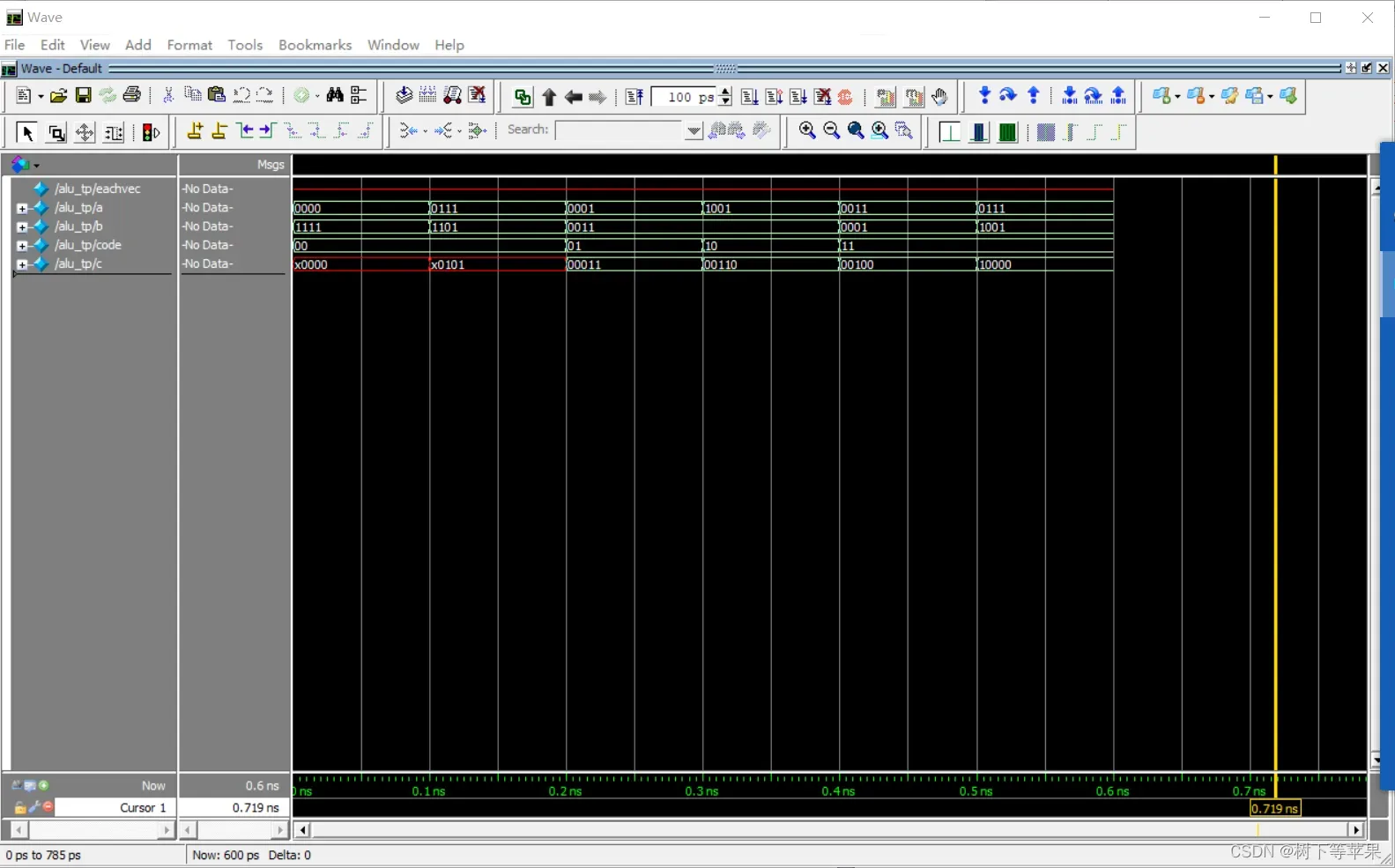

接下来只需等待便可,最后查看得出的wave图是否符合设计要求就完成了这个仿真。

文章出处登录后可见!

已经登录?立即刷新