文章目录

一、FPGA

简介

FPGA是Field Progammable Gate Array的简称,也就是现场可编程门阵列。它是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,其内部的大部分电路功能都可以根据需求进行更改,即解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

与传统模式的芯片设计相比,FPGA的涉笔并非单纯局限于研究以及设计芯片,而是针对较多领域产品都能借助特定芯片模型予优化设计。常见FPGA的应用领域有算法加速、视频图像处理、通信领域、医疗领域以及安防领域等。自Xilinx在1984年创造出FPGA以来,这种可编程逻辑器件凭借性能、上市时间、成本、稳定性和长期维护方面优势明显,在通信、医疗和安防等领域占有一席之地。

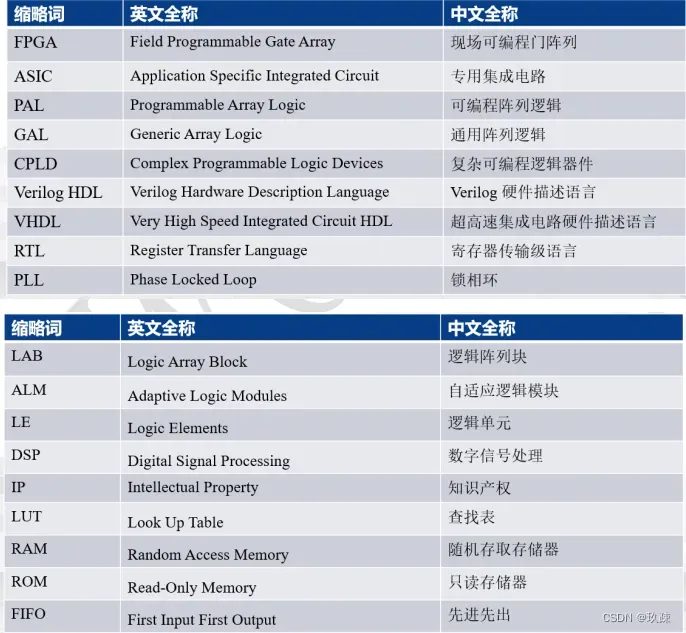

相关名词解释

说明:

PLL:可用于稳定时钟,时钟分频、倍频

IP:相当于第三方库文件

软IP核:由自己设计编写

硬IP核:集成好的IP核

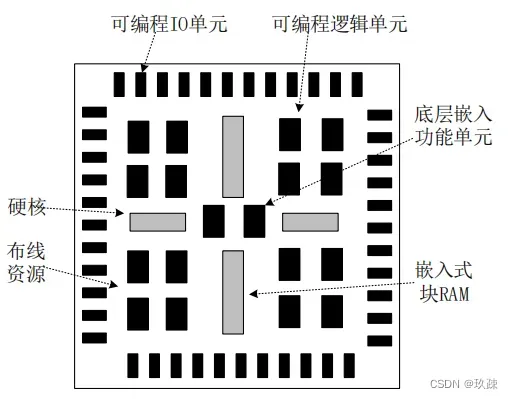

FPGA基本构造

简化的FPGA基本结构由6部分组成,分别是可编程输入/输出单元、基本可编程逻辑单元、嵌入式块RAM、丰富的布线资源、底层嵌入功能单元和内嵌专用硬核。

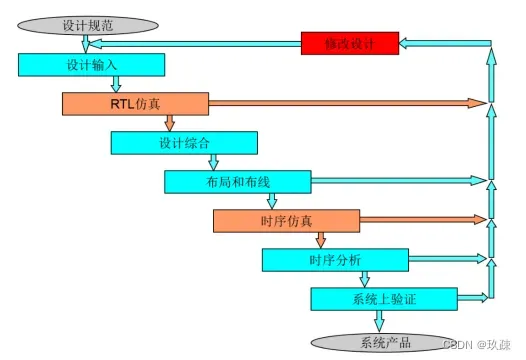

FPGA开发流程

一般来说,FPGA的设计开发流程包括设计输入、RTL功能仿真、分析综合、布局布线、时序仿真、时序分析和上板验证等几个步骤。

说明:

① 设计输入:通过某些规范的描述方式,将设计者构思输入给EDA工具;

② RTL仿真:功能仿真,运营专门的仿真工具,验证设计的逻辑功能是否正确;

③ 设计综合:运用对应的EDA工具,将设计转化成逻辑门级别电路;

④ 布局布线:在指定器件上将设计的逻辑电路实现;

⑤ 时序仿真:将布局布线的时延信息反标注到设计网表中所进行的仿真,也叫后仿真;

⑥ 时序分析:为了保证设计的可靠性,在时序仿真后还要做一下验证;

⑦ 上板验证:将生成的配置文件写入芯片进行测试;

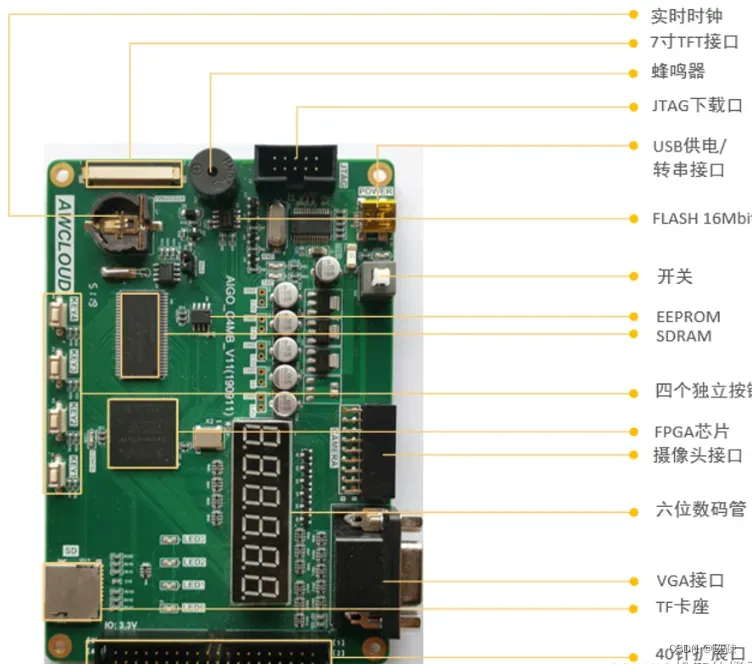

硬件资源介绍

我这里使用的是CycloneIV系列的EP4CE6F17C8这款FPGA开发板,如图所示:

二、开发工具介绍

说明:开发工具对于初学者来说选择一款就可以了,比如你用的哪家的开发板就可以选择相应的开发工具,有些EDA综合工具也自带代码编辑器和仿真器,如果够用就没必要装第三方仿真工具了。比如用Xilinx的开发板,就可以选择Vivado软件,这款软件自带代码编辑器和仿真工具。

VScode

官网下载地址:https://code.visualstudio.com

Visual Studio Code(简称VS Code)是Microsoft在2015年4月30日Build开发者大会上正式宣布一个运行于Mac OSX 、Windows和Linux之上的,针对与编写现代Web和云应用的跨平台源代码编辑器。它具有对JavaScript,TypeScript和Node.js的内置支持,并具有丰富的其他语言(例如C++,C#,Java,Python,Verilog)和运行时扩展的生态系统。

Quartus II

Quartus II 是Altera公司推出的综合性CPLD/FPGA开发软件,软件支持原理图、VHDL、VerilogHDL等多种设计输入形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程。

Quartus II 提供了完全集成且与电路结构无关的开发包环境,具有数字逻辑设计的全部特性,包括:可利用原理图、结构框图、VerilogHDL、AHDL和VHDL完成电路描述,并将其保存为实体文件;此外,Quartus II 还可以与VScode、Modelsim关联使用,给开发人员提供了软件使用的便利性。

Altera Quartus II 作为一种可编程逻辑的设计环境,由于其强大的设计能力与只管易用的接口,越来越受到数字系统设计者的欢迎。

Vivado

官网下载地址:https://china.xilinx.com/support/university/vivado.html

Vivado是由Xilinx公司在2012年发布的集成设计环境。其包括高度集成的设计环境和新一代从系统到IC级的工具,这些均建立在共享的可扩展书记模型和通用调试环境的基础上。

ModelSim

Mentor公司的ModelSim是业界最优秀的HDL语言仿真软件,它能提供友好的仿真环境,是业界唯一的单内核支持VHDL和Verilog混合仿真的仿真器。它采用直接优化的编译技术、Tcl/Tk技术和单一内核仿真技术,编译仿真速度快,编译的代码与平台无关,便于保护IP核,个性化的图形界面和用户接口,为用户加快调错提供强有力的手段,是FPGA/ASIC设计的首选仿真软件。

Visio

Microsoft Office Visio是一款绘制流程图和示意图的软件,是一款便于IT和商务人员就复杂信息、系统和流程进行可视化处理、分析和交流的软件。

总结

这篇文章仅仅是对FPGA开发一些基本的基础只是以及开发工具的介绍,如果想要进入FPGA行业深造,还得系统性地进行学习、实践。

对于工具的选择因人而异,反正我目前这几个工具都在使用,有一些没有贴下载地址工具需要自己找找,反正一搜一大把,跟着装就是了!!!

文章出处登录后可见!