1.ILA抓取不到波形或波形无变化的问题

1.1 dbg_hub时钟 ila时钟 jatg时钟 三者关系及要求

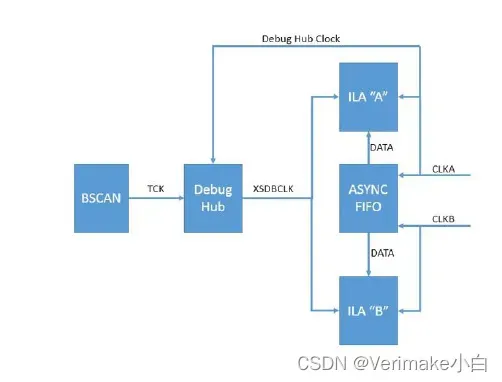

(1)两个ILA时钟CLKA和CLKB分别为跨时钟域的两个快慢时钟,通过(Mark Debug+Set Up Debug)方式添加的信号会自动连接到相应的时钟信号.

(2)DeBug Hub时钟为ILA时钟和JTAG时钟的中间连接部分, dbg_hub >= ila时钟 > jatg时钟,三者时钟关系需要满足要求。

(3)DeBug Hub时钟在通过(Mark Debug+Set Up Debug)方式添加待测信号时会自动选择某一个ILA时钟或者单纯就是一个clk(不知道是什么时钟),这一步最容易出问题,问题就是最后布线完成上板测试时显示(NO DeBug Hub Cores)完全看不到波形。

由于dbg_hub时钟 >= ila时钟,所以这一步在通过(Mark Debug+Set Up Debug)方式添加待测信号后保存工程,重新打开XDC约束文件,查看ILA最后四行,修改connect_debug_port dbg_hub/clk [get_nets clk_axi],使得dbg_hub时钟连接到频率最高的ILA时钟,即DeBug Hub=CLKB(高)>CLKA(次高)>CLKC(低)

set_property C_CLK_INPUT_FREQ_HZ 300000000 [get_debug_cores dbg_hub]

set_property C_ENABLE_CLK_DIVIDER false [get_debug_cores dbg_hub]

set_property C_USER_SCAN_CHAIN 1 [get_debug_cores dbg_hub]

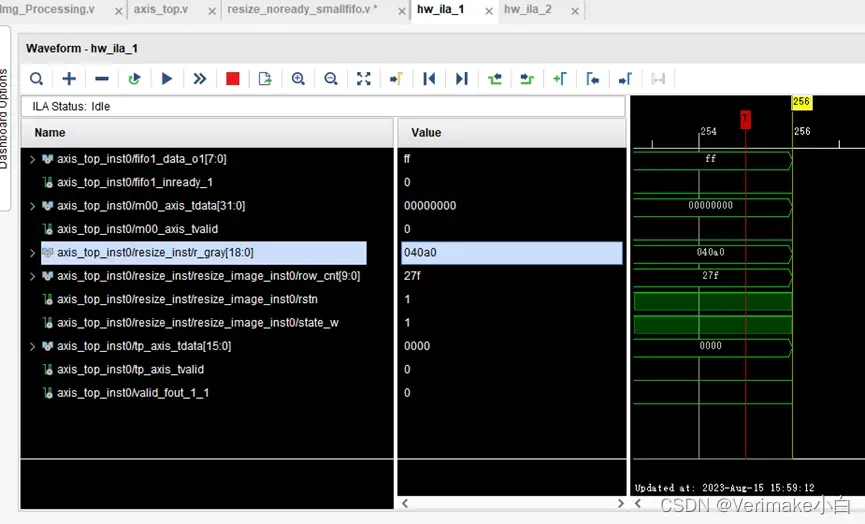

connect_debug_port dbg_hub/clk [get_nets clk_axi](4)如果看到波形,然而波形无变化,如下图所示

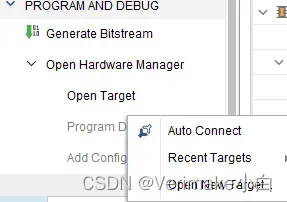

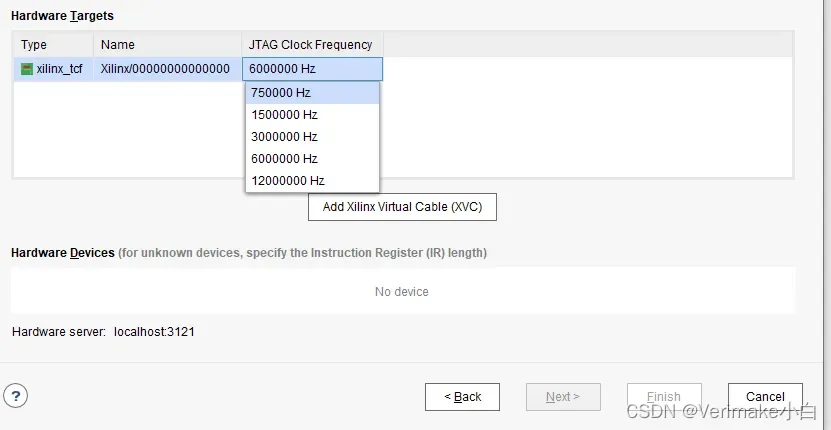

首先,看一下ILA时钟是否大于JTAG时钟频率,JTAG时钟可以在连接板子时选择(open new target),从0.75M到12M不等,取决于JTAG线。

其次,如果时钟关系没有问题,那么大概就是你的模块中某一个信号出问题了。

2.多模块ILA调试流程

如果你完成上述操作,确定是你模块中的某一个信号的问题导致ILA抓取到的波形无变化,那么接下来的ILA调试中,建议你按照数据流的路线从头开始查找问题。

时钟源->一级子模块->二级子模块->问题信号所在模块->四级模块,虽然这个过程繁琐,但是是查找问题最稳妥、最有效的方法了。

版权声明:本文为博主作者:Verimake小白原创文章,版权归属原作者,如果侵权,请联系我们删除!

原文链接:https://blog.csdn.net/weixin_60381535/article/details/132533116