文章目录

- 一、Verilog HDL 概述

-

- 1、Verilog HDL 是什么

- 2、Verilog HDL产生的背景

- 3、Verilog HDL 和 VHDL的区别

- 二、Verilog HDL 基础知识

-

- 1、Verilog HDL 语言要素

-

- 1.1、命名规则

- 1.2、注释符

- 1.3、关键字

- 1.4、数值

-

- 1.4.1、整数及其表示

- 1.4.2、实数及其表示

- 1.4.3、字符串及其表示

- 2、数据类型

-

- 2.1、线网型(wire)

- 2.2、寄存器型(reg)

- 2.3、存储器型(memory)

- 2.4、整数型(integer)

- 2.5、时间型(time)

- 2.6、实数型(real)

- 2.7、参数型

- 3、运算符

-

- 3.1、算术运算符

- 3.2、关系运算符

- 3.3、相等关系运算符

- 3.4、逻辑运算符

- 3.5、按位运算符

- 3.6、归约运算符

- 3.7、移位运算符

- 3.8、连接运算符

- 总结

一、Verilog HDL 概述

1、Verilog HDL 是什么

Verilog HDL(Hardware Description Language)是一种硬件描述语言,用于从算法级、门级到开关级的多种抽象设计层次的数字系统建模。 现实生活中多用于专用集成电路(Application Specific Integrated Circuit,ASIC)和现场可编程门阵列(Field Programmabl Gate Array,FPGA)的实现。

2、Verilog HDL产生的背景

第一只晶体管出现后,数字集成电路设计密度越来越大、电路越来越复杂,传统的画图或连线的设计方法已不再适用。

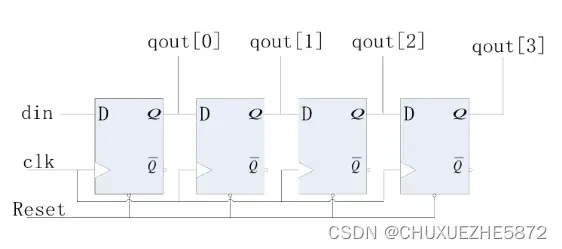

例如:设计4位移位寄存器,仅需简短几行代码完成。

module register_four(

input clk ,

input Reset ,

input din ,

output reg [3:0] qout

);

always @(posedge clk or posedge Reset)begin

if(Reset)

qout <= 4'b0;

else

qout <= {qout[2:0],din};

end

endmodule

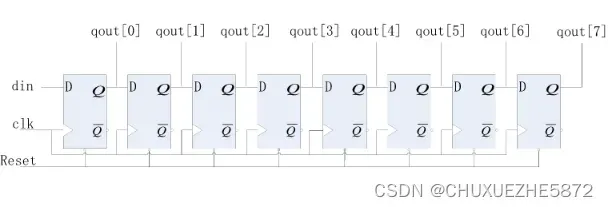

若要将4位移位寄存器改为8位移位寄存器,仅需修改少量代码。

module register_eight(

input clk ,

input Reset ,

input din ,

output reg [7:0] qout

);

always @(posedge clk or posedge Reset)begin

if(Reset)

qout <= 8'b0000_0000;

else

qout <= {qout[6:0],din};

end

endmodule

由上例可直观发现,Verilog HDL可用较少的语句描述较为复杂的电路和灵活的可扩展性,为数字集成电路设计带来了极大的便捷。

3、Verilog HDL 和 VHDL的区别

目前,Verilog HDL 和 VHDL(VHSIC Hardware Description Language,VHSIC 为 Very High Speed Integrated Circuit)是最为常用的硬件描述语音。

Verilog HDL:

语法灵活、宽松,多被思维活跃的美国人采用。因Verilog HDL 语法宽松,其不适合对系统要求层次严格的大规模设计。

VHDL:

语法结构紧凑、严谨,多被思维欧洲人采用。VHDL在大规模数字集成电路设计中具有一定优势。

注:

Verilog基于C语言发展而来,语法灵活、宽松,且国内开发人员多采用Verilog,对初学者较为友好。

二、Verilog HDL 基础知识

1、Verilog HDL 语言要素

1.1、命名规则

在Verilog HDL 中,标识符背用来命名信号、模块、参数等,它可以是任意一组字母、数字、$符号和_(下划线)符号的组合。

注:标识符中字母区分大小写,且第一个字必须是字母或下划线。

1.2、注释符

单行注释:单行注释以“//”开始,Verilog HDL忽略此处到行尾的内容。

多行注释:多行注释采用“/**/”,从“/”开始,到“/”结束,Verilog HDL忽略其中注释的内容。

注:多行注释不允许嵌套,但单行注释可以嵌套在多行注释中。

例如:

非法多行注释:

/*注释内容/*多行注释嵌套多行注释*/注释内容*/

合法多行注释:

/*注释内容//多行注释嵌套单行注释*/

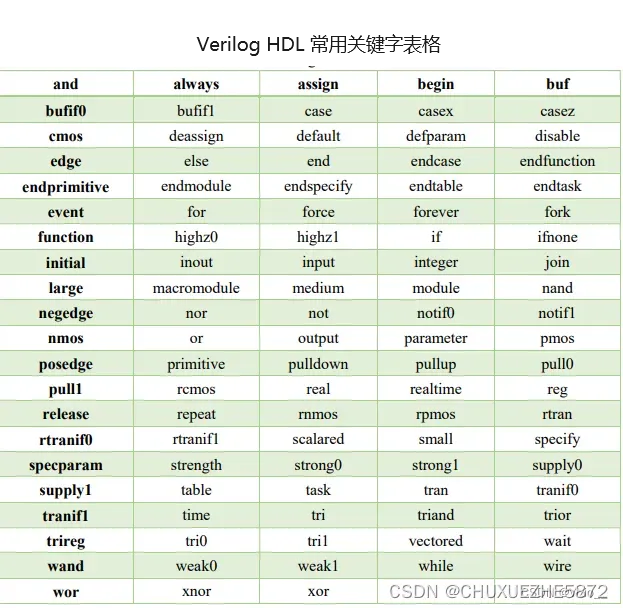

1.3、关键字

Verilog HDL 内部已经使用的词成为关键字或保留字,是事先定义好的确认符,用来组织语言结构。

注:Verilog HDL中所有的关键字都是小写的。

1.4、数值

Verilog HDL 有四种基本的电平逻辑数值状态,用数字或字符表达数字电路中传送的逻辑状态和存储信息。Verilog HDL逻辑数值中,“x”和“z”都不区分大小写,即0x1z与0X1Z等价。

在数值中,下划线符号“_”除不能放于首位外,可随意用在整数与实数中,对数值的大小无影响,仅为提高可读性。

例如:

8’b00110010 与8’b0011_0010的数值大小相等。

1.4.1、整数及其表示

整数的表示形式:

+/-<size>'<base_format><number>

(1)“+/-”:正数和负数的标识。

(2)size:换算过后二进制的宽度。

(3)“ ’ ”:为基数格式表示固有字符,该字符不能缺省,否则为非法表示形式。

(4)base_format:基数符号。

(5)number:可使用的数字字符集。

例如:

4'b0011

7'd32

8'hfd

1.4.2、实数及其表示

(1)十进制表示法。

(2)科学计数发。例如:758.4e2 的值为75840.0,3e-3的值为0.003。

1.4.3、字符串及其表示

注:字符串必须包含在同一行中,不能分行书写。

字符串在Verilog HDL中看做8位的ASCII值序列,即一个字符对应8位的ASCII值。

2、数据类型

按抽象程度 Verilog HDL数据类型可分为:物理数据类型(主要包括线网型及寄存器型)和抽象数据类型(主要包括整数型、时间型、实数型及参数型)。抽象数据类型主要用于辅助设计和验证。

2.1、线网型(wire)

wire 类型表示硬件单元之间的物理连线,由其连接的器件输出端连续驱动。如果没有驱动元件连接到 wire 型变量,缺省值一般为 “Z”。对wire 类型赋值用“assign”。

例如:

wire data_out ;

wire flag ;

assign data_out = data_in ;

assign flag = 1'b1 ;

2.2、寄存器型(reg)

reg 用来表示存储单元,它的数据会保持最后一次赋值,直到被改写。reg 默认初始值为不定值“x”,缺省是数据位宽为1位。reg 一般为无符号数,若将一个负数赋值给 reg 型变量,则制动转换其二进制补码形式。

例如:

reg data0;

reg data1;

reg [4:0] data2;

2.3、存储器型(memory)

存储器型本质上还是寄存器型变量阵列,可以描述RAM型、ROM型存储器以及reg文件。存储器中的每一个单元通过索引进行寻址。

声明格式:

reg<range1><name_of_register><range2>

(1) range1:存储器中寄存器的位宽,缺省,时为1,格式为[msb:lsb]。

(2)range2:寄存器的个数,缺省时为1,格式为[msb:lsb]。

(3)name_of_register:变量名称列表,一次可以定义多个名称,之间用逗号分开。

例如:

reg [7:0] mem1[255:0];//定义了一个有256个8位的存储器

reg [15:0] mem2[127:0],reg1,reg2;//定义了一个具有128个16位的寄存器mem2

//2个16位的寄存器reg1和reg2

mem1[2] = 0; //给mem1存储器中的第三个存储单元赋值为0

2.4、整数型(integer)

整数类型用关键字 integer 来声明。声明时不用指明位宽,位宽和编译器有关,一般为32 bit。reg 型变量为无符号数,而 integer 型变量为有符号数。

例如:

reg [31:0] data1 ;

reg [3:0] byte1 [7:0]; //数组变量,后续介绍

integer j ; //整型变量,用来辅助生成数字电路

always@* begin

for (j=0; j<=3;j=j+1) begin

byte1[j] = data1[(j+1)*8-1 : j*8]; //把data1[7:0]…data1[31:24]依次赋值给byte1[0][7:0]…byte[3][7:0]

end

end

2.5、时间型(time)

Verilog 使用特殊的时间寄存器 time 型变量,对仿真时间进行保存。其宽度一般为 64 bit,通过调用系统函数 $time 获取当前仿真时间。

例如

time current_time ;

initial begin

#100 ;

current_time = $time ; //current_time 的大小为 100

end

2.6、实数型(real)

实数用关键字 real 来声明,可用十进制或科学计数法来表示。实数声明不能带有范围,默认值为 0。如果将一个实数赋值给一个整数,则只有实数的整数部分会赋值给整数。

例如:

real data1 ;

integer temp ;

initial begin

data1 = 2e3 ;

data1 = 3.75 ;

end

initial begin

temp = data1 ; //temp 值的大小为3

end

2.7、参数型

参数用来表示常量,用关键字parameter声明,只能赋值一次,但可通过实例化的方式更改参数在模块中的值。局部参数用localparam声明,其作用和用法与parameter相同,区别在于它的值不能改变。所以当参数在本模块中调用时,可以用localparam来说明。

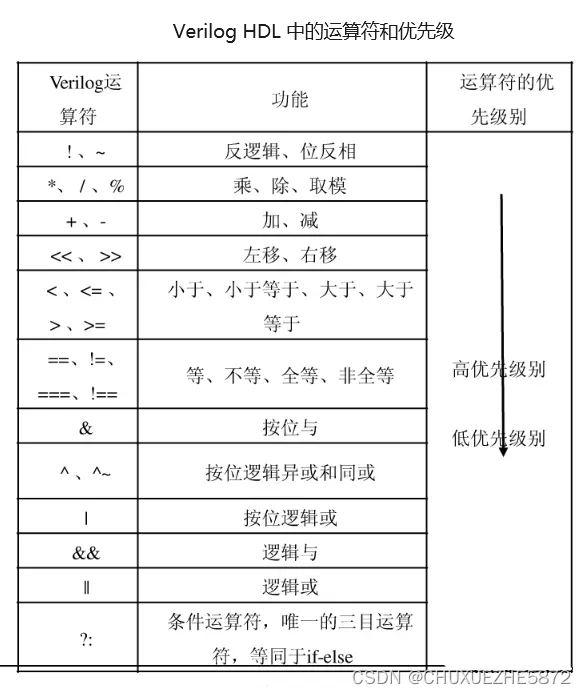

3、运算符

3.1、算术运算符

Verilog HDL中常用的算术运算符主要有五种,分别是加法(+)、减法(-)、乘法(*)、除法(/)和取模(%)。

注:

算术表达式结果的长度由最长的操作数决定。在赋值语句下,算术结果的长度由等号操作符左端的目标长度决定。

3.2、关系运算符

关系运算符也是双目运算符,是对两个操作数的大小进行比较。关系运算符有大于(>)、小于(<)、大于等于(>=)和小于等于(<=)几种。

3.3、相等关系运算符

相等关系运算符是对两个操作数进行比较,比较结果有三种,即真(1)、假(0)和不定值(x)。Verilog HDL 中有四种相等关系运算符:等于(==)、不等于(!=)、全等(===)、非全等(!==)。

3.4、逻辑运算符

逻辑运算符有三种,分别为逻辑与(&&)、逻辑或(||)、逻辑非(!)。其中逻辑与、逻辑或是双目运算符,逻辑非为单目运算符。

3.5、按位运算符

Verilog HDL 提供了五种类型位运算符:按位取反(~)、按位与(&)、按位或(|)、按位异或(^ )、按位同或(^~),按位运算符对其自变量的每一位进行操作。

3.6、归约运算符

归约操作符包括:归约与(&),归约与非(~&),归约或(|),归约或非(~|),归约异或(^),归约同或(~^)。归约操作符只有一个操作数,它对这个向量操作数逐位进行操作,最终产生一个 1bit 结果。逻辑操作符、按位操作符和归约操作符都使用相同的符号表示,因此有时候容易混淆。区分这些操作符的关键是分清操作数的数目,和计算结果的规则。

例如:

A = 4'b1010 ;

&A ; //结果为 1 & 0 & 1 & 0 = 1'b0,可用来判断变量A是否全1

~|A ; //结果为 ~(1 | 0 | 1 | 0) = 1'b0, 可用来判断变量A是否为全0

^A ; //结果为 1 ^ 0 ^ 1 ^ 0 = 1'b0

3.7、移位运算符

移位操作符包括左移(<<),右移(>>),算术左移(<<<),算术右移(>>>)。移位操作符是双目操作符,两个操作数分别表示要进行移位的向量信号(操作符左侧)与移动的位数(操作符右侧)。算术左移和逻辑左移时,右边低位会补 0。逻辑右移时,左边高位会补 0;而算术右移时,左边高位会补充符号位,以保证数据缩小后值的正确性。

A = 4'b1100 ;

B = 4'b0010 ;

A = A >> 2 ; //结果为 4'b0011

A = A << 1; //结果为 4'b1000

A = A <<< 1 ; //结果为 4'b1000

C = B + (A>>>2); //结果为 2 + (-4/4) = 1, 4'b0001

3.8、连接运算符

拼接操作符用大括号 {,} 来表示,用于将多个操作数(向量)拼接成新的操作数(向量),信号间用逗号隔开。拼接符操作数必须指定位宽,常数的话也需要指定位宽。

例如:

A = 4'b1010 ;

B = 1'b1 ;

Y1 = {B, A[3:2], A[0], 4'h3 }; //结果为Y1='b1100_0011

Y2 = {4{B}, 3'd4}; //结果为 Y2=7'b111_1100

Y3 = {32{1'b0}}; //结果为 Y3=32h0,常用作寄存器初始化时匹配位宽的赋初值

总结

该篇主要讲述Verilog HDL 常用数据类型、运算符等基础部分。受篇幅限制,此次未涉及至实际应用,后期将逐一讲解。

版权声明:本文为博主作者:CHUXUEZHE5872原创文章,版权归属原作者,如果侵权,请联系我们删除!

原文链接:https://blog.csdn.net/CHUXUEZHE5872/article/details/135882529