1 DDR3概述

DDR,名称:double data rate SDRAM,全称:双倍数据率同步动态随机存储器。允许在时钟的上升沿,下降沿传输数据,其主要作用是为了和CPU频率同步,进而大大提高数据传输效率。本工程使用的为DDR3 SDRAM,它具备更低的工作电压(1.5v),240线接口、支持8bit预读;

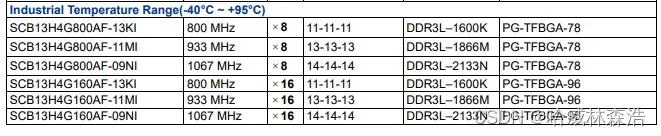

项目所使用的芯片为紫光国芯SCB13H4G160AF-11MI,该芯片容量为512GB(4Gbit),最大支持933MHz时钟输入。

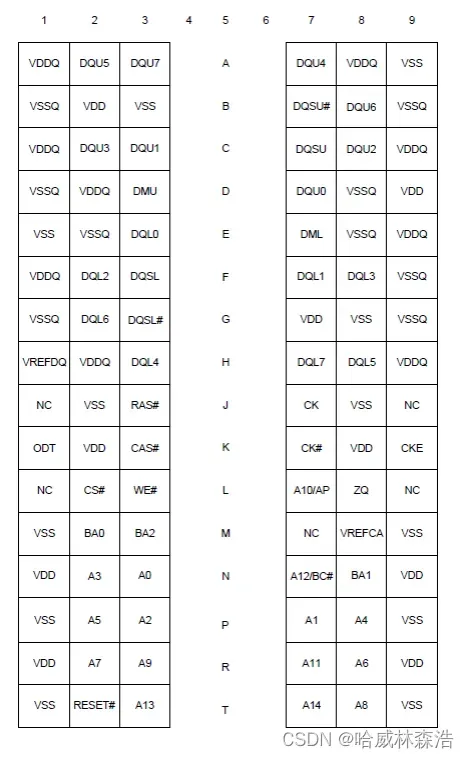

2 DDR3管脚介绍

DDR3管脚根据不同的功能可以分为:数据组、地址组、控制组和电源组。如图上所示,共96个管脚。

2.1数据组

DQ[15:0]:双向信号,16位数据总线; DQS /DQS: 数据选通,用于数据同步,读时是输出,边缘与读出的数据对齐。写时是输入。中心与写数据对齐。 DM:输入数据掩码。

2.2地址组

BA0~BA2:Bank地址选通; A0~A14:地址线;

2.3控制组

CK,/CK:差分时钟输入; CKE:时钟使能信号; /CS:片选信号; /RAS:行地址选通信号; /CAS:列地址选通信号; /WE:读使能信号; ODT:片上终端使能信号。DDR3芯片数据组是有片上端接的,无需外部端接,而控制信号和地址位保证信号完整性需要端接匹配; ZQ:校准管脚,下拉240Ω电阻到VSSQ。

2.4电源组

VDDQ:DQ供电,1.283V到1.45V或者1.5V±0.075V: VSSQ:DQ的地; VDD:电源电压,1.283V到1.45V或者1.5V±0.075V: VSS:电源地; VERFDQ:数据参考电压,电压为VDD/2; VERFCA: 控制、命令和地址参考电压,电压为VDD/2;

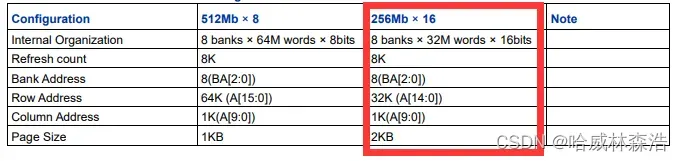

3 DDR3寻址及容量计算

将DDR芯片在逻辑上分为8个Bank,每个Bank可以理解为一个二维数组bool Array。Row/Column就是指示这个二维数组里的坐标。读写某个Bank,需要先指定一个行(Row),再指定一个列(Column)。

如图,Row Address = 15bit,Column Address = 10bit,Bank Address = 3bit,总的存储单元:2^15×2^10×2^3=2^28=256M,总的容量为:256M×16bit = 512MB(4Gbit)。

4 DDR3引脚分配

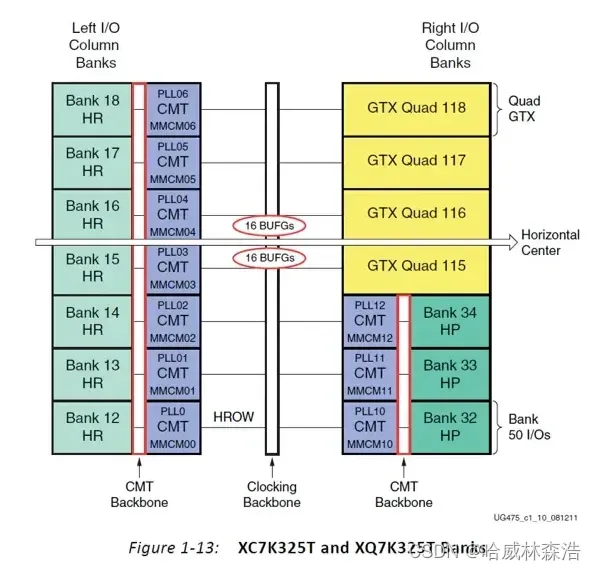

4.1 7系列FPGA引脚划分

7系列的FPGA开始才有HP BANK和HR BANK,UltraScale FPGA有HP BANK、HR BANK和HD BANK,但并不是一个FPGA中会同时包含HP/HR/HDBANK。

HP:High Performance,应用于高速场景,比如DDR或其他高速差分线(不是GTX)

HR:High Range,应用于宽范围I/0,最高能够支持到3.3V的电压。

HD:High Density,应用于低速I/O的场景,最高速率限制在250M以内,最高电压也是支持到3.3V。

如图,DDR的引脚分配一般在HPBank上,也就是Bank32,33,34.

4.1.1 用户Bank

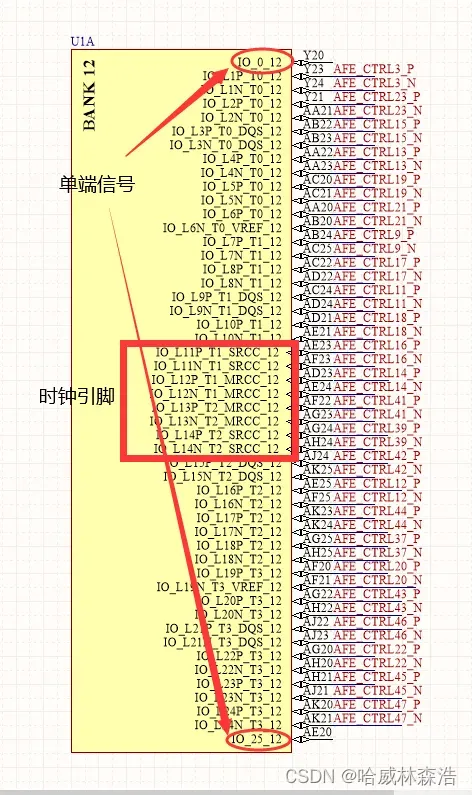

FPGA的管脚按照Bank进行划分,每个Bank独立供电,以使FPGA I/O适应不同电压标准,增强I/O设计的灵活性。每个用户Bank包括50个I/O管脚,或者说24对差分对管脚,顶端和底端各一个单端管脚。

在上图中,红色圈住的是两个单端信号蓝色圈住的是时钟管脚,在不作为时钟输入时可以当作普通I/O使用。

4.2 DDR3引脚分配原则

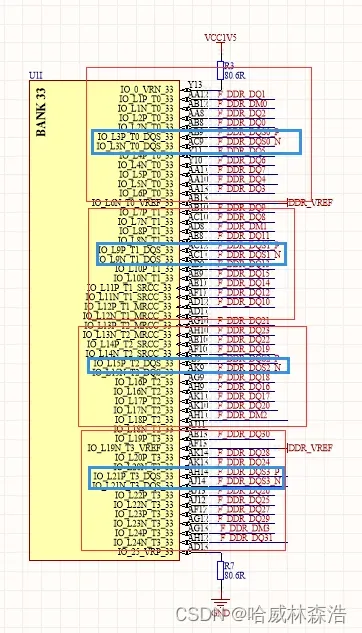

1.FPGA的一个Bank可以放置4个Group的DDR3信号。 2.每个Group包含1对DQS差分信号,8个数据信号,1个DM信号。其中DQS的位置是固定的,不能随意接,数据信号DQ和DM在组内可以互换,注意要按组摆放。 3.时钟信号必须放置在同一差分对上。

如图,T0,T1,T2,T3为Bank33的4个组,分别用红色框圈了出来,蓝色框圈的为DQS信号,每一组的DQS都在固定位置。一个MIG控制器最多支持的数据位宽为72bit,这些数据分布在3个Bank上。其中地址、控制、时钟信号必须在中间Bank。比如使用7K325T的Bank32,33,34,地址控制、时钟信号必须放置在Bank33.

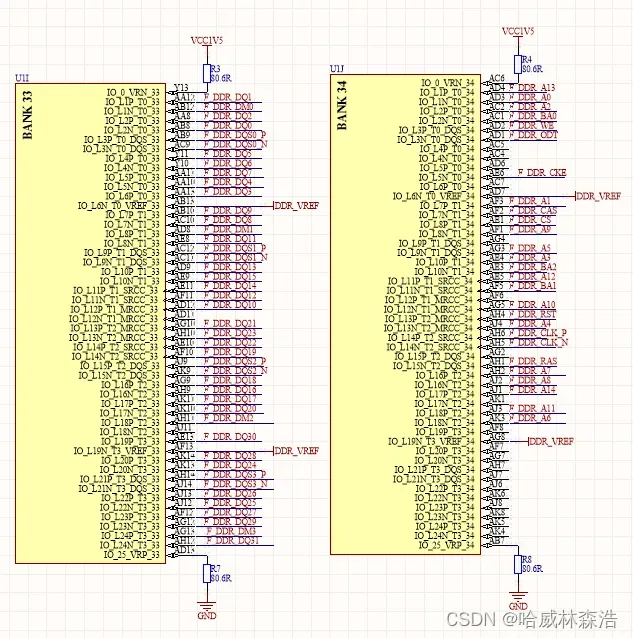

本项目的数据位宽为32bit,故选用了2个Bank,分别是33,34。他的引脚分配如上图所示。

版权声明:本文为博主作者:哈威林森浩原创文章,版权归属原作者,如果侵权,请联系我们删除!

原文链接:https://blog.csdn.net/m0_51679724/article/details/135123993